# An adaptable different-levels cascaded h-bridge inverter analysis for PV grid-connected systems

Adnan Hussein Ali, Hassan Salman Hamad, Ali Abdulwahhab Abdulrazzaq Middle Technical University, Technical Instructors Training Institute, Iraq

| Article Info                                                                                              | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Article history:                                                                                          | Multi-level inverters (MLIs), have gained popularity in the last few years as a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Received Jun 30, 2018<br>Revised Aug 21, 2018<br>Accepted Dec 11, 2018                                    | result of their low total harmonic distortions (THD) as well as their output<br>waveform which is of high quality. The converter which considers more<br>appropriate for applications of photovoltaic (PV)_beyond the varying MLIs<br>arrangements_is the Cascaded H-Bridge-(CHB) (MLI), meanwhile each PV<br>panel may be served as an independent DC supply for any CHB unit.                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Keywords:                                                                                                 | Through the use of MATLAB/Simulink, the efficiency of symmetrical single<br>phase MLI in terms of the number of switches, harmonic content in addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Cascaded h-bridge chb<br>Multi-level inverter mli<br>Photovoltaic PV<br>Total harmonic distortions thd    | to the stresses of voltage through the_switches that exist at photovoltaic cell<br>by means of input source is enhanced; varying parameters like output<br>current, voltage and power, and THD at 5-level 7-level and 9-level Cascaded<br>MLI are observed. In this paper, attention is paid to a multi-level topologies<br>which is flexible and based on cascaded MLI intended for PV grids<br>connected system. An observation of the output voltage becomes closer to<br>the sine wave as the levels increase, while the increase in the levels of<br>Cascaded Multilevel Inverter causes the total harmonic distortion to<br>decrease. |  |  |  |  |  |  |  |

|                                                                                                           | Copyright © 2019 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Corresponding Author:                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Adnan Hussein Ali,<br>Middle Technical University,<br>Technical Instructors Training Ins<br>Baghdad, Iraq | titute,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

Email: aaddnnaann63@yahoo.com

#### 1. INTRODUCTION

Currently, an interest in generating power electricity from renewable energy has increased with solar energy considering the best areas of interest. There are many advantages attached to the use of PV systems which are basically distribution generated units; these advantages include, little maintenance, no pollution, no noise and no fuel cost [1]. One of the sources of energy which is rapidly growing globally is solar photovoltaic panels, especially in grid-connected applications.

In the last few decades, a wider application use of renewable energy such as PV system had been recorded, as it is abundantly and freely available in the entire earth. Engineers have focused on designing and controlling an inverter which is appropriate for photovoltaic applications using this PV energy that is available in abundance. Since the 1960's multilevel inverters have been a research area which has attracted the interest of many [2]. In the literature, various topologies such as diode clamped, and flying capacitor in addition to the cascaded H - Bridge are exist [3]. For every topology, there are advantages and limitations. For instance, the rejection of the flying capacitor came as a result of uneven capacitors' charging [4]. In the same vein, owing to the disparate losses noted at semiconductor devices besides the need for the large element number for a greater amount of the output levels, the significance of the clamped diode topology was lost. The topology of\_conventional CH-Bridge gained importance as a result of these limitations and other limitations found in other topologies; this made the conventional CH-Bridge rises first in the market [5].

Among the different conventional topology for ML inverters, the topology of Cascaded H-Bridge be regarded as the leading in terms of the design simplicity, modular form, packaging, troubleshooting and great power possibilities. Nonetheless, in the cascaded H-Bridge, there is an increase in cost and larger system losses due to the large switch number needed here. Therefore, while modifying the topology of cascaded, it must be done in such a way that the quantity of controlled switches is reduced without the waveform output or a voltage level number being affected.

The design of a multi-level inverter that be present widely referring to as conventional CH bridge multi-level inverter, can be done using cascading H-bridge unit cells [6]. Through the use of one, two, or more unit cells, which were needed for cascading can be used in obtaining the output with 3, 5, 7 and 9 levels respectively. Below is a calculation of the bridge number (B) required for cascading so as to create the output level number (L):

$$B = \frac{L-1}{2} \tag{1}$$

Where the output level number is denoted by L which can be 3, 5, 7, 9, 11, 13, n. Similarly, "N" which refers to the essential number of switches of the transistor may be established at:

N=4\*B (2)

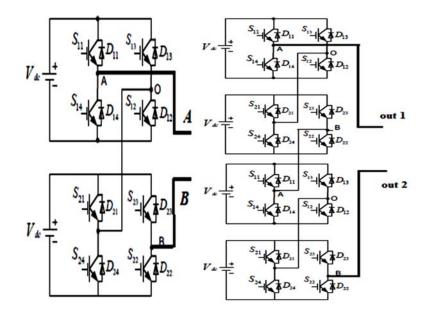

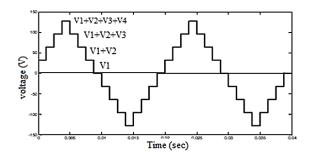

Figure 1 illustrates a five level and n-level inverter alongside its mechanism for switching. The CH-Bridge MLIs can basically be designated as a sum of the classic two-level bridge, with AC terminals that are sequentially linked for the purpose of synthesizing the output waveforms. The symmetrical 9-level inverter's power circuit that comprises four cells of CHB is illustrated in Figure 2. Many stand-alone DC sources that can be gotten from fuel cells, batteries or solar cells are required by the CHB inverter. It is possible for three various voltage output steps, 0 as a reference, (+Vdc), and (-Vdc) to be generated with combining any of the four switches of each cell, as shown in Table 1 for Classic H-Bridge MLI. The total number of the individual converter outputs can be used in deriving the AC output. Using an n=2N+1, the voltage level's number in output phase can be defined, where a number of DC sources is denoted by N. For example, with nine levels, there is a fluctuation of the output voltage from (-4Vdc) to (+4Vdc).

Figure 1. (a) Five-level (b) n-level Inverter

Figure 2. Power circuit for 9-level

| Time          |    | e Half Cycle |            |         |    |         |        |         |

|---------------|----|--------------|------------|---------|----|---------|--------|---------|

| Outputs       | V1 | (V1+V2)      | (V1+V2+V3) | (V1+V2  | V1 | (V1+V2) | (V1+V2 | (V1+V2+ |

| -             |    |              |            | +V3+V4) |    |         | +V3)   | V3+V4)  |

| Bridge A SA 1 | 1  | 1            | 1          | 1       | 1  | 1       | 1      | 1       |

| SA 4          | 1  | 1            | 1          | 1       | 1  | 1       | 1      | 1       |

| Bridge B Sb 1 | 0  | 1            | 1          | 1       | 0  | 1       | 1      | 1       |

| Sb 4          | 1  | 1            | 1          | 1       | 1  | 1       | 1      | 1       |

| Bridge C Sc 1 | 0  | 0            | 1          | 1       | 0  | 0       | 1      | 1       |

| Sc 4          | 1  | 1            | 1          | 1       | 1  | 1       | 1      | 1       |

| Bridge D Sd 1 | 0  | 0            | 0          | 1       | 0  | 0       | 0      | 1       |

| Sd 4          | 1  | 1            | 1          | 1       | 1  | 1       | 1      | 1       |

| Inversion Sp1 | 1  | 1            | 1          | 1       | 0  | 0       | 0      | 0       |

| Bridge Sp2    | 0  | 0            | 0          | 0       | 1  | 1       | 1      | 1       |

| Sp3           | 0  | 0            | 0          | 0       | 1  | 1       | 1      | 1       |

| Sp4           | 1  | 1            | 1          | 1       | 0  | 0       | 0      | 0       |

Table 1. Switching mechanism for classic h-bridge MLI

Compared to flying capacitor or diode clamped MLI topologies, the cascaded H bridge MLI are simpler due to some advantages which it possess like switching redundancy, automatic voltage distribution, smaller dv/dt stress, absence of high-rated capacitors and diodes as well as the need for minimum number of components [7]. The main focus of this manuscript is to investigate the single phase CHB performances of MLI which an input sources started from level 5 to 9 are a photovoltaic cell. It presents a symmetric type inverter with a reduction in switch amount. It consists of two voltage sources and four switches for each cell and generates 5, 7, and 9 levels output waveform during symmetric operation. More so, it concentrates on technologies of inverter to connect photovoltaic panels to a single-phase grid. A related works are explained in Section II. The suggested topology for different methods of calculating the switching are offered in Section V.

## 2. RELATED WORKS

Based on the review of literature in the previous pages, it is evident that efforts are made by many researchers to propose novel inverter topologies or to modify the old ones. The purpose of doing this is to improve the quality of energy that is available at the terminals of inverters. Due to the ability of cascaded H-bridge multi-level inverter to handle high-power as well as its reliability, which is as a result of its modular topology, it has been regarded as one of the best available multilevel inverter topologies. Due to this, is considered as a more capable option which can be extended to allow grid connection that is transformer-less.

Rodriguez et al. [8], have provided a description of the most significant methods of control and modulation which he designed for a family of converters which include space-vector modulation, multi-level selective harmonics elimination and multilevel sinusoidal pulse width modulation (SPWMs). The PWM regenerative rectifiers were introduced by Rodriguez et al. [9] in which they were able to improve the power factor as well as reduce input harmonics. In time past, the application of multilevel active rectifiers was basically made in high power industrial application, high voltage applications, owing to the capability of the applied voltage dispensing through many cascaded power devices, therefore addressing the issue of their limitation voltage as well as enabling the exclusion of out-put system transformers of medium toward high voltages. The performance of the multilevel active rectifiers is better than that of the two-levels PWMs inverters related to total harmonics distortion, and with-out using passive filters which are expensive, bulky and deceptive; this is because their output voltage is in the form of modulated staircase.

In 2003, Alonso O. et al. [10] presented a novel scheme of controlling and proportionate PWM for the CH-bridge multilevel inverter used for grid connected photovoltaic system. Through by utilizing this controlling, various power levels are provided by each H-bridge module, thereby allowing each module to independently track the maximum power point of corresponding PVA. Furthermore, multilevel PWM inverters, which are appropriate for using in independent PV grid-connected power inverters for PV units were developed by Kang et al. [11]. A strategy for switching a five level CHB MLI essential frequency to PV systems that are independent was proposed by Ozdemir et al. [12] through the selection of the switching angles in a way that it can eliminate the harmonics with lower order.

In addition to the advantage of having the capability for maximizing the power acquired from PVAs, a ML inverter is also capable of decreasing the stress of voltage device as well as to generate a lower output, that is a voltage harmonic distortion more efficient. In the area of renewable energies Josh et al. [13] had suggested MLI, which is capable of reducing the dimensions of output filter as well as influencing the perturbations that occur as a result of the darkening of cloud of variation in seasons, while a modified phase disposition PWM was proposed by Mei et al. [14] for units of MLI which was employed at PV grid connected for the purpose of achieving balance in the dynamic capacitor voltage without requiring additional compensation signal. A distinct DC source is needed by the Cascade H-bridge MLI, besides it limits the performance this MLI when it is available [15]. However, in the case of PV systems, it is a striking characteristic as it enhances the assembling of solar cells in a number of independent generators. Various PWM methods such as optimized stepped waveform (OHSW) and selective harmonics elimination PWM are supported by the CHB-MLI [16].

## 3. SUGGESTED TOPOLOGY

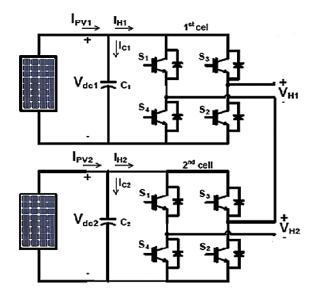

The suggested topology accomplished by reducing the number of controlling switches is described here. A review of past studies, shows that the focus of previous researchers has been dealing with a reduction of size and components of MLI, with the purpose of reducing switches through the use of Inversion Bridge. The currently proposed design focuses on minimum number of switches which have some disadvantages related to these topologies. One of such limitations is using a bidirectional switch which incurs extra cost asides the absence of even sources of voltage. More so, the proposed topology offers a better and simpler modular form in comparison to the symmetrical multilevel inverter; the topology also allows transistor switches to connect with each other, and it also provides parallel diodes as illustrated in Figure 3. The inverter representation diagram of the CH-bridge structure of the grid connection PV systems appears in Figure 3. A topology of the cascaded MLI comprises of *n*-connected H-bridge inverters serially and each DC link can be fed with a small chain of PV panels [17].

Figure 3. CHB circuit diagram MLI

#### **B** 835

## 4. DESIGN SIMULATION, ANALYSIS, AND RESULTS

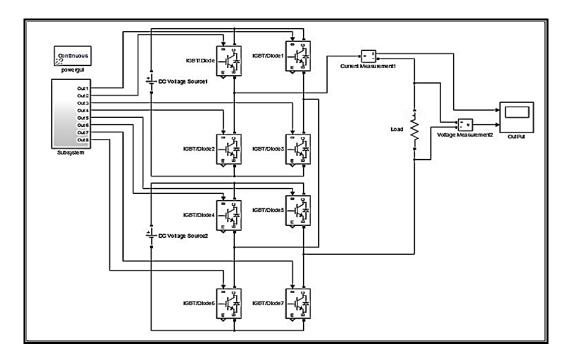

The cascaded H-Bridge MLI circuit which can be designed using MATLAB/Simulink is discussed in this section. More so, the figures for all levels illustrate the simulated output voltage, THD and current analysis as well as the output voltage with equal step waveform for eleven-level cascaded H-Bridge inverter. 5, 7 and 9-Levels switching of the CHB MLI as shown in Table 2.

| Table 2: 5. | 7 and 9-Levels switching of the CHB | MLI |

|-------------|-------------------------------------|-----|

|             |                                     |     |

|         | 5 levels |    |            |            |    | 7 levels |     |     |     | 9 levels |     |     |  |  |

|---------|----------|----|------------|------------|----|----------|-----|-----|-----|----------|-----|-----|--|--|

| V (OUT) | S5       | S6 | <b>S</b> 7 | <b>S</b> 8 | S9 | S10      | S11 | S12 | S13 | S14      | S15 | S16 |  |  |

| 4VP     | 1        | 0  | 0          | 1          | 1  | 0        | 0   | 1   | 1   | 0        | 0   | 1   |  |  |

| 3VP     | 1        | 0  | 0          | 1          | 1  | 0        | 0   | 1   | 1   | 1        | 0   | 0   |  |  |

| 2VP     | 1        | 0  | 0          | 1          | 1  | 1        | 0   | 0   | 1   | 1        | 0   | 0   |  |  |

| VP      | 1        | 1  | 0          | 0          | 1  | 1        | 0   | 0   | 1   | 1        | 0   | 0   |  |  |

| 0 V     | 1        | 1  | 0          | 0          | 1  | 1        | 0   | 0   | 1   | 1        | 0   | 0   |  |  |

| -VP     | 0        | 0  | 1          | 1          | 0  | 0        | 1   | 1   | 0   | 0        | 1   | 1   |  |  |

| -2VP    | 0        | 1  | 1          | 0          | 0  | 0        | 1   | 1   | 0   | 0        | 1   | 1   |  |  |

| -3VP    | 0        | 1  | 1          | 0          | 0  | 1        | 1   | 0   | 0   | 0        | 1   | 1   |  |  |

| -4VP    | 0        | 1  | 1          | 0          | 0  | 1        | 1   | 0   | 0   | 1        | 1   | 0   |  |  |

## 4.1. Five-level inverter

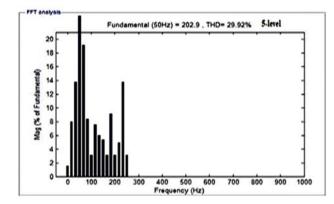

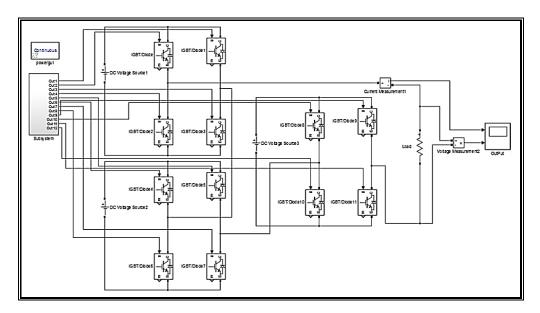

Figure 4(a) illustrates the model of simulation for the Five-level cascade inverter circuit content 8 IGBT grid connected PV system. In order for IGBT's to inverts DC to AC, 8 pulses are required. Figure 4(b) represents the output signal THD, the 8 PWM signal for IGBT is explained in Figure 4(c) and Figure 4(d) illustrates the output voltage and Current.

The simulation model comprises two H-bridges which nominal DC voltage supposed to be 65 V, in addition to the PWM inverter which control the system connected to the grid, also, a multi-level stepped output voltage can be achieved and a harmonics could be reduced. A PWM generator block exists that contain parameters like amplitude, phase delay, and pulse width period from which a shape of the output can be determined.

Figure 4(a). 5-levels CHB Inverter MATLAB model circuit

Figure 4(b). Analysis of FFT CH-Bridge MLI

Figure 4(c). Gating pulses generated of PWM 5-levels CHB

Figure 4(d). Voltage and current output phase

Thus, the inverter efficiency could be increased, so the inverter needs to perform with reliability and proficiently for supplying a wide-ranging of AC loads **by a** required power quality and voltage which is necessary for efficient load as well as system performances. Many system advantages like high-power, low harmonic distortions, capacity of high-voltage in addition to low switching losses. A 5-levels output voltage and current are shown. The output 5-level inverter, central frequency is 50 Hz.

## 4.2. Seven-level Inverter

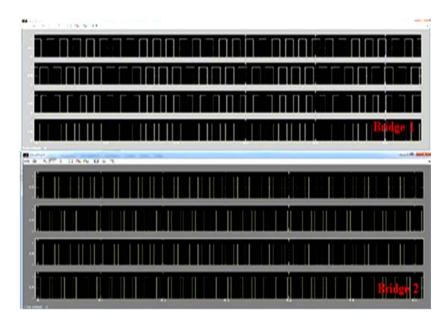

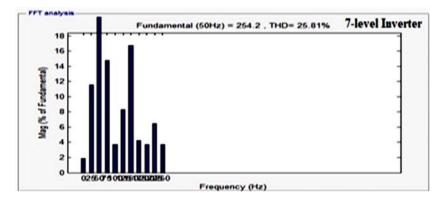

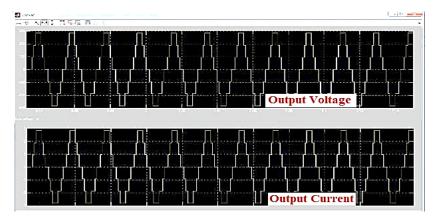

A Seven-levels CHB inverter circuit content 12 switches of IGBT, which can be displayed in the Figure 5(a). An IGBT's need 8 pulses for inverting DC signal to the AC. Figure 5(b) represents the THD for the output voltage signal, Figure 5(c) explains the 8 PWM signal for IGBT and finally Figure 5(d) shows the output voltage and Current.

Figure 5(a). 7-levels CHB Inverter MATLAB model circuit

Figure 5(b). Analysis of FFT CH-Bridge MLI

| • · · ·      |               |         |     |        |       |     |     |       |            |             |           |

|--------------|---------------|---------|-----|--------|-------|-----|-----|-------|------------|-------------|-----------|

| İTTT         |               |         |     |        |       |     |     |       |            | ΙΠÌ         |           |

| i a la       |               |         |     |        |       |     |     |       |            |             |           |

| HIII         |               |         | 111 |        |       | 11  |     |       |            |             |           |

|              | - n -         | ri -    |     | ΠΓ     | Bridg | e 1 | ППП | רור   | n n -      |             |           |

|              |               | 1/654 C |     | ADDEED |       | 1   |     |       | (1994) - A | er (displa) | Acres 100 |

|              | <u>الم ال</u> |         | ي ا |        |       | الص |     | التال |            |             | 111       |

|              |               |         |     |        |       |     |     |       |            |             |           |

| -            |               |         |     |        |       |     |     |       | H.II       |             | 1 11      |

|              |               | TÎ [    |     | 1.0    | Bridg | e 2 |     | 1.11  |            |             |           |

| and a sector |               | a 1.    |     |        |       |     |     |       |            |             | Locia     |

|              |               |         |     | 1      | ا ک ک |     |     |       |            |             |           |

| -            |               |         |     | 1      |       |     |     |       | 1          | 1           |           |

|              |               |         |     | 1      |       |     |     |       | 11         |             |           |

| IT I         | 1             | T 1     | n r | ГГ     | Bridg |     | r n | n n n | 1          |             | 1         |

Figure 5(c). Gating pulses generated of PWM 7-levels CHB

Figure 5(d). Voltage and current output phase

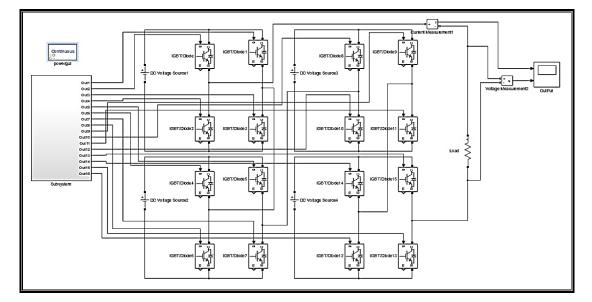

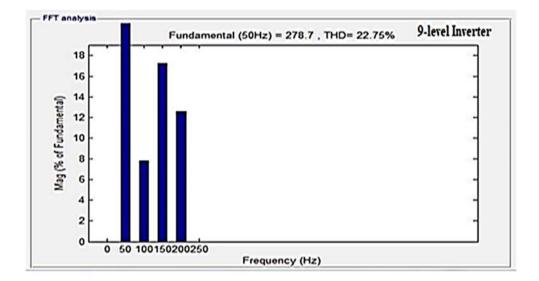

#### 4.3. Nine-level inverter

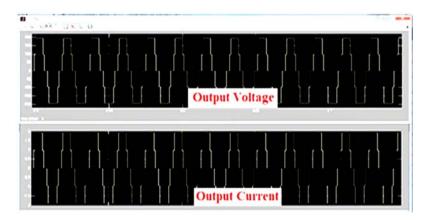

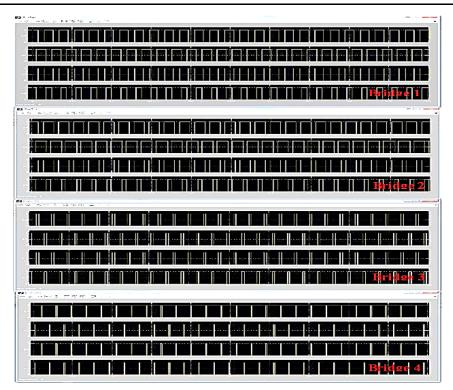

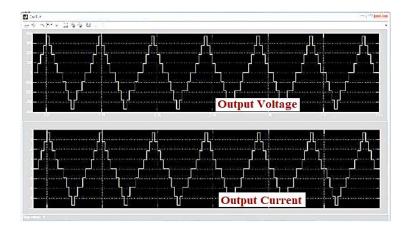

A circuit of nine-levels CHB inverter content 16 switches of IGBT, which can be presented in the Figure 6(a). An IGBT's need 16 pulses in inverting DC signal to the AC. Figure 6(b) represents the THD for the output voltage signal, Figure 6(c) explains the 16 PWM signal for IGBT and finally Figure 6(d) shows the output voltage and Current.

| Time          |    | Positiv | e Half Cycle |                 |    | Negative Half Cycle |              |                 |  |  |

|---------------|----|---------|--------------|-----------------|----|---------------------|--------------|-----------------|--|--|

| Output        | V1 | V1+V2   | V1+V2+V3     | V1+V2<br>+V3+V4 | V1 | V1+V2               | V1+V2+<br>V3 | V1+V2+V<br>3+V4 |  |  |

| Bridge A Sa 1 | 1  | 1       | 1            | 1               | 1  | 1                   | 1            | 1               |  |  |

| Sa 4          | 1  | 1       | 1            | 1               | 1  | 1                   | 1            | 1               |  |  |

| Bridge B Sb 1 | 0  | 1       | 1            | 1               | 0  | 1                   | 1            | 1               |  |  |

| Sb 4          | 1  | 1       | 1            | 1               | 1  | 1                   | 1            | 1               |  |  |

| Bridge C Sc 1 | 0  | 0       | 1            | 1               | 0  | 0                   | 1            | 1               |  |  |

| Sc 4          | 1  | 1       | 1            | 1               | 1  | 1                   | 1            | 1               |  |  |

| Bridge D Sd 1 | 0  | 0       | 0            | 1               | 0  | 0                   | 0            | 1               |  |  |

| Sd 4          | 1  | 1       | 1            | 1               | 1  | 1                   | 1            | 1               |  |  |

| Inversion Sp1 | 1  | 1       | 1            | 1               | 0  | 0                   | 0            | 0               |  |  |

| Bridge Sp2    | 0  | 0       | 0            | 0               | 1  | 1                   | 1            | 1               |  |  |

| Sp3           | 0  | 0       | 0            | 0               | 1  | 1                   | 1            | 1               |  |  |

| Sp4           | 1  | 1       | 1            | 1               | 0  | 0                   | 0            | 0               |  |  |

Int J Pow Elec & Dri Syst, Vol. 10, No. 2, June 2019: 831 – 841

Figure 6(a). 9-Levels CHB Inverter MATLAB model circuit

Figure 6(b). Analysis of FFT CH-Bridge MLI

Figure 6(c). Gating pulses generated of PWM 9-levels CHB

Figure 6(d). Voltage and current output phase

The simulation MATLAB have been presented to numerous CH-bridge topologies of MLIs focuses on 5-levels, 7-levels and 9-levels. A comparison of these topologies with detailed has been offered in this paper and concentrated on main parameters such as switching power devices used number, Total Harmonic Distortion, the stresses over current and voltage, and gating Pulses generated of PWM.

# 5. CONCLUSION

The simulation of five levels, seven levels, and nine levels, inverters were executed in MATLAB/SIMILINK, based on applying straightforward control strategy of controlling the IGBT switches with suitable angles at proper delays. A perfect specification of the CHB MLI are achieved like high

**D** 841

conversion efficiency in addition to easily interface with sources of renewable energy. An MLI realizes ratings of high power and get better performances of the total harmonic system. This harmonic distortion was studied for each specific level so as to have a comparison for resistive load. Depending on simulation of different levels of MLI, it is clear found that a considerable THD amount could be decreased with an increasing level number, which confirms the proposition of the control strategy and thus it eliminates the need for a filter.

#### REFERENCES

- Thiyagarajan V, Somasundaram P, "A New Seven Level Symmetrical Inverter with Reduced Switch Count", International Journal of Power Electronics and Drive System (IJPEDS) Vol. 9, No. 2, pp. 921- 925, June 2018.

- [2] V. Thiyagarajan and P. Somasundaram, "Modified Nine Level Inverter with Reduced Number of Switches", International Journal of Control Theory and Applications, Vol.10, No. 2, pp 217-225, 2017.

- [3] M. Jayabalan, B. Jeevarathinam and T. Sandirasegarane, "Reduced switch count pulse width modulated multilevel inverter," in *IET Power Electronics*, vol. 10, no. 1, pp. 10-17, 2017.

- [4] K. Ramani, M.A. Sathik, S Sivakumar, " A New Symmetric Multilevel Inverter Topology Using Single and Double Source Sub-Multilevel Inverters", *Journal of Power Electronics*, Volume 15, Issue 1, pp. 96-105, 2015.

- [5] Muhammad T, et al, "Cascaded Symmetric Multilevel Inverter with Reduced Number of Controlled Switches", International Journal of Power Electronics and Drive System (IJPEDS), Vol. 8, No. 2, pp. 795-803, June 2017.

- [6] Mohannad J. Mnati, Adnan H. Ali, Dimitar V. Bozalakov, Shahad Al-yousif, Alex Van den Bossche, "Design and Implementation of a Gate Driver Circuit for Three-Phase Grid Tide Photovoltaic Inverter Application", 7th International Conference on Renewable Energy Research and Applications (ICRERA), Paris, 14-17 Oct. 2018.

- [7] Zulkefle A, et al," Modeling and Simulation of Nine-Level Cascaded H-Bridge Multilevel Inverter", *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)* Vol. 11, No. 2, pp. 696-703, August 2018.

- [8] Rodriguez JR, Lai J-S, Peng FZ. "Multilevel inverters: A survey of topologies, control, and applications". IEEE Transactions on Industrial Electronics. Vol 49 (4): 724–38, 2002.

- [9] Adnan H. Ali, Hassan S. Hamad, Ali A. Abdulrazzaq,"Performance Investigation of Grid Connected Photovoltaic system Modelling Based on MATLAB Simulation", *International Journal of Electrical and Computer Engineering* (*IJECE*), Vol. 8, No. 6, pp. 4847~4854, December 2018.

- [10] .Alonso O, Sanchis P, Gubia E, Marroyo L. "Cascaded H-bridge multilevel converter for grid connected photovoltaic generators with independent maximum power point tracking of each solar array". In *Proceedings of* the 34th IEEE power electronics specialists conference, Acapulco, Mexico, vol. 2, pp. 731–735, 2003.

- [11] Kang FS, Park SJ, Cho SE, Kim CU, Ise T. "Multilevel PWM inverters suitable for the use of stand-alone photovoltaic power grid-connected inverters for photovoltaic module". *IEEE Transactions on Energy Conversion*. Vol. 20 (4): pp. 906–15, 2005.

- [12] Ozdemir E, Ozdemir S, Tolbert LM. "Fundamental frequency- modulated six-level diode-clamped multilevel inverter for three-phase stand-alone photovoltaic system". *IEEE Transactions on Industrial Electronics*; vol 56 (11): pp. 4407–15, 2009.

- [13] Ali A. Abdulrazzaq, Adnan H. Ali, "Efficiency Performances of Two MPPT Algorithms for PV System With Different Solar Panels Irradiances", *International Journal of Power Electronics and Drive System (IJPEDS)*, Vol. 9, No. 4, pp. 1755~1764, December 2018.

- [14] Mei J, Xiao B, Shen K, Tolbert LM, Zheng JY. "Modular multilevel inverter with new modulation method and its application to photovoltaic grid connected generator". *IEEE Transactions on Power Electronics*, vol 28 (11): 5063– 73, 2013.

- [15] Bo Sun, Wu F, Savaghebi M, Guerrero J," A Flexible Five-level Cascaded H-bridge Inverter for Photovoltaic Gridconnected Systems", In Proceedings of 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia): Green World with Power Electronics (pp. 2369-2375). [7168101] IEEE Press, 2015.

- [16] Xin-Jian Cai, Zhen-Xing Wu, Quan-Feng Li, and Shu-Xiu Wang," Phase-Shifted Carrier Pulse Width Modulation Based on Particle Swarm Optimization for Cascaded H-bridge Multilevel Inverters", *Energies* 2015, 8, 9670-9687.

- [17] Adnan H. Ali, Ali A. Abdulrazzaq," Evaluating the performance and efficiency of MPPT algorithm for PV systems", *International Journal of Engineering & Technology*, Vol.7, (4), pp- 2122-2126, 2018.