# Novel AZSPWM Algorithms based VCIMD for Reduced CMV Variations

J. Amarnath\*, A. Kailasa Rao\*\*, K. Satyanarayana\*\*

\* Departement of Electrical and Electronics Engineering, JNTUH, Kukatpally, Hyderabad \*\* Departement of Electrical and Electronics Engineering, Pragati Engineering College, Surampalem

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Novel AZSPWM algorithms based on the concept of imaginary switching                                                                                                                                                                                                                                                                                                                             |  |  |  |

| times (IST) are presented in this paper for vector controlled induction motor<br>drive to reduce the common mode voltage (CMV) variations. The propose<br>algorithms did not use the information of angle and sector and hence reduce<br>the complexity involved in the conventional space vector PWM (CSVPWM<br>approach. The proposed AZSPWM algorithms did not use zero voltage              |  |  |  |

| vectors and involves utilizing the two adjacent voltage vectors along with<br>two opposing active voltage vectors with equal duty cycle to provide                                                                                                                                                                                                                                              |  |  |  |

| cancellation and create an effective zero state. Moreover, these algorithms<br>are developed based on the concept of imaginary switching times, the<br>computational burden involved in the conventional algorithms can be<br>decreased. To verify these algorithms, numerical simulation studies have<br>been carried out and results are presented and compared with the CSVPWM<br>algorithm. |  |  |  |

| Copyright © 2013 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

Prof.K.Satyanarayana, Departement of Electrical and Electronics Engineering, Pragati Engineering College, 1-378, ADB Road, Surampalem, East Godavari District, Andhra Pradesh, India , 533437. Email: snkola@gmail.com

# 1. INTRODUCTION

Nowadays the vector control methods are widely used for the control of induction motor drives in high-performance applications. With the vector control method [1], the decoupling control of torque and flux of the induction motor can be obtained, and the induction motor can be controlled as a separately excited dc motor. However, the classical vector control algorithm uses hysteresis controllers for the generation of gating signals to the voltage source inverter (VSI), which results in variable switching frequency operation. To achieve constant switching frequency operation of the inverter, the conventional space vector PWM (CSVPWM) algorithm [2] has been used for vector controlled induction motor drive. The CSVPWM algorithm distributes the zero voltage vector time equally among the two zero voltage vectors. Due to the presence of zero voltage vectors the CSVPWM algorithm results in large common-mode voltage (CMV) variations. In the induction motor drives, the poor CMV characteristics lead to prohibitive amount of common-mode current (CMC). In induction motor drive applications, this may lead to motor bearing failures, electromagnetic interference (EMI) noise, or interference with other electronic equipment in the vicinity [3]-[4]. Such problems have increased recently due to increasing PWM frequencies and faster switching times. The filters can be utilized to suppress the effect of the CMV from the source. However, these methods involve additional hardware, and thus, they significantly increase the drive cost and complexity. An alternative approach is to modify the pulse pattern of the standard PWM algorithm such that the CMV is substantially reduced from its source and its effects are mitigated at no cost [5]-[9]. In the literature, several PWM algorithms have been developed for reduced CMV and analyzed in detail.

However, the conventional space vector approach requires angle and sector information for the calculation of gating times, which increases the complexity of the algorithm. to reduce the complexity involved in the conventional approach, a novel approach is presented in [10] by using the concept of offset time. Similarly, another simplified approach is presented in [11]-[12] by using the concept of imaginary switching times.

This paper presents space vector based Novel AZSPWM algorithms for reduced CMV in vector controlled induction motor drives by using the concept of imaginary switching times.

### 2. COMMON MODE VOLTAGE

The common mode voltage is the potential of the star point of the load with respect to the center of the dc bus.

A set of phase voltage equations can be written as given in (1)

$$V_{an} = V_{so} - V_{ao}$$

$$V_{bn} = V_{so} - V_{bo}$$

$$V_{cn} = V_{so} - V_{co}$$

(1)

where  $V_{ao}$ ,  $V_{bo}$ ,  $V_{co}$  are inverter pole voltages and  $V_{so}$  is common mode voltage. Adding the set of equations of (1) and since  $V_{an} + V_{bn} + V_{cn} = 0$ , the common mode voltage in the motor is given by

$$V_{com} = V_{so} = \frac{V_{ao} + V_{bo} + V_{co}}{3}$$

(2)

Hence, if the drive is fed by balanced three phase supply, the common mode voltage is zero. But, the common mode voltage exists inevitably when the drive is fed from an inverter employing PWM technique because the voltage source inverter cannot produce pure sinusoidal voltages and has discrete output voltages.

#### 3. CONVENTIONAL ALGORITHMS

#### **3.1. SVPWM ALGORITHM**

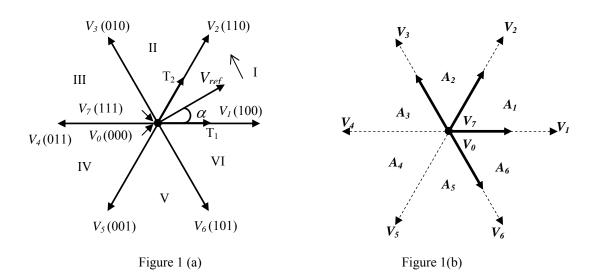

The three-phase, two-level voltage source inverter has eight possible voltage vectors, which can be represented as shown in Figure 1(a). Among these voltage vectors,  $V_1$  to  $V_6$  vectors are known as active voltage vectors or active states and the remaining two vectors are known as zero states or zero voltage vectors. The reference voltage space vector or sample, which is as shown in Figure 1(a) represents the corresponding to the desired value of the fundamental components for the output phase voltages. In the space vector approach this can be constructed in an average sense. The reference voltage vector ( $V_{ref}$ ) is sampled

at equal intervals of time,  $T_s$  referred to as sampling time period. Different voltage vectors that can be produced by the inverter are applied over different time durations with in a sampling time period such that the average vector produced over the sampling time period is equal to the sampled value of the  $V_{ref}$ , both in

terms of magnitude and angle. It has been established that the vectors to be used to generate any sample are the zero voltage vectors and the two active voltage vectors forming the boundary of the sector in which the sample lies. As all six sectors are symmetrical, the discussion is limited to the first sector only.

For the required reference voltage vector, the active and zero voltage vectors times can be calculated as in (3), (4) and (5).

$$T_{1} = \frac{2\sqrt{3}}{\pi} M_{i} \sin(60^{o} - \alpha) T_{s}$$

(3)

$$T_2 = \frac{2\sqrt{3}}{\pi} M_i \sin(\alpha) T_s \tag{4}$$

$$T_z = T_s - T_1 - T_2 \tag{5}$$

where  $M_i$  is the modulation index and defined as in [1]. In the CSVPWM algorithm, the total zero voltage vector time is equally divided between V<sub>0</sub> and V<sub>7</sub> and distributed symmetrically at the start and end of the each sampling time period. Thus, SVPWM uses 0127-7210 in sector-I, 0327-7230 in sector-II and so on.

Figure 1 (a) Possible voltage space vectors and sector definition in CSVPWM algorithm (b) Voltage space vectors and formation of AZSPWM algorithms

# **3.2. AZSPWM ALGORITHM**

In the conventional SVPWM method, two adjacent states with two zero voltage vectors are utilized to program the output voltage. Every  $60^{0}$  degrees the active voltage vectors change, but the zero state locations are retained. In the AZSPWM methods, the choice and the sequence of active voltage vectors are the same as in conventional SVPWM. However, instead of the real zero voltage vectors (V<sub>0</sub> and V<sub>7</sub>), two active opposite voltage vectors with equal duration are utilized. Here, three choices exist. For AZSPWM algorithms, any of the pairs V<sub>1</sub>-V<sub>4</sub>, V<sub>2</sub>-V<sub>5</sub>, or V<sub>3</sub>-V<sub>6</sub> can be utilized. In each PWM method, with a specific performance optimization criterion, the voltage vectors are selected, and their sequences depend on the region of the reference voltage vectors defined in Figure 1(b).

#### 4. PROPOSED AZSPWM SWITCHING SEQUENCES

In this section, the proposed AZSPWM have been developed by using the notion of imaginary switching times (IST). The imaginary switching times are proportional to the instantaneous phase voltages and can be defined as follows:

$$T_{an} = \frac{T_s}{V_{dc}} V_{an}; T_{bn} = \frac{T_s}{V_{dc}} V_{bn}; T_{cn} = \frac{T_s}{V_{dc}} V_{cn}$$

(6)

$V_{an}$ ,  $V_{bn}$  and  $V_{cn}$  are the instantaneous reference phase voltages and  $T_{an}$ ,  $T_{bn}$  and  $T_{cn}$  are the corresponding imaginary switching times. As these times are proportional to the instantaneous voltages, these times could be negative where the voltages are negative. Hence, these times are defined as imaginary switching times. If the reference voltage vector falls in sector-1, the active vector switching times  $T_1$  and  $T_2$ , may be expressed as follows [11]-[12]:

3

$$T_{\max} = Max(T_{an}, T_{bn}, T_{cn}) \tag{7}$$

$$T_{mid} = Mid(T_{an}, T_{bn}, T_{cn}) \tag{8}$$

$$T_{\min} = Min(T_{an}, T_{bn}, T_{cn}) \tag{9}$$

In the CSVPWM algorithm, when the reference voltage vector falls in the first sector, the imaginary switching time which is proportional to the a-phase  $(T_{an})$  has a maximum value, the imaginary switching time which is proportional to the c-phase  $(T_{cn})$  has a minimum value and the imaginary switching time which is proportional to the b-phase  $(T_{bn})$  is neither minimum nor maximum value. Thus, in general to calculate the active vector switching times, the maximum  $(T_{max})$ , middle  $(T_{mid})$  and minimum  $(T_{min})$  values of imaginary switching times are calculated in every sampling time. Then the active vector switching times  $T_1$  and  $T_2$  may be expressed as [11]

$$T_1 = T_{\max} - T_{mid} \ ; T_2 = T_{mid} - T_{\min}$$

(10)

The zero voltage vectors switching time is calculated as

$$T_z = T_s - T_1 - T_2 \tag{11}$$

The CSVPWM algorithm divides the zero state time equally between the two possible zero voltage space vectors. The usage of zero voltage vectors increases the common mode voltage variations [9]. Hence, in order to reduce the common mode voltage variations, the proposed AZSPWM algorithms use two active opposite voltage vectors in place of zero voltage vectors with equal time duration for composing the reference voltage vector. These two active opposite voltage vectors with equal time create effectively a zero voltage vector. The switching sequences of two AZSPWM algorithms, which have considered in this paper, are given in Table 1. In the proposed AZSPWM algorithms, the zero state time is divided equally among the two active voltage vectors in each sector. The utilized voltage vectors and their sequences for the conventional CSVPWM and AZSPWM methods are given in Table 1.

Table 1. Switching sequences of CSVPWM and AZSPWM algorithms in all sectors

| Type of PWM | Sector-1  | Sector – 2 | Sector – 3 | Sector – 4 | Sector – 5 | Sector - 6 |

|-------------|-----------|------------|------------|------------|------------|------------|

| CSVPWM      | 0127-7210 | 0327-7230  | 0347-7430  | 0547-7540  | 0567-7650  | 0167-7610  |

| AZSPWM1     | 3216-6123 | 4321-1234  | 5432-2345  | 6543-3456  | 1654-4561  | 2165-5612  |

| AZSPWM2     | 5122-2215 | 6233-3326  | 1344-4431  | 2455-5542  | 3566-6653  | 4611-1164  |

# 5. NOVEL AZSPWM ALGORITHMS BASED VECTOR CONTROLLED INDUCTION MOTOR DRIVE

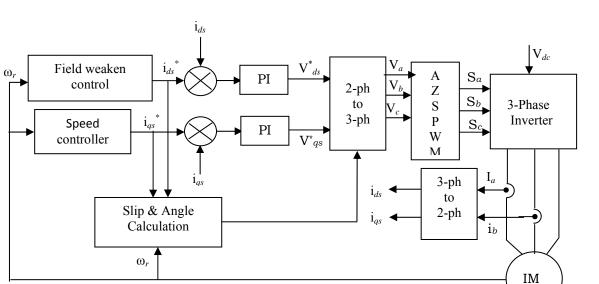

In the vector controlled induction motor drive, a voltage source inverter is supposed to drive the induction motor so that the slip frequency can be changed according to the particular requirement. Assuming the rotor speed is measured, and then the slip speed is derived in the feed-forward manner. For decoupling control, it is desirable that the rotor flux is aligned on to the d-axis of the synchronously rotating reference frame, then  $\lambda_{qr} = 0$  and  $\lambda_{dr} = \lambda_r = L_m i_{ds}$ . The block diagram of proposed vector controlled induction motor drive is as shown in Figure 2.

Figure 2. Block diagram of proposed AZSPWM algorithms based vector controlled induction motor

# 6. SIMULATION RESULTS AND DISCUSSIONS

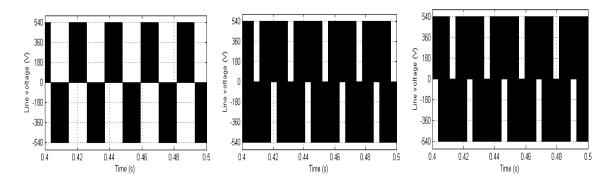

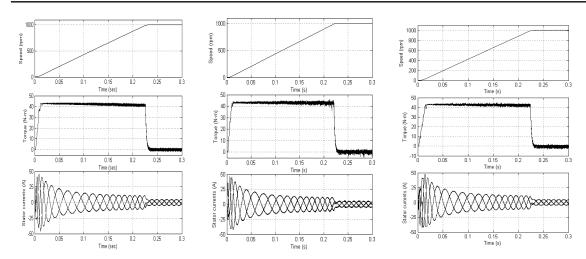

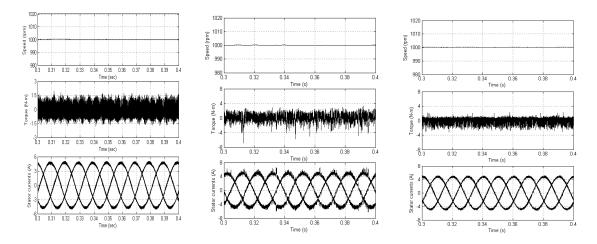

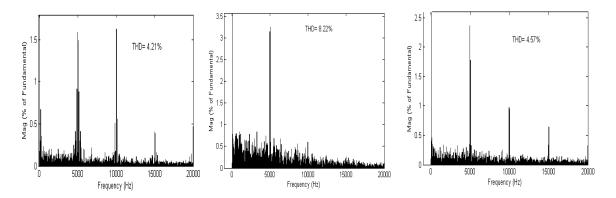

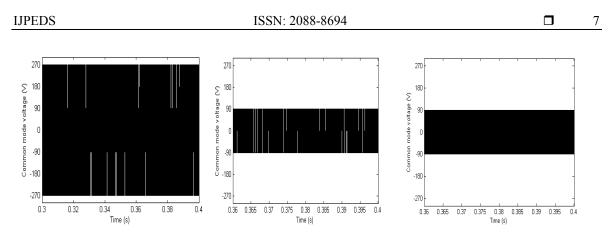

To validate the proposed algorithms, the numerical simulation studies have been carried out using MATLAB. For the simulation studies, the average switching frequency of the inverter is taken as 5 kHz. The induction motor used in this case study is a 4 kW, 400V, 1470 rpm, 4-pole, 50 Hz, 3-phase induction motor having the following parameters:  $R_s$ = 1.57 $\Omega$ ,  $R_r$  = 1.21 $\Omega$ ,  $L_s$  = 0.17H,  $L_r$  = 0.17H,  $L_m$  = 0.165 H and J = 0.089 Kg.m<sup>2</sup>. The steady state simulation results of CSVPWM algorithm and proposed AZSPWM algorithms based vector controlled induction motor drive are shown in from Figure 3 to Figure 7 along with the harmonic spectra of line current and common mode voltage variations.

Figure 3. Line voltages of CSVPWM, AZSPWM1 and AZSPWM2 algorithms based vector controlled induction motor drive respectively

Figure 4. Starting transients of CSVPWM, AZSPWM1 and AZSPWM2 algorithms based vector controlled induction motor drive respectively

Figure 5. Steady state plots of CSVPWM, AZSPWM1 and AZSPWM2 algorithms based vector controlled induction motor drive respectively

Figure 6. Harmonic spectra of line current in CSVPWM, AZSPWM1 and AZSPWM2 algorithms based vector controlled induction motor drive respectively

Figure 7. Common mode voltage variations in CSVPWM, AZSPWM1 and AZSPWM2 algorithms based vector controlled induction motor drive respectively

From the simulation results, it can be observed that the SVPWM algorithm results in large common mode voltage variations and the proposed AZSPWM algorithms result in less common mode voltage variations. However, the proposed AZSPWM algorithms give more harmonic distortion when compared with the CSVPWM algorithm because of opposite pulses in the line voltages. Thus, the proposed AZSPWM algorithms give reduced common mode voltages and hence reduced common mode currents when compared with the CSVPWM algorithm without any extra hardware requirements.

# 7. CONCLUSION

A Novel AZSPWM algorithms based on the concept of imaginary switching times are presented in this paper for vector controlled induction motor drive. The proposed algorithms did not use the information of angle and sector and hence reduces the complexity involved in the conventional space vector approach. From the simulation results, it can be observed that the proposed algorithms reduce the common mode voltage variations when compared with CSVPWM algorithm with slight increased ripples in current and torques without any additional hardware requirements. In the proposed AZSPWM algorithms, AZSPWM2 gives better performance when compared with the AZSPWM1 algorithm.

# **REFERENCES (10 PT)**

- [1] F. Blaschke "The principle of field orientation as applied to the new transvector closed loop control system for rotating-field machines", *Siemens Review*, 1972, pp 217-220.

- [2] Heinz Willi Vander Broeck, Hnas-Christoph Skudelny and Georg Viktor Stanke, "Analysis and realization of a pulsewidth modulator based on voltage space vectors", *IEEE Trans. Ind. Applicat.*, vol. 24, no. 1, Jan/Feb 1988, pp. 142-150.

- [3] J.M. Erdman, R. J. Kerkman, D.W. Schlegel, and G. L. Skibinski, "Effect of PWM inverters on ACmotor bearing currents and shaft voltages", *IEEETrans. Ind. Appl.*, vol. 32, no. 2, pp. 250–259, Mar./Apr. 1996.

- [4] G. L. Skibinski, R. J. Kerkman, and D. Schlegel, "EMI emissions of modern PWM AC drives", *IEEE Ind. Appl. Soc. Mag.*, vol. 5, no. 6, pp. 47–81, Nov./Dec. 1999.

- [5] Y. S. Lai and F. S. Shyu, "Optimal common-mode voltage reduction PWM technique for inverter control with consideration of the dead-time effects—Part I: Basic development", *IEEE Trans. Ind. Appl.*, vol. 40, no. 6, pp. 1605–1612, Nov./Dec. 2004.

- [6] Y. S. Lai, P. S. Chen, H.K. Lee, and J.Chou, "Optimal common-mode voltage reduction PWM technique for inverter control with consideration of the dead-time effects—Part II: Applications to IM drives with diode front end", *IEEE Trans. Ind. Appl.*, vol. 40, no. 6, pp. 1613–1620, Nov./Dec. 2004.

- [7] J. Zitzelberger and W. Hofmann, "Reduction of bearing currents in inverter fed drive applications by using sequentially positioned pulse modulation", *EPE J.*, vol. 14, no. 4, pp. 19–25, 2004.

- [8] Emre Ün and A.M. Hava, "A high performance PWMalgorithmfor common mode voltage reduction in three-phase voltage source inverters", in *Proc. IEEE PESC 2008*, pp. 1528–1534.

- [9] A. M. Hava, and Emre Ün, "Performance Analysis of Reduced Common-Mode Voltage PWM Methods and Comparison With Standard PWM Methods for Three-Phase Voltage-Source Inverters", IEEE Trans. Power Electron., vol. 24, no. 1, pp. 241-252, Jan, 2009.

- [10] Dae-Woong Chung, Joohn-Sheok Kim and Seung-Ki Sul, "Unified voltage modulation technique for real-time three-phase power conversion", *IEEE Trans. Ind. Applicat.*, vol. 34, no. 2, Mar/Apr 1998, pp. 374-380.

- [11] T. Brahmananda Reddy, J. Amarnath and D. Subbarayudu, "Improvement of DTC performance by using hybrid space vector Pulsewidth modulation algorithm", *International Review of Electrical Engineering*, Vol.4, no. 2, pp. 593-600, Jul-Aug, 2007.

- [12] K. Satyanarayana1, J. Amarnath2, and A. Kailasa Rao1, "Hybrid PWM Algorithm with Low Computational Overhead for Induction Motor Drives for Reduced Current Ripple", *ICGST-ACSE journal*, vol. 10, isue. 1, pp. 29-37, Dec, 2010.

# **BIOGRAPHIES OF AUTHORS**

**Dr. J. Amarnath** graduated from Osmania University in the year 1982, M.E from Andhra University in the year 1984 and Ph.D from J. N. T. University, Hyderabad in the year 2001. He is presently Professor in the Department of Electrical and Electronics Engineering, JNTU College of Engineering, Hyderabad, India. He presented more than 300 research papers in various national and international conferences and journals. His research areas include Gas Insulated Substations, High Voltage Engineering, Power Systems and Electrical Drives.

**Dr. A. Kailasa Rao** graduated from IIT, Kharagpur in Electrical Engineering. He took his M. Tech degree in Power Systems from JNTU, Hyderabad and obtained Ph.D, from IIT, Kharagpur in Control Systems. He has Published many research papers in International Journals. A research monograph based on his Ph.D Thesis work is published by Springer Verlag, New York. Currently, he is a Professor and Director of Pragati Engineering College, Surampalem<u>a</u> Andhra Pradesh, INDIA.

**K. Satyanarayana** obtained M.Tech degree in Power Electronics from JNTU College of Engineering, Hyderabad in 2003. He is presently working as Professor in the Department of Electrical and Electronics Engineering, Pragati Engineering College, Surampalem, Peddapuram, A.P., INDIA. He is presently pursuing Doctoral degree from JNTU. College of Engineering, Kakinada. He presented many research papers in various national and international journals and conferences. His research interests include Power Electronic Drives, PWM, Fuzzy logic and Vector Control techniques.