### 40

# A Comparative Studies of Cascaded Multilevel Inverters Having Reduced Number of Switches with R and RL-Load

Lipika Nanda<sup>1</sup>, A. Dasgupta<sup>2</sup>, U. K. Rout<sup>3</sup>

<sup>1-3</sup>Department of Electrical Engineering, KIIT University, India

### **Article Info**

### Article history:

Received Sep 21, 2016 Revised Nov 26, 2016 Accepted Dec 07, 2016

### Keyword:

Bidirectional switch Switching loss Symmetric multilevel inverter Total harmonic distortion Voltage stress

### ABSTRACT

Multilevel inverter offers many benefits for high power application compavered to conventional cascaded Multilevel Inverter topology. This paper presents Symmetric CMLI using variable frequency carrier based pulse width modulation techniques. The proposed topology reduces total harmonic distortion and reduced switching losses for seven level inverter. The simulation study of the proposed topology has been carried out in MATLAB/SIMULINK. The main objective of this paper is to achieve number of levels of MLI with reduced number of switches and DC power sources compared to conventional topology.

Copyright © 2017 Institute of Advanced Engineering and Science.

All rights reserved.

### Corresponding Author:

Lipika Nanda,

Department of Electrical Engineering,

KIIT University, Bhubaneswar,

Odisha, India, pin-751024.

Email: lnandafel@kiit.ac.in

### 1. INTRODUCTION

In a multilevel inverter a desired output voltage has been synthesized to several levels from a number of DC sources as inputs. The most attractive applications of multilevel power conversion technology are in the medium to high voltage ranges [1]. A multilevel inverter not only achieves high power ratings but also enables the use of renewable energy sources. Renewable energy sources i.e solar photovoltaic, wind, fuel cells etc. can be easily interfaced to multilevel converter for high power applications [2].

Three different topologies have been proposed for multilevel inverters i.e cascaded MLI, Diode-clamped MLI and capacitor clamped. Each of the topology has a different mechanism to provide voltage levels [3]. These topologies are widely referred to as the 'classical topologies' [4]. One major disadvantage of multilevel power conversion is that great number of power semiconductor switches needed. Another disadvantage of multilevel power converters is that the voltage steps are produced by isolated DC voltage sources or a bank of series capacitors. Isolated voltage sources may not always be readily available and series capacitors require voltage balance [5].

There are two PWM methods mainly used in multilevel inverter control strategy. One is fundamental switching frequency and another is high switching frequency.for high switching frequency classified as space vector PWM, Selective Harmonic Elemination PWM and SPWM. Among these PWM methods SPWM is the most preferable as it is simple and easy to implement [6]-[7]. In this paper SPWM method with different carrier based disposition as PDPWM and APODPWM have been analyzed.

### **EXISTING TOPOLOGIES**

Conventional cascaded seven level multilevel inverter require twelve switches and 3 dc sources separately [4]. To overcome the drawbacks of it next topologies are made with seven level nine switches 3 dc sources, seven level seven switches and 3 dc sources etc [7]. The proposed topologies are designed for seven level, 6 switches with 4 dc and 3 dc sources respectively with bidirectional switches where the harmonics are reduced.

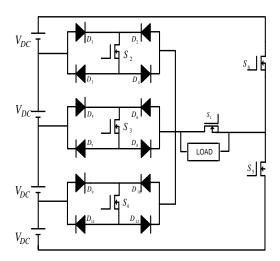

### 2.1. Proposed Topology-I

The proposed topology is designed with six switches without H-bridge and four dc sources as shown in Figure 1. The proposed topology is simple in design compared to the existing topologies. Switches S6 and S7 are used for generating the pulses in positive and negative sequence and switch S1 is connected to the load. It is used only when all the switches are open to produce zero voltage level. Switch S2, S3, and S4 are used to generate the levels Vdc, 2Vdc, 3Vdc in both positive and negative levels.

The generalized expression for the number of switches and the number of Dc sources are

$$S=(N+5)/2$$

and  $V=(N+1)/2$

Where N=Number of levels, S= No. of switches and V=No. of DC sources.

Both the carrier based PWM techniques i.e IPD PWM and APOD PWM methods are analyzed with resistive and RL-type load.

Figure 1. Configuration of seven level six switches with 4 DC sources proposed Topology

|       | Table 1. Switching pattern for seven level six switches 4 De sources |     |            |     |     |     |      |      |      |      |       |                   |

|-------|----------------------------------------------------------------------|-----|------------|-----|-----|-----|------|------|------|------|-------|-------------------|

| SL.No | <b>S</b> 1                                                           | S2  | <b>S</b> 3 | S4  | S5  | S6  | D1D4 | D2D3 | D5D8 | D6D7 | D9D12 | Output<br>Voltage |

| 1     | Off                                                                  | Off | Off        | On  | On  | Off | Off  | Off  | Off  | Off  | On    | $V_{dc}$          |

| 2     | Off                                                                  | Off | On         | Off | On  | Off | Off  | Off  | On   | Off  | Off   | $2V_{dc}$         |

| 3     | Off                                                                  | On  | Off        | Off | On  | Off | On   | Off  | Off  | Off  | Off   | $3V_{dc}$         |

| 4     | On                                                                   | Off | Off        | Off | Off | Off | Off  | Off  | Off  | Off  | Off   | 0                 |

| 5     | Off                                                                  | On  | Off        | Off | Off | On  | Off  | On   | Off  | Off  | Off   | $-V_{ m dc}$      |

| 6     | Off                                                                  | Off | On         | Off | Off | On  | Off  | Off  | Off  | On   | Off   | $-2V_{dc}$        |

| 7     | Off                                                                  | Off | Off        | On  | Off | On  | Off  | Off  | Off  | Off  | Off   | $-3V_{dc}$        |

Table 1. Switching pattern for seven level six switches 4 Dc sources

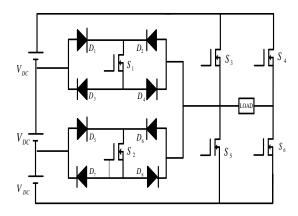

## 2.2. Proposed Topology-II

It is simple in design and compared to other existing topologies. It consists of three DC sources and six switches.the generalized expression for the number of switches ad number of Dc sources for the topology is given by

$$S=(N+5)/2$$

and  $V==(N-1)/2$ .

42 ISSN: 2088-8694

Both the carrier based PWM techniques i.e IPD and APOD PWM methods are analyzed with resistive load type.

Figure 2. Configuration of seven level six switches with 3 DC sources proposed Topology

Table 2. Configuration of 7 level 6 switches and 3Dc sources

| SL.No | S1  | S2  | S3  | S4  | S5  | <b>S</b> 6 | D1D4 | D2D3 | D5D8 | D6D7 | Output<br>Voltage |

|-------|-----|-----|-----|-----|-----|------------|------|------|------|------|-------------------|

| 1     | Off | On  | Off | Off | Off | On         | Off  | Off  | On   | Off  | $V_{dc}$          |

| 2     | On  | Off | Off | Off | Off | On         | On   | Off  | Off  | Off  | $2V_{dc}$         |

| 3     | Off | Off | On  | Off | Off | On         | Off  | Off  | Off  | Off  | $3V_{dc}$         |

| 4     | Off | Off | Off | Off | Off | Off        | Off  | Off  | Off  | Off  | 0                 |

| 5     | On  | Off | Off | On  | Off | Off        | Off  | On   | Off  | Off  | $-V_{dc}$         |

| 6     | Off | On  | Off | On  | Off | Off        | Off  | Off  | Off  | On   | $-2V_{dc}$        |

| 7     | Off | Off | Off | On  | On  | Off        | Off  | Off  | Off  | Off  | $-3V_{dc}$        |

# 3. MODES OF OPERATION

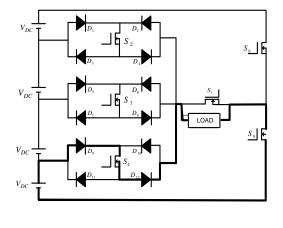

# 3.1. Topology -1

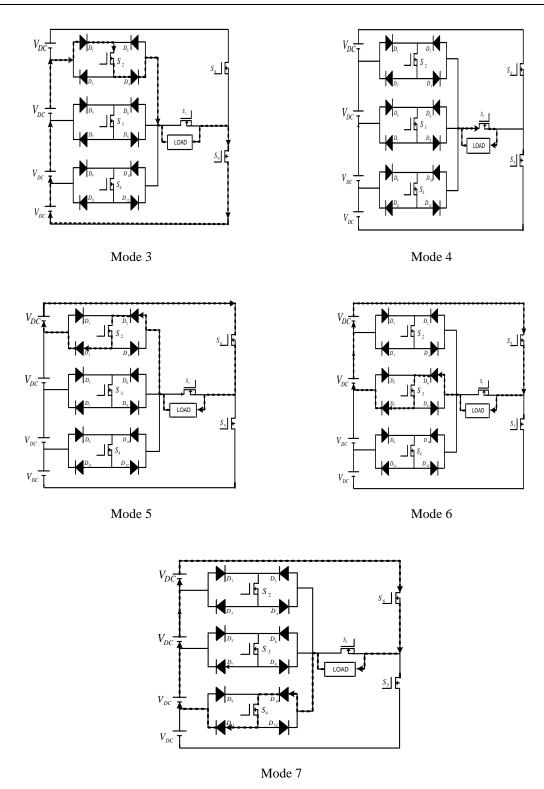

Mode 1 Mode 2

Figure 3. Different modes of operation of 7 levels, 6 switches and 4 DC sources CMLI

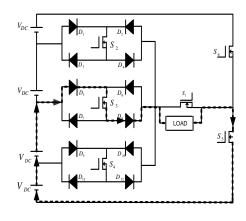

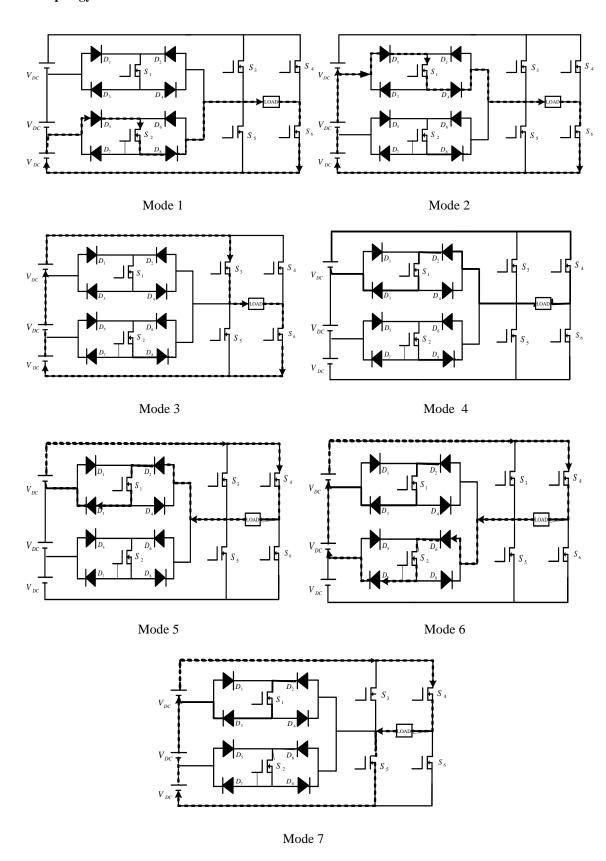

# 3.2. Topology -II

Figure 4. Different modes of operation of 7 levels, 6 switches and 3 Dc sources CMLI

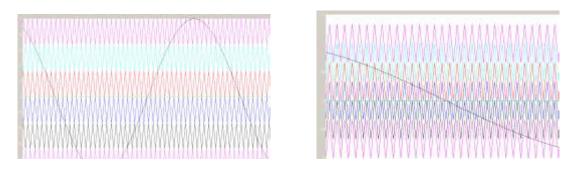

### 4. PWM TECHNIQUES

The carrier based modulation techniques for multilevel inverters can be generally classified into two categories: phase shifted and level shifted modulations. Both modulation schemes can be applied to the cascaded multilevel inverter [8]-[9]. Total harmonic distortion of phase shifted modulation is much higher than level shifted modulation. Hence level shifted modulation technique is being chosen. In this paper SPWM method with different carrier based disposition as PDPWM and APODPWM have been analyzed.

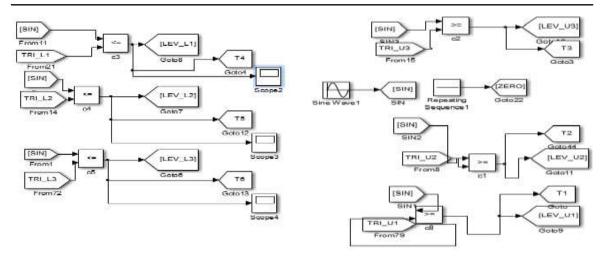

Figure 5. APOD and IPD PWM Switching Schemes

### 5. SIMULATION RESULTS

### 5.1. Topology - I

All the switches used in this circuit are MOSFETS. The switches  $S_2$ ,  $S_3$ ,  $S_4$  are bidirectional and remaining switches are unidirectional.the loads are resistive and RL-load. The DC sources are 10V.

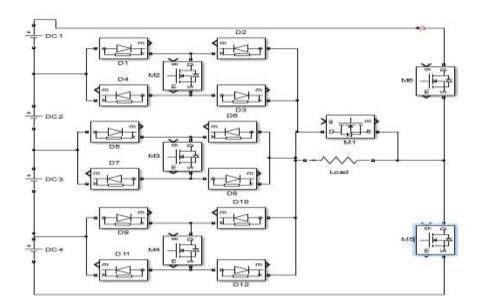

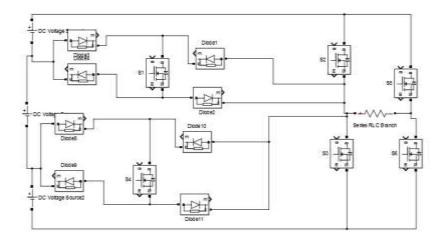

Figure 6. Simulation Diagram of Proposed Topology 1

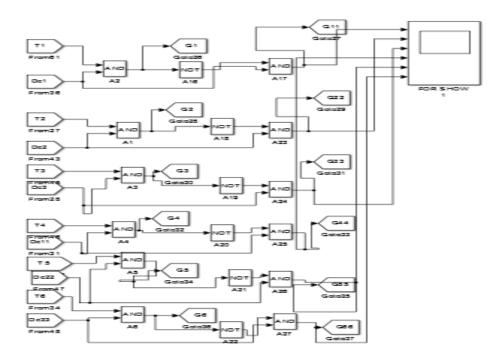

Sine and triangular carriers are compared and 7 levels are generated. Both the Dc and different levels generated are fed to logic gates to produce gate signals. These gate signals are fed to switches  $S_1$  to  $S_7$  respectively.

46 □ ISSN: 2088-8694

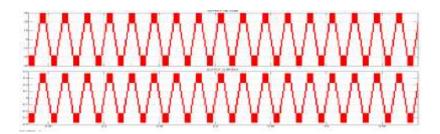

Figure 7. Different levels generation

Figure 8. Gate Pulse Generation

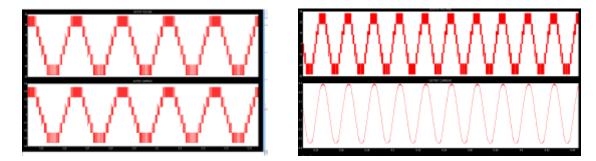

Figure 9(a). Output voltage and current with Resistive load (b) with RL -Load

Figure 10(a). APOD switching scheme (b) IPD switching scheme

# 5.2. Topology II

All the switches used in this circuit are unidirectional except switches S1 and S2 of circuit diagram. All the Dc sources are taken as 10~Vdc and Resistance as 80~ohms.

Figure 11. Simulation of 7 levels six switches and 3 Dc sources topology

Figure 12. IPD PWM switching scheme, 7 levels, 6 switches, 3 DC sources

Comments: Vout=30V at R=80ohms and carrier frequency=5KHz

48 □ ISSN: 2088-8694

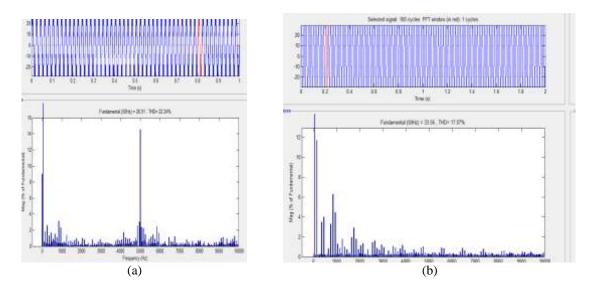

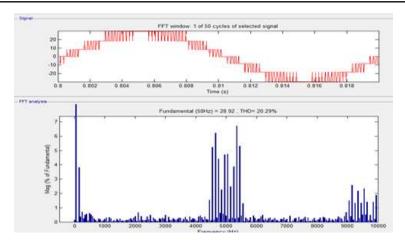

Figure 13. THD Analysis

At R=80 ohms, THD=20%, Fundamental output voltage=28.9V

# 6. COMPARISON OF TWO TOPOLOGIES

# 6.1. THD Analysis

Table 3. Comparison of two topologies with APOD and IPD switching schemes

7 levels, 6 switches, 4 DC sources Topology

| PWM  | MI  | THD   | Fundamental (Simulated) | Fundamental (Calculated) |

|------|-----|-------|-------------------------|--------------------------|

| APOD | 0.8 | 23.73 | 22.46                   | 23.7                     |

|      | 0.9 | 23.15 | 24.98                   | 25.6                     |

|      | 1   | 19    | 27.8                    | 28.3                     |

| IPD  | 0.8 | 23.48 | 22.53                   | 23.4                     |

|      | 0.9 | 23.11 | 25.09                   | 25.9                     |

|      | 1   | 19.08 | 27.94                   | 29.3                     |

|      |     |       |                         |                          |

7 levels, 6 switches, 3 DC sources Topology

| 7 icvers, 6 switches, 5 De sources Topology |     |       |                         |                          |  |  |  |  |  |  |

|---------------------------------------------|-----|-------|-------------------------|--------------------------|--|--|--|--|--|--|

| PWM                                         | MI  | THD   | Fundamental (Simulated) | Fundamental (Calculated) |  |  |  |  |  |  |

| APOD                                        | 0.8 | 24.87 | 22.69                   | 24.2                     |  |  |  |  |  |  |

|                                             | 0.9 | 24.72 | 25.66                   | 26.3                     |  |  |  |  |  |  |

|                                             | 1   | 20.29 | 28.9                    | 30                       |  |  |  |  |  |  |

| IPD                                         | 0.8 | 24.82 | 22.82                   | 24.2                     |  |  |  |  |  |  |

|                                             | 0.9 | 24.6  | 25.73                   | 26.4                     |  |  |  |  |  |  |

|                                             | 1   | 19.8  | 29.01                   | 29.9                     |  |  |  |  |  |  |

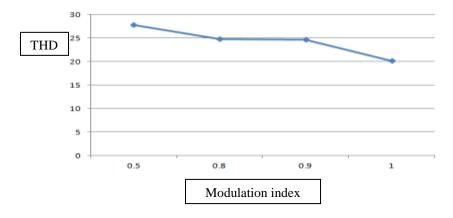

Figure 14. THD Vs Modulation Index of 7 level 6 switches and 4 Dc sources, Comment: With increase of Modulation index THD reduced

### 6.2. Voltage Stress Across Switches

It has been observed that reduced number of switches give more voltage stress compared to conventional CMLI.

Table 4. Voltage stresses across the switches

| Conventional              |       | 7 levels 4 DC sources in V |       |       |       |       |       | 7 levels 3 DC sources in V |       |       |       |       |  |

|---------------------------|-------|----------------------------|-------|-------|-------|-------|-------|----------------------------|-------|-------|-------|-------|--|

| 10V (Across all switches) | $S_1$ | $S_2$                      | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_1$ | $S_2$                      | $S_3$ | $S_4$ | $S_5$ | $S_6$ |  |

| 10V (Across all switches) | 28.4  | 20                         | 10    | 20    | 40    | 40    | 18.2  | 18.2                       | 30    | 30    | 30    | 30    |  |

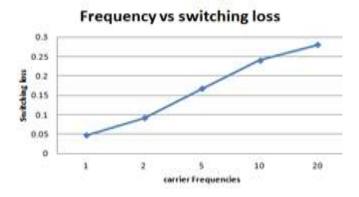

Figure 15. Carrier frequency Vs Switching loss of 7 level 6 switches 4Dc sources

### 7. LOSS CALCULATION

Each Mosfet loss has been calculated from simulation result. The voltage and current wave forms are observed from simulation diagram of each switch and thus power is being calculated. From power pulse of each switch at different carrier frequencies the switching and conduction losses are calculated. At carrier frequency 1 KHz, different losses are calculated as shown below.

Table 5. Calculation of Switching, Conduction and Total Circuit loss at different Carrier Frequencies

|                        | U/     |        |        |        |        |        |        |

|------------------------|--------|--------|--------|--------|--------|--------|--------|

|                        | S1     | S2     | S3     | S4     | S5     | S6     | Total  |

| Swtching loss (in W)   | 0.035  | 0.0016 | 0.0012 | 0.0023 | 0.05   | 0.0489 | 0.0489 |

| Conduction Loss (in W) | 0.0045 | 0.0042 | 0.004  | 0.0042 | 0.0045 | 0.0041 | 0.005  |

| Total Loss (in W)      | 0.0395 | 0.0058 | 0.0052 | 0.0065 | 0.0545 | 0.053  | 0.0539 |

Table 6. Loss at different carrier frequencies

| Carrier<br>Frequencies<br>(in KHz) | Input<br>Voltage<br>(in Volt) | Input<br>Current<br>(in Amp) | Input Power (in Watt) | Output<br>Voltage<br>(in Volt) | Output<br>Current<br>(in Amp) | Output<br>Power<br>(in Watt) | Circuit<br>Total Loss<br>(in Watt) |

|------------------------------------|-------------------------------|------------------------------|-----------------------|--------------------------------|-------------------------------|------------------------------|------------------------------------|

| 1                                  | 40                            | 0.354                        | 14.16                 | 28.35                          | 0.351                         | 9.95                         | 4.05                               |

| 2                                  | 40                            | 0.35                         | 14                    | 28.35                          | 0.35                          | 9.92                         | 4.08                               |

| 5                                  | 40                            | 0.351                        | 14.04                 | 28.35                          | 0.3482                        | 9.87                         | 4.13                               |

| 10                                 | 40                            | 0.3458                       | 13.83                 | 28.35                          | 0.354                         | 10.03                        | 3.97                               |

| 20                                 | 40                            | 0.35                         | 14                    | 28.35                          | 0.3475                        | 9.85                         | 4.15                               |

It shows with increase of carrier frequencies switching losses increases.

# 8. CONCLUSION

Inverter operation of 6 switches and 4 DC sources based topology was carried out and the required objective of low harmonics and 7 level output at THD is19.08% & Fundamental output at 27.9V at MI=1. Inverter operation of 6 switches and 3 DC sources based topology was carried out and the required objective of low harmonics and 7 level output at THD is 19.8% & Fundamental output at 29.01V at MI=1. Switching Loss, Conduction Loss and total circuit loss at different carrier frequencies are carried out successfully. Voltage stress of conventional and modified topologies are compared.

50 🗖 ISSN: 2088-8694

### REFERENCES

- [1] R. H. Baker, "High Voltage converter circuit," U.S. patent number 4, 2013.

- [2] M. N. A. Kadir, *et al.*, "Voltage vector control of a hybrid three stage eighteen level inverter by vector decomposition," *IET Trans.Power electron*, vol/issue: 3(4), pp, 601-611, 2010.

- [3] J. Rodriguez, *et al.*, "Multilevel voltage source converter topologies for industrial medium voltage drives," *IEEE Trans.Ind.Electron*, vol/issue: 54(6), pp. 2930-2945, 2007.

- [4] J. Podriguez, *et al.*, "Multilevel inverters: Sourvey of topology control and applications," *IEEE trans.ind.applicat*, vol/issue: 49(4), pp. 724-738, 2002.

- [5] E. Babaei, *et al.*, "A new general topology for cascaded multilevel inverters with reduced number of components based on developed H-bridge," *IEEE trans.Ind.Electron*, vol/issue: 61(8), pp. 3932-3939, 2014.

- [6] L. M. Tolbert and T. G. Habetler, "Novel multilevel inverter carrier based PWM method," *IEEE Transaction on Industrial application*, vol/issue: 35(5), pp. 1098-1107, 1999.

- [7] G. Carnara, et al., "A new multilevel PWM method: a Theoritical analysis," *IEEE Transactions on Power Electronics*, vol/issue: 7(3), pp. 497-505, 1992.

- [8] G. Prakash M., et al., "A new multilevel inverter with reduced number of switches," *International journal of Power Electronics and Drives system*, vol/issue: 5(1), pp. 63-70, 2014.

- [9] M. Kavitha, *et al.*, "New Cascaded H-Bridge multilevel Inverter topology with reduced number of switches and sources," *IOSR-JEEE*, vol/issue: 2(6), pp. 26-36, 2012.

### **BIOGRAPHIES OF AUTHORS**

Lipika Nanda is a Ph.D research scholar in school of Electrical Engineering ,KIIT University, Bhubanswar and has 10years of teaching experiences in the field of Power Electronics and Drives,Energy Systems etc. At present she is Asst. professor, School of Electrical Engineering, KIIT University,Bhubaneswar, India.She has published a number of papers in conferences and journal related to converters ,inverters and application of solar photovoltaics.

Abhijit Dasgupta graduated in Electrical Engg from Regional Engineering College (NIT), Durgapur in the year 1977, post-graduated from Indian Institute of Technology, Kanpur, in Power Electronics in 1980. He has 21 years of industrial experience and 13 years of academic experience. At present he is professor, School of Electrical Engineering, KIIT University,Bhubaneswar, India. He has authored more than 17 research papers in the areas of power electronics, Automatic Generation control, and implementation of new optimization techniques.

Dr.-Ing. Ullash Kumar Rout is currently working in the post of Associate Professor in School of Electrical Engineering, KIIT University, Bhubaneswar. He received his B. Tech. in Electrical Engineering from Utkal University, M. Tech. in Power System from IIT Kanpur, and Ph.D. in Energy System from University of Stuttgart, Germany. Ha has around 11 years research experience in energy system modelling and 7 years in teaching. His research interest includes energy system and power system.