# Performance of Interconnection and Damping Assignment Passivity-Based Controller on Inverter Circuits

# N. H. Ramlan<sup>1</sup>, N. A. Azli<sup>2</sup>, N. F. A. A. Hafidz<sup>3</sup>

<sup>1</sup> Faculty of Electrical and Electronics Engineering, Universiti Malaysia Pahang, Pekan, Pahang, Malaysia

<sup>1,2,3</sup> Universiti Teknologi Malaysia, Faculty of Electrical Engineering, Skudai, Johor Bahru, Malaysia

| Article Info                           | ABSTRACT                                                                                                                                                       |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article history:                       | This paper presents an extension work on the application of interconnection<br>and domping assignment passivity based controllar (IDA BBC) from the            |

| Received Sep 24, 2016                  | and damping assignment passivity-based controller (IDA-PBC) from the<br>conventional H-bridge inverter to a 5-level Cascaded H-bridge Multilevel               |

| Revised Nov 29, 2016                   | Inverter (CHMI). With the controller, the inductor current and the voltage                                                                                     |

| Accepted Dec 10, 2016                  | capacitor track the desired reference of the inverter to ensure that the output<br>voltage maintains its regulation while the Total Harmonic Distortion (THD)  |

| <i>Keyword:</i><br>CHMI                | is kept at low levels with fast transient response. It is designed based on th<br>Port-Control Hamiltonian theory exploiting the dissipation properties of the |

|                                        | averaged model of inverter circuits. The results obtained have proven that<br>the IDA-PBC previously developed for the H-bridge inverter can be easily         |

| H-Bridge                               | extended and applied to the CHMI circuit. The simulation results showed                                                                                        |

| IDA-PBC                                | that the IDA-PBC is able to maintain the output voltage regulation in both                                                                                     |

| Interconnection and damping assignment | circuits in the case of no-load to full-load condition, load uncertainty,<br>and structural uncertainty while maintaining THD of less than 5%. However,        |

| Multilevel inverter                    | in all cases, CHMI has shown better performance in terms of THD                                                                                                |

| Passivity based controller             | percentage and transient response compared to the H-bridge inverter, which are 290 $\mu$ s and 150 $\mu$ s respectively.                                       |

|                                        | Copyright © 2017 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                        |

#### Corresponding Author:

Nur Huda Binti Ramlan, Faculty of Electrical and Electronics Engineering, Universiti Malaysia Pahang, 26600 Pekan, Pahang, Malaysia. Email: nurhuda@ump.edu.my/nurhuda105@gmail.com

## 1. INTRODUCTION

Inverters are the simplest technology to convert DC to AC power and have been integrated in many applications, including uninterruptible power supplies (UPS), induction heating, high-voltage direct current (HVDC) transmission, electric vehicles, and various renewable energy applications [1],[2]. Inverters have gone through many technological improvements which include their capabilities in handling high power systems and reduction in switching losses. One of the improvement methods is by increasing the output voltage levels of the inverters that in turn reduce the Total Harmonic Distortion (THD) while also reducing the voltage stress on each component [3],[4]. The multilevel inverter topology, which was first introduced in 1975 [5], became popular over the years due to the fact that it was able to provide less disturbances and offered the possibility to function at lower switching frequencies compared to the ordinary three-level H-bridge inverters [6]. Various types of controllers such as hysteresis [7], sliding mode [8] and fuzzy logic [9] have been proposed for multilevel inverters over the years, mainly to maintain output voltage regulation and good dynamic performance. In recent years, there is an emerging interest on the development of a controller based on the concept of passivity that exploits the total energy of the system [10],[11]. There are two types of the so-called passivity-based controller (PBC) i.e the classical PBC and the interconnection and damping assignment PBC (IDA-PBC). The work presented in [12] shows that the performance of the IDA-

PBC on a single-phase H-bridge inverter is better than that of the classical PBC. The former has managed to maintain the inverter output voltage regulation with fast time response and low THD under load and parameters uncertainties. This paper extends the work presented in [12] for a 5-level Cascaded H-bridge Multilevel Inverter (CHMI). The performance of both the conventional H-bridge inverter and CHMI under IDA-PBC control are compared and analyzed.

### 2. INTERCONNECTION AND DAMPING ASSIGNMENT PASSIVITY-BASED CONTROLLER (IDA-PBC)

The IDA-PBC, introduced by Ortega et al. [13], is a physically-inspired control design methodology that invokes the principles of energy-shaping and dissipation and formulated for systems described by the Port-Controlled Hamiltonian (PCH) models. The main objective of this method is to stabilize the dynamical system by rendering the closed-loop system passive (by shaping its energy) with a desired storage function (which is a proper Lyapunov function) [11]. Apart from that, the system can be asymptotically stabilized if it can be rendered strictly (output) passive by means of damping injection [14]. This type of controller has been applied in many power electronic devices and shows remarkable results in controlling the respective system [12],[15]–[21].

In this paper, the IDA-PBC algorithm previously developed for a single-phase H-bridge inverter in [12] is used as a basis to develop the control algorithm of similar concept for a 5-level CHMI. The CHMI with five output voltage levels has been selected in this work because it owns the trade-offs of the advantages and disadvantages between the traditional H-bridge inverter and a higher output voltage level CHMI, i.e. seven, nine, eleven etc. In comparison to the H-bridge inverter, a 5-level CHMI can generate a higher output voltage magnitude by dividing the voltage between two H-bridges which results in reduced voltage stress in the circuit components. This results in a lower power losses and reduced harmonic contents in the output voltage. While higher output voltage levels of a CHMI may offer lower output voltage THD without the need for a filter circuit, the 5-level CHMI can produce a similar low output voltage THD with an added filter circuit, but at a lower cost, as it uses less number of components and switches [22].

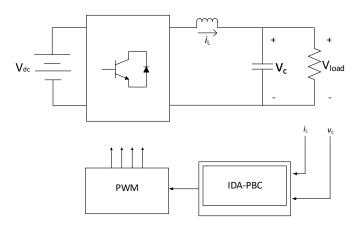

The block diagram of an inverter with its controller is shown in Figure 1. It shows that the inverter output voltage is controlled using IDA-PBC. This is possible by feeding back the inductor current,  $i_L$  and the capacitor voltage,  $v_C$  from the low-pass LC filter into the controller. The IDA-PBC uses a d-q transformation technique and produces a sinusoidal reference signal, u. This signal is compared with a carrier signal and produces the PWM signals to accordingly turn on and turn off the inverter IGBTs as the switching devices. Detailed derivation of the controller algorithm is explained in the next section.

Figure 1. Inverter controlled by the IDA-PBC

# 3. AVERAGE MODELING OF THE 5-LEVEL CHMI

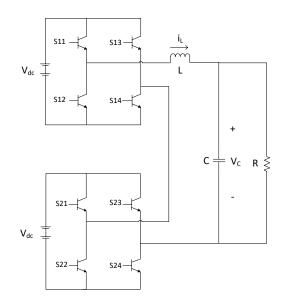

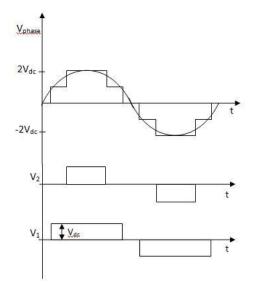

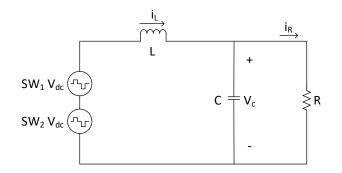

Figure 2 shows a 5-level CHMI circuit with a resistive load that is connected to an LC filter. Each H-bridge is connected to a separate DC voltage source that is used to generate the AC output voltage waveform. In general, the power circuit produces a 5-level output voltage waveform, including zero voltage as shown in Figure 3. The mathematical model of the CHMI is developed through an average modeling method as explained in [23], where each DC source is represented by a reduced cell denoted as  $sw_1 \cdot V_{dc}$

**D** 71

and  $sw_2 \cdot V_{dc}$  respectively. The simplified average circuit of the 5-level CHMI is shown in Figure 4. Each of the new, reduced cells can produce a 3-level output voltage waveform consisting of  $+V_{dc}$ ,  $-V_{dc}$ , and 0. These voltages can also be represented by the  $sw_i$  switching function as +1, -1, and 0. The combination of both reduced cells can synthesize a 5-level output voltage waveform, represented by the  $sw_i$  switching function as -2, -1, 0, +1, and +2.

Figure 2. 5-level CHMI with LC filter

Figure 3. 5-level CHMI output voltage waveform

Figure 4. Simplified equivalent average circuit of the 5-level CHMI

By applying Kirchoff's Law, the mathematical model obtained for Figure 4 are as follows:

$$L\frac{di_L}{dt} = sw_1 \cdot V_{dc} + sw_2 \cdot V_{dc} - V_C \tag{1}$$

$$C\frac{dv_c}{dt} = -\frac{1}{R}v_c + i_L \tag{2}$$

Equations (1) and (2) showed that the system is operating in discontinuous mode. Considering that each DC bus feeds the same voltage to each cell, and that each control signal, u is assigned to each cell and is denoted as  $u_1$  and  $u_2$ , with  $u = \{0, 1\}$ , the equation (1) can be represented as:

$$L\frac{di_L}{dt} = \bar{u} \cdot V_{dc} - v_C \tag{3}$$

Performance of Interconnection and Damping Assignment Passivity Based Controller on .... (N. H. Ramlan)

In this rearranged equation (3), the control signal is represented by  $\overline{u}$ , where the discrete set  $\overline{u} = \{-2, -1, 0, +1, +2\}$  represents *u*, which defines the 5-level output voltage of the CHMI. This averaging derivation technique for the CHMI has been proposed and discussed in [23],[24].

## 4. THE PROPOSED CONTROLLER

Through the averaging technique, the control signal for a 5-level CHMI is extended to the discrete set of  $\bar{u} = \{-2, -1, 0, +1, +2\}$ . This averaging method can also be extended to a higher output voltage level multilevel inverter; given that the equation (2) and (3) are represented as:

$$L\frac{x_1}{dt} = -x_2 + \bar{u}V_{dc} \tag{4}$$

$$C\frac{x_2}{dt} = x_1 - \frac{1}{R}x_2 \tag{5}$$

where  $x_1$  and  $x_2$  are the average states corresponding to  $i_L$  and  $v_C$  respectively, while  $\bar{u}$  is a continuous signal that belongs to the continuous set (-2, 2) or more. For the multilevel inverter model, equations (4) and (5) are constrained by the control law  $\bar{u} = \bar{u}(x_1, x_2)$  such that:

$$\lim_{x \to \infty} x_1 - x_{1d} = 0 \; ; \; \lim_{x \to \infty} x_2 - x_{2d} = 0 \tag{6}$$

forcing internal stability and with prescribed behaviors for the average state of the system [25].

#### 4.1. Port-Controlled Hamiltonian (PCH) System Details

In order to derive the IDA-PBC control algorithm, the Port Controlled Hamiltonian (PCH) description of the system is considered [25]:

$$\Sigma:\begin{cases} \dot{x} = [J(x) - R(x)] \frac{\partial H}{\partial x}(x) + g(x)u, \\ y = g^{T}(x) \frac{\partial H}{\partial x}(x), \end{cases}$$

(7)

where J(x) and R(x) are the interconnection structure and damping assignment respectively;  $x \in \mathbb{R}^n$  is the state variables vector;  $u \in \mathbb{R}^n$  is the input vector, and  $y \in \mathbb{R}^n$  is the output vector. u and y are the power variables, which in this case, are the inductor currents,  $i_L$  and capacitor voltages,  $v_C$ . H(x) is the energy (Hamiltonian) function. The  $J(x) = -J^T(x)$  represents the interconnection structure, while  $\mathbb{R}(x) = \mathbb{R}^T(x) \ge 0$  is the dissipation matrix due to resistances and frictions.

With the aim to represent the transformed model in PCH form, and applying the d-q transformation for the equivalent single-phase circuit, the state variables can be taken as  $i_{Ld}$ ,  $i_{Lq}$ ,  $v_{cd}$  and  $v_{cq}$ . The energy function is given as:

$$H(i_{L_{r}}v_{c}) = \frac{1}{2}Li_{Ld}^{2} + \frac{1}{2}Li_{Lq}^{2} + \frac{1}{2}CLv_{cd}^{2} + \frac{1}{2}Lv_{cq}^{2}$$

(8)

The d-q model is developed as follows:

$$\begin{bmatrix} i_{Ld} \\ i_{Lq} \\ \dot{v}_{Cd} \\ \dot{v}_{Cq} \end{bmatrix} = \begin{bmatrix} 0 & \frac{\omega}{L} & -\frac{1}{LC} & 0 \\ -\frac{\omega}{L} & 0 & 0 & -\frac{1}{LC} \\ \frac{1}{LC} & 0 & -\frac{1}{RC^2} & \frac{\omega}{C} \\ 0 & \frac{1}{LC} & -\frac{\omega}{C} & -\frac{1}{RC^2} \end{bmatrix} \begin{bmatrix} Li_{Ld} \\ Li_{Lq} \\ Lv_{Cd} \\ Lv_{Cq} \end{bmatrix} + \begin{bmatrix} \frac{1}{L} & 0 \\ 0 & \frac{1}{L} \\ 0 & 0 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} \overline{u}^d V_{dc} \\ \overline{u}^q V_{dc} \end{bmatrix}$$

(9)

In order to design the controller, these two important properties were taken into consideration:

i) Property 1: For the equilibria of equation (9) in the d-q frame, the desired capacitor voltage signal (a pure harmonic free sinusoidal signal with a fixed angular frequency and amplitude) is considered.

$$v_{C*} = V_P \sin \omega t \tag{10}$$

ii) Property 2: It is possible to formulate the control problem as follows, since the complete system is measurable.

ISSN: 2088-8694

a. A control law is designed such that the voltage regulation is maintained under different load conditions, while maintaining a low THD value.

The energy equation for the 5-level CHMI can be defined as [12]:

$$H_d = \frac{1}{2}L(i_{Ld} - i_{Ld*})^2 + \frac{1}{2}L(i_{Lq} - i_{Lq*})^2 + \frac{1}{2}C(v_{Cd} - v_{Cd*})^2 + \frac{1}{2}C(v_{Cq})^2$$

(11)

where  $[i_{Ld*} \quad i_{Lq*} \quad v_{Cd*} \quad v_{Cq*}]^T = \begin{bmatrix} \frac{V_P}{R} & \omega C V_P & V_P & 0 \end{bmatrix}^T$  are the equilibrium points. According to [25], it is necessary to assign the interconnection and damping matrices in order to

According to [25], it is necessary to assign the interconnection and damping matrices in order to transform the PCH model in equation (9) to the form,

$$\dot{x} = [J_d(x) - R_d(x)] \frac{\partial H_d}{\partial x}(x)$$

(12)

where  $J_d(x) = -J_d^T(x)$  and  $R_d(x) = R_d^T \ge 0$ . The derivative of  $H_d(x)$  can be expressed as:

$$H_d(x) = -\frac{\partial H_d^T(x)}{\partial x} R_d(x) \frac{\partial H_d(x)}{\partial x} \le 0$$

(13)

By considering the following properties,

i) (Integrability) K(x) is the gradient of a scalar function:

$$\frac{\partial K}{\partial x}(x) = \left[\frac{\partial K}{\partial x}(x)\right]^T$$

ii) (Equilibrium Assignment) K(x) at  $x_*$ , verifies:

$$K(x_*) = -\frac{\partial H}{\partial x}(x_*)$$

iii) (Lyapunov stability) The Jacobian of K(x), at  $x_*$ , satisfies the bound:

$$\frac{\partial K}{\partial x}(x_*) > -\frac{\partial^2 H}{\partial x^2}(x_*)$$

Thus, the vector function K(x) satisfies the following equation:

$$\left[J(x) + J_a(x) - \left(R(x) + R_a(x)\right)\right]K(x) = -\left[J_a(x) - R_a(x)\right]\frac{\partial H}{\partial x}(x) + g(x)\beta(x)$$

(14)

Under these conditions, the closed-loop system  $u = \beta(x)$  will be a port-controlled Hamiltonian system as in equation (12). The functions  $J_a(x)$  and  $R_a(x)$  are given as:

$$J_a(x) = 0, R_a(x) = \begin{bmatrix} r_1 & 0 & 0 & 0\\ 0 & r_2 & 0 & 0\\ 0 & 0 & 0 & 0\\ 0 & 0 & 0 & 0 \end{bmatrix}$$

(15)

The control-law equations based on the PCH IDA-PB controller is obtained in terms of d-q rotation, which is [12]:

$$\bar{u}^{d} = \frac{1}{V_{dc}} \left[ -r_{1}L^{2}\widetilde{\iota_{Ld}} + v_{Cd*} - \omega Li_{Lq} \right]$$

$$\bar{u}^{q} = \frac{1}{V_{dc}} \left[ -r_{2}L^{2}\widetilde{\iota_{Lq}} + \omega Li_{Lq} \right]$$

(16)

where  $\widetilde{i_{Ld}} = i_{Ld} - i_{Ld*}$  and  $\widetilde{i_{Lq}} = i_{Lq} - i_{Lq*}$ .

Finally, the control signal is given by

$$\overline{\boldsymbol{u}} = \overline{\boldsymbol{u}}^d + \overline{\boldsymbol{u}}^q \tag{17}$$

Comparing the control equation for the 5-level CHMI with a single-phase H-bridge inverter as in [12], the final control signal is rather similar, except for the fact that through average modeling of the CHMI previously explained in Section 2, the control signal for the 5-level CHMI is represented as,

$$\overline{u} = \{-2, -1, 0, +1, +2\}$$

(18)

Instead of the three-level square wave voltage in a single H-bridge. This proves that the control equation in [12], can be easily extended to cater for CHMIs of higher output voltage levels and thus produces higher output voltage with reduced THD. The following sections present the implementation of the IDA-PBC control signal for the 5-level CHMI through simulation with a performance comparison study based on a single-phase H-bridge inverter.

## 5. SIMULATION RESULTS AND DISCUSSION

Both systems have been simulated using MATLAB/Simulink for validation purposes. The parameters used in the simulation are as shown in Table 1. The switching devices are IGBT modules commutated at a frequency of 20 kHz using the phase-shift PWM method for the CHMI circuit. The controllers are implemented at a sample time of 2  $\mu$ s. In order to attenuate the high frequency ripple associated with the PWM pattern, a low-pass LC filter is connected at the output of the inverter. The L and C values have been calculated using the Butterworth filter equation and resulted in a 2.813  $\mu$ F capacitor and a 0.5 mH inductor; given that the resistor value is marked at 50  $\Omega$ . The desired AC output voltage for both circuits is 180 V<sub>peak</sub>. Hence, the DC voltage source of the H-bridge circuit is 200 V, while the voltage source of the CHMI is 100 V for each H-bridge.

| Symbol          | Parameters                              | Value   |

|-----------------|-----------------------------------------|---------|

| V <sub>dc</sub> | DC Source Voltage for H-bridge inverter | 200 V   |

|                 | DC source voltage for each cell in CHMI | 100 V   |

| fs              | Switching frequency                     | 20 kHz  |

| Ts              | Sample time                             | 2 us    |

| L               | Inductor                                | 2.81 mH |

| С               | Capacitor                               | 0.5 uF  |

| т               | Modulation index                        | 0.9     |

| f               | Frequency                               | 50 Hz   |

| Ŕ               | Resistor                                | 50 Ω    |

Table 1. Simulation parameters

## 5.1. No Load to Full Load Condition

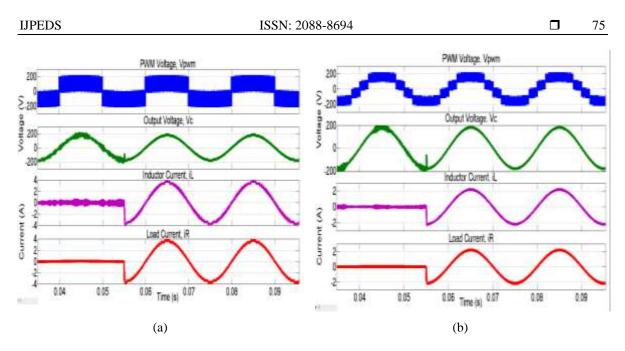

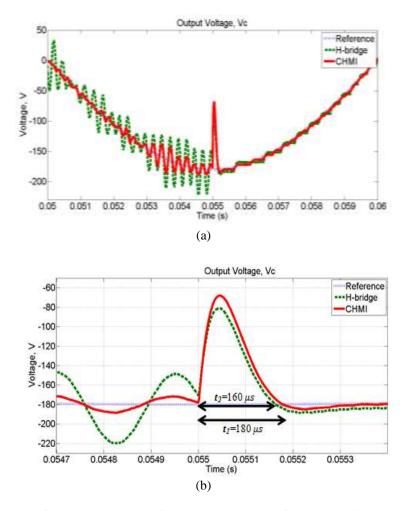

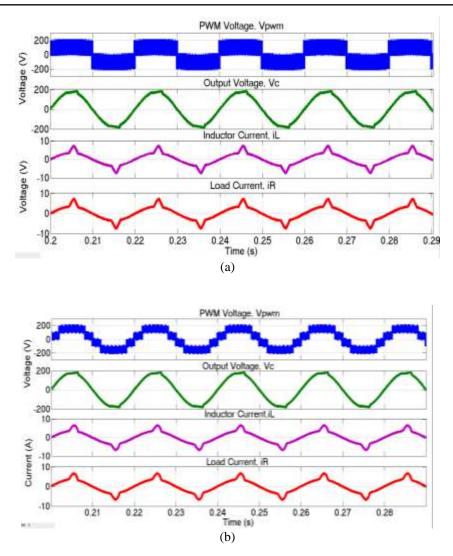

The first simulation is conducted to observe the dynamic transient response based on the IDA-PBC control algorithm for both inverters, taking into consideration the worst-case condition where a change of load is imposed at the negative peak of the reference output voltage. Initially, the inverter is operated at a no-load condition. Then, at 0.055 s, the resistor nominal value of 50  $\Omega$  is connected to provide full-load operation. Figures 5(a) and (b) show the output voltage waveform of the H-bridge inverter and the 5-level CHMI. It is noticed that in both circuits, output voltage regulation is achieved with low THD. Figure 6 shows the comparison made on the output voltage waveforms of both inverters with respect to reference during the load transition. It can be seen in Figure 6(a) that the ripples in the CHMI output voltage during unloading condition is smaller than that of the H-bridge inverter. This is reflected by the fact that the output voltage THD of the former is lower than that of the latter, which are 1.07% and 3.05% respectively. Figure 6(b) shows the transient times of the circuits. The transient time for the H-bridge inverter,  $t_1$  is measured at 180  $\mu$ s which is slightly longer than the transient time for the CHMI,  $t_2$  that is measured at 160  $\mu$ s.

Figure 5. No load to full load condition, top to bottom, PWM voltage  $V_{PWM}$ , output capacitor voltage  $V_C$ , inductor current  $i_L$ , and load current  $i_R$  (a) H-bridge Inverter and (b) 5-level CHMI

Figure 6. Comparison of output voltage waveform during no load to full load condition showing ripples and transient time, t<sub>1</sub> and t<sub>2</sub> (a) Ripples (b) Transient time

Performance of Interconnection and Damping Assignment Passivity Based Controller on .... (N. H. Ramlan)

## 5.2. Load Uncertainty

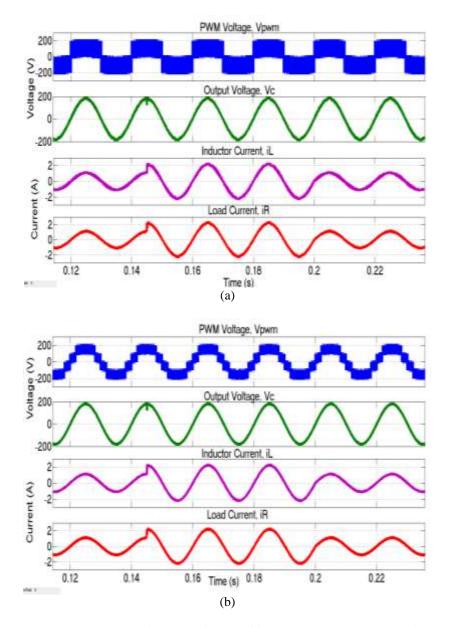

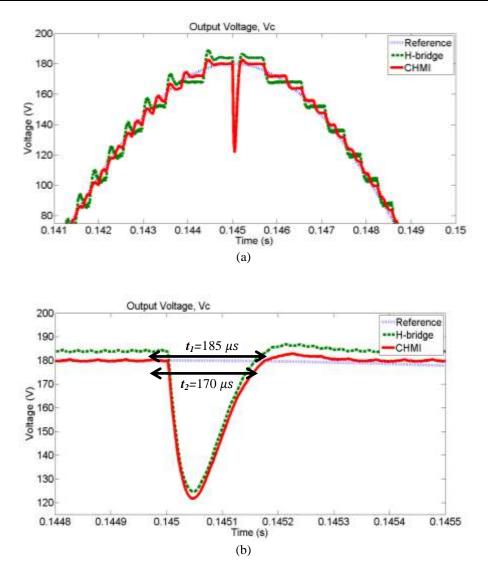

The simulation is then conducted to evaluate the robustness of the controller with respect to the uncertainty in the load resistance value. A 100% instantaneous step change in the load resistance is applied by changing the resistance from 100  $\Omega$  to 50  $\Omega$  and vice-versa. The system response under load transition for the H-bridge inverter and the 5-level CHMI are shown in Figures 7(a) and (b) respectively. It is noticed that as the load resistance is reduced, the load and inductor current increase with time while maintaining its stability and high performance, and most importantly, the output voltage regulation is maintained. Comparison of the output voltage waveforms of the H-bridge inverter and the CHMI with the reference voltage waveform is shown in Figure 8. In Figure 8 (a), it is noticeable that the output voltage of the H-bridge inverter produces more significant ripples compared to CHMI's. This leads to higher output voltage THD for the H-bridge inverter which is 4.19 % and lower output voltage THD for the CHMI which is 1.59 %. Figure 8(b) shows the settling time of the inverter circuits during load change. The settling time for the H-bridge inverter, denoted as  $t_1$  is measured at 185  $\mu s$  while the settling time for the CHMI,  $t_2$  is measured at 170  $\mu s$ .

Figure 7. System response under transient operating conditions, top to bottom, PWM voltage  $V_{PWM}$ , output capacitor voltage  $v_C$ , inductor current  $i_L$ , and load current  $i_R$  (a) H-bridge Inverter and (b) 5-level CHMI

Figure 8. Comparison of output voltage waveform during load uncertainties showing ripples and response time,  $t_1$  and  $t_2$  (a) Ripples (b) Response time

## 5.3. Structural Uncertainty Test - Nonlinear Load

The final simulation study included in this paper is also related to the uncertainty on the load; specifically, the structural uncertainty. In this case, a nonlinear load consisting of a single-phase full-bridge rectifier circuit with a capacitor and a resistor is connected in parallel to the inverter circuits. The resistance is chosen as 50  $\Omega$  whereas the capacitance is set at 350  $\mu$ F. The system response for both the H-bridge inverter and the 5-level CHMI is shown in Figures 9(a) and (b) respectively. The inductor and load currents are both distorted, as expected. However, output voltage regulation is remarkably achieved, even in the presence of the nonlinear load. The H-bridge inverter gives an output voltage THD of 3.94%, while a lower output voltage THD of 1.62% is obtained by the 5-level CHMI. Table 2 provides the summary of results obtained from the simulation study.

| Table 2. Comparison between the H-Bridge Inverter and CHMI |                          |                   |              |  |

|------------------------------------------------------------|--------------------------|-------------------|--------------|--|

| Load                                                       | Measurement              | H-Bridge Inverter | 5-level CHMI |  |

| No load to full load condition                             | THD (%)                  | 3.05              | 1.07         |  |

|                                                            | Transient time $(\mu s)$ | 180               | 160          |  |

| Load uncertainty                                           | THD (%)                  | 4.19              | 1.59         |  |

|                                                            | Settling time $(\mu s)$  | 185               | 170          |  |

| Structural uncertainty                                     | THD (%)                  | 3.94              | 1.62         |  |

Performance of Interconnection and Damping Assignment Passivity Based Controller on .... (N. H. Ramlan)

Figure 9. System response structural uncertainty, top to bottom, PWM voltage  $V_{PWM}$ , output capacitor voltage  $v_C$ , inductor current  $i_L$ , and load current  $i_R$  (a) H-bridge Inverter and (b) 5-level CHMI

#### 6. CONCLUSION

The IDA-PBC control algorithm previously applied to an H-bridge inverter in [12] can be extended for application in a 5-level CHMI, as detailed in Section 4. The newly derived control algorithm for the latter is validated through a series of simulation under various loading conditions. The controller has managed to achieve its objective in maintaining output voltage regulation while ensuring low THD in both types of inverters. However, the results obtained for the 5-level CHMI have shown a remarkably faster time response and a lower output voltage THD during all loading conditions compared to those of the H-bridge inverter. This is as expected due to the advantages offered by the multilevel inverter topology itself. For future work, new interconnections and damping matrices functions can be proposed to tune the controller for a much better output performance.

# ACKNOWLEDGMENT

The authors would like to thank the Research Management Center (RMC) of Universiti Teknologi Malaysia for their support on the research management and funding with vote number R.J130000.7808.4F799.

#### REFERENCES

- M. Divyasree and L. V. N. Rao, "Islanding Detection of Inverter Based DG Unit Using PV System," *International Journal of Power Electronics and Drive System*, vol/issue: 4(4), pp. 438–450, 2014.

- [2] M. R. Patil and P. D. D. Dighe, "Single Phase Inverter Techniques a Review," pp. 1009–1012, 2016.

- [3] N. Devarajan and A. Reena, "Reduction of switches and DC sources in Cascaded Multilevel Inverter," *Bulletin of Electrical Engineering and Informatics*, vol/issue: 4(3), pp. 186–195, 2015.

- [4] M. Malinowski, et al., "A Survey on Cascaded Multilevel Inverters," vol/issue: 57(7), pp. 2197–2206, 2010.

- [5] H. A. A. Nabae and I. Takahashi, "A new neutral-point clamped PWM Inverter," *IEEE Trans. Ind. Appl.*, vol/issue: IA-17(5), pp. 518–523,1989.

- [6] R. H. Baker and L. H. Bannister, "Electric Power Converter," U.S. Pat. 3 867 643.

- [7] K. Sundararajan, *et al.*, "Comparison of Current Controllers for a Five-level Cascaded H-Bridge Multilevel Inverter," *Ijcer*, vol/issue: 2(6), pp. 5–7, 2012.

- [8] S. Huseinbegovic and B. P. Drazenovic, "A sliding mode based direct power control of three-phase grid-connected multilevel inverter," 2012 13th Int. Conf. Optim. Electr. Electron. Equip., pp. 790–797, 2012.

- [9] A. Tomova, et al., "Fuzzy Logic Hysteresis Control of A Single Phase on Grid Inverter: Computer Investigation," *Int. J. Power Electron. Drive Syst.*, vol/issue: 3(2), pp. 179–184, 2013.

- [10] E. Nuño, et al., "Coordination of multi-agent Euler-Lagrange systems via energy-shaping: Networking improves robustness," Automatica, vol/issue: 49(10), pp. 3065–3071, 2013.

- [11] R. Ortega, et al., "Putting energy back in control," Control Syst. IEEE, vol/issue: 21(2), pp. 18–33, 2001.

- [12] D. Gerardo and Z. Universitaria, "Interconnection and Damping Passivity-Based Control applied to a Single-Phase Voltage Source Inverter," no. 2, pp. 229–234, 2010.

- [13] R. Ortega and E. G. Canseco, "Interconnection and Damping Assignment Passivity-Based Control: A Survey," *Eur. J. Control*, vol/issue: 10(5), pp. 432–450, 2004.

- [14] A. van der Schaft, "L2-Gain and Passivity Techniques in Nonlinear Control," Springer, 2000.

- [15] C. Batlle, et al., "IDA-PBC controller for a bidirectional power flow full-bridge rectifier," Proc. 44th IEEE Conf. Decis. Control. Eur. Control Conf. CDC-ECC '05, vol. 2005, pp. 422–426, 2005.

- [16] S. Yu, et al., "Continuous Finite-Time Terminal Sliding Mode IDA-PBC Design for PMSM with the Port-Controlled Hamiltonian Model," *Mathematical Problems in Engineering*, 2013.

- [17] H. González, *et al.*, "A novel induction motor control scheme using IDA-PBC," *J. Control Theory Appl.*, vol/issue: 6(1), pp. 59–68, 2008.

- [18] M. Ryalat, et al., "Integral IDA-PBC and PID-like Control for Port-Controlled Hamiltonian Systems," no. 1, pp. 5365–5370, 2015.

- [19] X. Fan, et al., "IDA-PB control design for VSC-HVDC transmission based on PCHD model," Int. Trans. Electr. Energy Syst., 2014.

- [20] M. Böttcher, et al., "Interconnection and Damping Assignment Passivity-Based current control of grid-connected PWM converter with LCL-filter," Proc. EPE-PEMC 2010 - 14th Int. Power Electron. Motion Control Conf., pp. 20–26, 2010.

- [21] J. Huang and H. Wang, "A Passivity-based Control for DC Motor Drive System with PWM," *Telkomnika Indones.* J. Electr. Eng., vol/issue: 10(8), pp. 2267–2271, 2012.

- [22] M. Derakhshanfar, "Analysis of different topologies of multilevel inverters," pp. 1-45, 2010.

- [23] H. Miranda and V. Cardenas, "Hybrid control scheme for a single-phase shunt active power filter based on multilevel cascaded inverter," Power Electronics Specialists Conference, PESC 2007. IEEE, no. 51050, pp. 1176– 1181, 2007.

- [24] H. Miranda and D. Unam, "Multilevel Cascade Inverter with Voltage and Current Output Regulated Using a Passivity – Based Controller," Conference Record - IAS Annual Meeting (IEEE Industry Applications Society), pp. 974–981, 2006.

- [25] R. Ortega, et al., "Interconnection and damping assignment passivity-based control of port-controlled Hamiltonian systems," Automatica, vol/issue: 38(4), pp. 585–596, 2002.

#### **BIOGRAPHIES OF AUTHORS**

**Nur Huda Ramlan** received her Bachelor's degree in Electrical and Electronics Engineering from Universiti Teknologi Petronas, Perak, Malaysia in 2009 and M. Eng. Degree in Electrical Engineering from Universiti Teknologi Malaysia in 2011. She is currently working towards her Ph.D. degree in the Universiti Teknologi Malaysia, Johor, Malaysia. Her current research interests are passivity-based controllers, IDA-PBC, PWM, and multilevel inverters.

Naziha Ahmad Azli received her B. Sc. Degree in Electrical Engineering from University of Miami, Florida, USA and M.E.E. and Ph.D. from Universiti Teknologi Malaysia in 1986, 1992, and 2002 respectively. She is now an Associate Professor at Universiti Teknologi Malaysia (UTM), with which she has been affiliated to since 1988. She currently teaches Power Electronics at both undergraduate and postgraduate levels at the university. Her research interests are power quality, renewable / alternate / distributed energy, and intelligent systems applied to power electronics converters.

**Nur Farhana Atiqah Amir Hafidz** received her Bachelor's degree in Electrical and Electronics Engineering from Universiti Malaysia Pahang, Pahang, Malaysia in 2015. She is currently working as a research assistant at the Faculty of Electrical Engineering at Universiti Teknologi Malaysia, Johor, Malaysia. Her current research interests are modular multilevel converters and multilevel inverters.