# A PWM Strategies for Diode Assisted NPC-MLI to Obtain Maximum Voltage Gain for EV Application

## C. Bharatiraja<sup>1</sup>, Shri Harish<sup>2</sup>, J L Munda<sup>3</sup>, P.Sanjeevikumar<sup>4</sup>, M. Sriram Kumar<sup>5</sup>, Vivek Bhati<sup>6</sup>

<sup>5,6</sup> Department of Electrical and Electronics Engineering, SRM University, Chennai, India

<sup>2</sup> Department of Mechanical Engineering, Vel Tech University, Chennai, India

<sup>3</sup> Department of Electrical Engineering Tshwane University of Technology, South Africa

<sup>4</sup>Electrical and Electronics Engineering, University of Johannesburg, South Africa

#### Article Info

Article history:

## ABSTRACT

Received Jan 18, 2017 Revised Mar 18, 2017 Accepted Apr 1, 2017

## Keyword:

Pulse width modulation (PWM) Space vector pulse width modulation (SVPWM) Neutral point clamped (NPC)

The projected diode assisted Neutral Point Diode Clamed (NPC-MLI) with the photovoltaic system produces a maximum voltage gain that is comparatively higher than those of other boost conversion techniques. This paper mainly explores vector selection approach pulse-width modulation (PWM) strategies for diode-assisted NPC-MLI to obtain a maximum voltage gain without compromising in waveform quality. To obtain a high voltage gain maximum utilization of dc-link voltage and stress on the power switches must be reduced. From the above issues in the diode assisted NPC-MLI leads to vector selection approach PWM technique to perform capacitive charging in parallel and discharging in series to obtain maximum voltage gain. The operation principle and the relationship of voltage gain versus voltage boost duty ratio and switching device voltage stress versus voltage gain are theoretically investigated in detail. Owing to better performance, diode-assisted NPC-MLI is more promising and competitive topology for wide range DC/AC power conversion in a renewable anergy application. Furthermore, theoretically investigated are validated via simulation and experimental results.

> Copyright © 2017 Institute of Advanced Engineering and Science. All rights reserved.

#### **Corresponding Author:**

C. Bharatiraja, Department of Electrical and Electronics Engineering, SRM University, Chennai, India. Email: bharatiraja@gmail.com

## 1. INTRODUCTION

Solar energy, harnessed through solar cells, can be used extensively in various power electronic applications, such as power generation and distribution system. The most prominent advantage in these applications is the low dc source voltage supply and required high output ac voltage [2],[4]. The largest aid to the power grid will be based on the development of the photovoltaic generation system through which renewable energy is utilized. The main drawback of the existing solar photovoltaic panels is the wide range voltage drop and high investment cost [5]-[6]. Hence, there is a need to boost the low dc source voltage into a high constant ac voltage. Voltage source inverter is added to normalize the amplitude and frequency in order to obtain the necessary high ac voltage for power grid [7]. The initial cost can be minimized by decreasing the number of stages of inverter. Cuk and single ended primary inductor converter (SEPIC), which have both buck-boost conversion and bidirectional power processing [8]. For improved performance, the buck-boost converter is achieved [9].However, the switching devices used in the buck- boost circuit lead to large dc source current and high intermediate dc-link voltage when the boost duty ratio is extremely high [10]. Considering adding a power conversion stage, causing increase in system cost and reduction in efficiency, Peng [1] introduced impedance source inverter. Impedance source inverter consists of a unique impedance

network between the source and the main circuit to obtain both voltage buck and boost characteristics to overcome the limitations with voltage source inverter [13].

Shoot through mode is used to enhance the low ac output voltage. This circuit provides low- cost, reliable, and single-stage methodology for dc to ac power conversion when the voltage gain is low [12]. This circuit incorporates an X-shaped diode-assisted capacitor network between the boost inductor and the inverter bridge. When  $S_1$  is turned off, the two capacitors are connected in parallel through two forwardbiased diodes and the transitional dc-link voltage  $V_i$  is equal to capacitor voltage. During this period, the three-phase voltage source inverter operates in null state and output ac voltage is zero. Sufficient utilization of intermediate dc- link voltage can improve the voltage transfer ratio and reduce the voltage gain as well as to minimize the voltage stress of the switching devices in theory [13]-[14]. Diode-assisted buck–boost VSI validates advantages in design cost and better performance in dc/ac power conversion for simultaneously much higher and wide range voltage regulation [15]. However, those methods are uses number of shoot through (ST) switching options and less bother on neutral point balancing.

Given that the neutral point balancing with minimal switching state usage was seldom investigated in the literature, this paper is demanding to cover the research gap.Within this context, in paper proposed the improved SVPWM schemes for Z-T-NPC-MLI with minimal ST state. The scheme exploits the redundancy switching vector option for both ST and regular switching, which good voltage profile and maintain the quarter symmetry and harmonic spectra.

#### 2. EQUIVALENT CIRCUIT, VOLTAGE GAIN and VOLTAGE STRESS

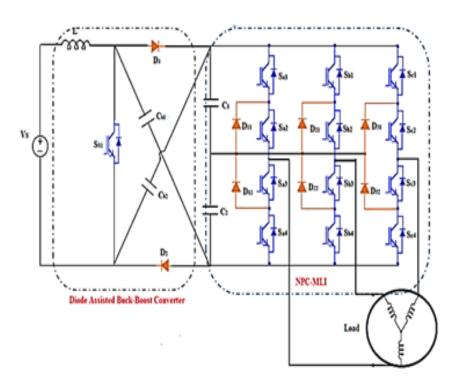

Diode based buck-boost converter shown in the Figure 1 is having two operating modes based on the switching state of the switch  $S_1$ . For our convenience the capacitance and terminal voltage across the two capacitors  $C_1$  and  $C_2$  in the symmetrical X-shape network are assumed as same values.

$$C_1 = C_2, V_{C1} = V_{C2} = V_C \tag{1}$$

The Figure 2 shows the equivalent circuit for the diode based buck-boost converter when the switch  $S_1$  is ON. In this time period the two diodes are reverse biased.

Figure 1. Circuit diagram of diode assisted buck-boost converter with NPC-MLI

Figure 2. Equivalent circuit of diode assisted buck-boost converter during S1 is ON

With this operation the inductor present in the circuit absorbs the energy from the dc source by maximizing the charging current and the dual capacitors are connected in series to feed the loads. The Equations during this time period are expressed as Equation.

$$V_L = V_S, V_{i(S_1 = 0N)} = V_{C1} + V_{C2} = 2V_C$$

(2)

Figure 3. Equivalent circuit of diode assisted buck-boost converter during S<sub>1</sub> is OFF

The Figure 3 shows the equivalent circuit of diode based buck boost converter equivalent circuit when the switch  $S_1$  is turned OFF. Then the two diodes in the circuit are forward biased the energy accumulated in the inductor is transferred to the two capacitors and both of the capacitors will be in parallel to supply the loads.

$$V_L = V_S - V_C \cdot V_{i(S_1 = OFF)} = V_{C1} = V_{C2} = V_C$$

(3)

The average voltage across inductor during one switching period in steady state is zero. From (2) and (3), the voltage of the inductor is

$$V_L = \frac{p_{\text{on}} T_{\text{s}} \cdot V_{\text{in}} + (1 - p_{\text{on}}) T_{\text{s}} \cdot (V_{\text{s}} - V_{\text{c}})}{T_{\text{s}}}$$

(4)

From the above equation, the voltage across the capacitor can be derived as

$$V_{\rm C} = \frac{1}{1 - p_{on}} V_{\rm s} \tag{5}$$

Where  $V_s$  is the input supply voltage,  $p_{on}$  is the on-state duty ratio of the switch  $S_1$ , Ts is switching time period. In the similar way the average intermediate dc-link voltage across the converter can be written as follows

$$V_{i} = \frac{p_{on} \cdot T_{s} \cdot 2V_{c} + (1 - p_{on})T_{s} \cdot V_{c}}{T_{s}} = (1 + P_{on})V_{s}$$

(6)

The switching stress across the two diodes and switch present in front of the boost circuit is equal to the voltage across the capacitor  $V_c$  and similarly the voltage stress across theswitchingdevices in the NPC-MLI is the maximum dc-link voltage of the inverter.

The bridge voltage which is twice the capacitor voltage  $2V_C$

$$V_{Sf} = V_C, V_{Si} = \hat{v}_i = 2V_C \tag{7}$$

The voltage transfer ratio of the diode based buck-boost NPC-MLI is defined as

$$G = \frac{\hat{v}_l}{\frac{V_s}{2}} = \frac{2\hat{v}_{ac}}{v_{dc}}$$

(8)

Where  $v_{ac}$  is the peak value of the output phase voltage

## 3. PROPOSED PULSE WIDTH MODULATION STRATEGIES

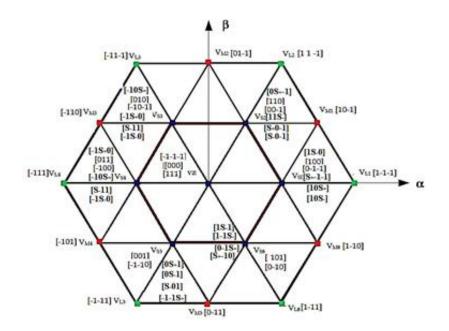

The space vector diagram for a 3-phase 3-level VSI is a hexagon, consisting of six sectors as shown in Figure 4, and each sector consists of four sub-triangles. Each inverter leg can have three switching states, which results in 27 voltage vectors. No power is delivered to the load for the switching states (111), (000), and (-1-1-1), which is referred to as the null voltage vector (NV). Hence, the 27 possible voltage vectors are classified as 18 effective voltage vectors and 1 null vector. The non-zero voltage vectors can have three phase voltage levels, which are 2/3Vs,  $V_s/\sqrt{3}$ , and  $V_s/3$ . Each voltage level corresponds to the vertex of the large hexagon called the large vector (LV), that on the middle side point of the large hexagon called the medium vector (MV) and that on the vertex of the small (inside) hexagon called the small vector (SV), respectively. The six LVs forms the vertices of the hexagon and the three NVs are located at the origin.For theoretical analysis a new concept introduced which is called as the natural point potential.

Figure 4. Space vector diagram for the proposed technique

In the stationary coordinate, a space vector of constant magnitude  $|V_r|$  and angular velocity  $\omega_r$  is introduced to represent the three-phase balanced voltage.

$$V_r = |V_r|e^{j\Theta r} = \frac{2}{3} [V_{ao} + V_{bo} e^{j\frac{2}{3}\Pi} + V_{co} e^{-j\frac{2}{3}\Pi}]$$

(9)

The factor 2/3 includes in the amplitude of the voltage vector equals the peak value of the corresponding output phase voltage. $\theta_r = \omega_r t$  is the phase angle of reference vector,  $\omega_r = 2\pi f N$  We know that,

$$V_{ON} = \frac{1}{2} (V_{aN} + V_{bN} + V_{cN}) \tag{10}$$

IJPEDS Vol. 8, No. 2, June 2017: 767 - 774

In the above equations  $V_{ao}$ ,  $V_{bo}$ ,  $V_{co}$  are the line to neutral voltages,  $V_{aN}$ ,  $V_{bN}$ ,  $V_{cN}$  are the line to zero voltages,  $V_{oN}$  is the neutral to zero voltage

$$V_{ON} = \frac{1}{3} V_c, V_{ao} = \frac{2}{3} V_c, V_{co} = V_{bo} = -\frac{1}{3} V_c$$

(11)

$$V_1 = |V_1| = \frac{2}{3}V_c \tag{12}$$

$$|V_1| = |V_3| = |V_5| = |V_7| = |V_9| = |V_{11}| = \frac{2}{3}V_c$$

(13)

$$|V_2| = |V_4| = |V_6| = |V_8| = |V_{10}| = |V_{12}| = \frac{4}{3}V_c$$

(14)

Based on the above PWM strategy there is a necessity for the new improved PWM strategy to take the full advantage on the small voltage vectors. The below figure shows the sequences of the voltage vectors in the first sextant compared with the existing PWM strategies. The active switching vectors are commanded during the both intervals when  $S_1$  is ON and  $S_2$  is OFF with one switching time period ( $T_s$ ) to synthesize the reference wave vector ( $V_r$ ). The vectors are symmetrically distributed during two switching time periods ( $2T_s$ ) by inserting the interval of  $S_1$ =ON symmetrically in centre. If the switch  $S_1$  turns ON and OFF once in two switching periods the switching loss of power devices in front of the boost circuit can be reduced to half. In order to minimize the half-switching frequency harmonics distortion, the second improved PWM strategy is presented to ensure a symmetrical placement of switching states in one switching time period. The main feature of this modulation strategy is that  $S_1$  turns ON and OFF once with  $S_1$ =ON interval symmetrically inserted at the centre of one switching period  $T_s$ . There will be an additional switching state for small vector  $V_1$ . With this introduces an additional switching state in phase leg of the inverter bridge during  $S_1$ =OFF. With the same design approach the switching states in other sextants can be obtained. The modulation index of the inverter  $M_t$  is limited by the on-state duty ratio of the switching device  $S_1$  of the front boost circuit.

$$G = \frac{{}^{2M_{i}}}{{}^{1-p_{\text{ON}}}} (0 \le M_{i} \le P_{\text{ON}})$$

(15)

The voltage stress across the switching devices in front of the boost circuit  $V_{sf}$  and that value is same as the capacitor voltage  $V_c$

$$V_{Sf} = \frac{1}{1 - p_{on}} V_S, V_{Si} = \frac{2}{1 - p_{on}} V_S$$

(16)

For the traditional carrier wave based SPWM with third harmonic injection or SVM, dc voltage utilization of the inverter bridge is increased and the maximum modulation index of  $M_t$ =1.15  $p_{on}$ .

$$G_{max} = \frac{4}{\sqrt{3}} \frac{p_{on}}{1 - p_{on}} (M_i = \frac{2}{\sqrt{3}} P_{on})$$

(17)

$$V_{sf} = \frac{4 + \sqrt{3}G_{max}}{4} V_s, V_{Si} = \frac{4 + \sqrt{3}G_{max}}{2} V_s$$

(18)

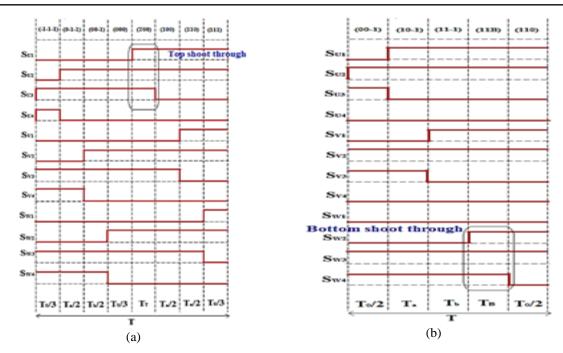

## 3.1. Shoot Through Mode

The shoot defined as the creation of the short circuit path to the inductor. The shoot through in NPC-MLI can be achieved using the triggering of all switches at a time. Three types of shoot through are available they are

- a. In full shoot through state the switches the switches 1 and 4 will triggered simultaneously

- b. In Top Shoot through state the upper half switches are triggered

- c. In bottom Shoot through state the lower half of the switches are triggered

The three above mentioned shoot through can be observed from the following waveforms, and how the operation is being achieved

Figure 5. Switching operation of NPC-MLI (a) Top shoot through (b) Bottom shoot through

## 4. SIMULATION STUDY

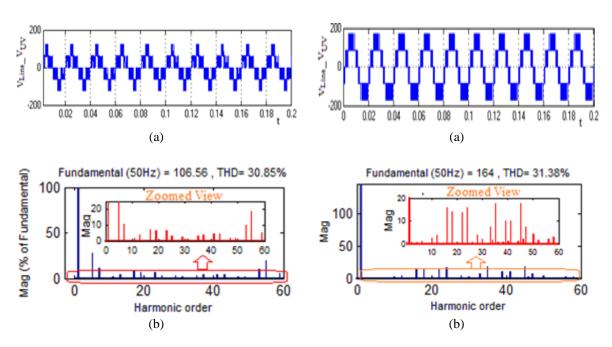

Inverter is operated in the linear modulation range with the maximum modulation index of 0.907. The values of capacitance and inductance in the Z source network are 640 micro Farad and 10 mH respectively. The internal resistance of IGBT is considered as 1 m $\Omega$  and snubber resistance is 10 micro Ohm. Two equal capacitors are considered across the supply to split the supply voltage in to two equal half and to create a neutral point. In this Simulation circuit the source voltage is considered as 100 V DC and the output of the NPC-MLI is 180 V AC (maximum). Line voltage and THD for the modulation index (M<sub>a</sub>) of 0.7 and 0.9 for the NPC-MLI is shown in the Figure 6 and Figure 7.

Figure 6. output performance characteristics for M<sub>a</sub>=0.7 (a) Line voltage (b) THD spectra

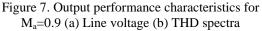

## 5. EXPERIMENTAL STUDY

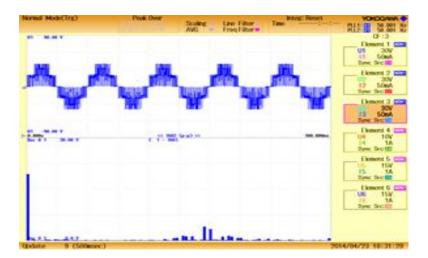

The IM is driven by a Z-source NPC-MLI with 100V DC-link and two 100 $\mu$ F front-end DC-link capacitors. Z-source Network having two 10mH inductors and two 3400 $\mu$ F capacitors.FGA15N120ANTD and CT60AM 18F which has an in-built structure of IGBT and anti-parallel diodes is used in each phase leg which provides the basic structure of NPC Type-MLI. The gate pulses for the top and bottom shoot through of each leg are shown in the Figures 8. The bottom shoot through the switches 2, 3 and 4 are triggered simultaneously as shown in the Figure 9. The experimental results for entire modulation region are shown below for  $m_a$ =0.8. Here the line voltage and THD spectra is witnessed as 167V and 32.89% respectively. Based on the simulation and excremental results, it could understand that the proposed SVM for Z NPC-MLI is produced more line voltage and less THD compare to the previous work [12]. In addition the scheme uses less number of ST, which reducing the switching losses on the inverter.Here could understand that the conduction losses are low throughout the operating value of M<sub>a</sub>, which lead the best efficiency of Z-T-NPC-MLI

Figure 8. Gate pulses of one leg in top shoot through

Figure 9. Gate pulses of one leg in bottom shoot through

Figure 10. Experimental Line voltage (30v/div) THD spectra for M<sub>a</sub>=9.0

## 6. CONCLUSION

This paper analyses the drawbacks of the existing PWM strategies for the diode assisted buck-boost VSI and then proposed new improved PWM strategy. The voltage gain and switching devise stress are improved compared to the existing PWM strategy. Simulation and experimental results are provided in order

to validate the theoretical results. The advantages are high voltage and the wide range of voltage regulation, because of these advantages this topology is using for a wide range of power conversion in renewable energy applications.

#### REFERENCES

- [1] F. Z. Peng, "Z-Source inverter," IEEE Trans. Ind. Appl., vol. 39, no. 2, pp. 504–510, Mar. 2003.

- [2] F. Gao, P. C. Loh, R. Teodorescu, and F. Blaabjerg, "Diode-assisted buck-boost voltage- source inverters," *IEEE Trans. Power Electron.*, vol. 24,no. 9, pp. 2057–2064, Sep. 2009.

- [3] Fang Zheng Peng, Miaosen Shen and Zhaoming Qian, "Maximum Boost Control of the Z-Source Inverter," *IEEE Trans. Power Electron.*, vol.20, no.4, pp. 833-838, July. 2005.

- [4] Miaosen Shen, Alan Joseph, Jin Wang, Fang Z. Peng and Donald J. Adams, "Comparison of Traditional Inverters and Z-Source Inverter for Fuel Cell Vehicles," *IEEE Trans. Power Electron.*, vol. 30, no.5, pp. 125-132, Oct.2004.

- [5] Miaosen Shen, Jin Wang, Alan Joseph, Fang Zheng Peng, Leon M. Tolbert, and Donald J. Adams, "Constant Boost Control of the Z-Source Inverter to Minimize Current Ripple and Voltage Stress," *IEEE Trans. Ind. App.*, vol.42, no.3, pp. 770-778, June.2006.

- [6] M.K. Nguyen, Y.C. Lim, and G.B. Cho, "Switched inductor quasi-Z source inverter," *IEEE Trans. Power Electron.*, vol. 26, no.11, pp. 3183–3191, Nov. 2011.

- [7] L.S. Yang, T.J. Liang, and J.F. Chen, "Transformer less dc-dc converters with high step-up voltage gain," *IEEE Trans. Ind. Electron.*, vol. 56, no. 8, pp. 3144–3152, Aug. 2009..

- [8] Miaosen Shen, Alan Joseph, Fang Z Peng, and Donald J. Adams, "Comparison of Traditional Inverters and Z-Source Inverter for Fuel Cell Vehicles," *IEEE Trans. Power Electron.*, vol. 22, no.4, pp. 125-132, July. 2007.

- [9] Yu Tang, Shaojun Xie, Chaohua Zhang, and Zegang Xu, "Improved Z- Source Inverter With Reduced Z-Source Capacitor Voltage Stress and Soft-Start Capability," *IEEE Trans. Power Electron.*, vol. 24, no.16, pp.409-415, Nov 2009..

- [10] Yi Huang, Miaosen Shen, Fang Z. Peng, and Jin Wang, "Z-Source Inverter for Residential Photovoltaic Systems," *IEEE Trans. Power Electron.*, vol. 21, no. 6, pp.1692-1698, Nov 2006.

- [11] C Bharatiraja, Jl Munda, Ishan Vaghasia, Rajesh Valiveti, P Manasa, "Low cost Real Time Centralized Speed Control of DC Motor Using Lab View -NI USB 6008," *International Journal of Power Electronics and Drive* Systems, vol.3, no.3, pp. 656-664, 2016

- [12] R.J. Wai, C.Y. Lin, and R.Y. Duan, "High-efficiency dc-dc converter with high voltage gain and reduced switch stress," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 354–364, Feb. 2007.

- [13] Z. Yi, W. Li, and X.He, "Single-phase improved active clamp coupled- inductor-based converter with extended voltage doubler cell," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 2869–2878, Jun. 2012.

- [14] J. Momoh, "Renewable Energy and Storage Smart Grid: Fundamentals of Design and Analysis," New York, NY, USA: Wiley-IEEE, vol.22, no.7, pp.140-159, Jun. 2012..

- [15] R. Antal, "Improved control of diode-assisted buck-boost voltage-source inverters," in Proc. EPE/PEMC, vol. 23, no.2, pp. 93–99, Sep.2010.

- [16] C. Bharatiraja, Harshavardhan Reddy, N. Sri Ramsai, and Sunkavalli Satya Saisuma "FPGA Based Design and Validation of Asymmetrical Reduced Switch Multilevel Inverter, *International Journal of Power Electronics and Drive System (IJPEDS)*, Vol. 7, No. 2, pp. 340-348, June 2016.

- [17] M. Liserre, F. Blaabjerg, and S. Hansen, "Design and Control of an LCL-Based Three-Phase Active Rectifier", *IEEE Transactions on Industry Applications*, vol. 41, No.5, September/October 2005.

- [18] E. Twining and D. G. Holmes, "Grid Current Regulation of a Three Phase Voltage Source Inverter with an LCL Input Filter," in *IEEE Transactions on Power Electronics*, vol. 18, No. 3, pp. 888-895, May2003.

- [19] C.Bharatiraja, S.Jeevananthan, R.Latha, "Vector Selection Approach-based Hexagonal Hysteresis Space Vector Current Controller for a Three-phase Diode Clamped MLI with Capacitor Voltage Balancing", *IET Power Electronics*, vol.9, Issue 7, pp.1350-1361, 8 June 2016.

- [20] C.Bharatiraja,S.Raghu,P.Rao, K.R.S.Paliniamy, "Comparative Analysis of Different PWM Techniques to Reduce the Common Mode Voltage in Three-level Neutral-point- clamped Inverters for Variable Speed Induction Drives", *International Journal of Power Electronics and Drive Systems*, vol. 3, Issue 1,Pages 105-116. March 2013.

- [21] C. Bharatiraja, R. Latha, Dr. S. Jeevananthan, S. Raghu and Dr. S.S. Dash. "Design and Validation of Simple Space Vector PWM Scheme for Three-Level NPC - MLI with Investigation of Dc Link Imbalance using FPGA IP Core", *Journal of Electrical Engineering*, vol. 13, edition 1, pp 54-63, 2013.

- [22] C. Bharatiraja, J.L. Munda, N. Sriramsai, T Sai Navaneesh, "Investigation of the Common Mode Voltage for a Neutral-Point-Clamped Multilevel Inverter Drive and its Innovative Elimination through SVPWM Switching-State Redundancy," International Journal of Power Electronics and Drive Systems, vol.7, no.3, pp892-900,2016.

- [23] K. Ramesh, C. Bharatiraja, S. Raghu, G. Vijayalakshmi, PL. Sambantha, "Design and Implementation of Real Time Charging Station Optimization Infrastructure for Hybrid Electric Vehicles,"*International Journal of Power Electronics and Drive Systems*, vol.7, no. 4, 2016.