# Appropriate Switching State Selection to Avoid Capacitor Imbalance in Five-Level NPC

# K.Narasimha Raju<sup>1</sup>, Chandra Sekhar O<sup>2</sup>, Ramamoorthy M<sup>3</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, K.L University, Vaddeswaram, Guntur, India <sup>1,2,3</sup>Department of Electrical Engineering, K.L University, Vaddeswaram, Guntur, India

# Article Info ABSTRACT

# Article history:

Received Nov 21, 2017 Revised Dec 12, 2017 Accepted Dec 18, 2017

## Keyword:

Capacitor junction imbalance Five level Multilevel Inverters Neutral point clamped Space vector pulse width modulation

An intrinsic problem with neutral point clamped (NPC) multilevel inverters (MLI) is unbalance of capacitor voltage. There are many mitigation techniques well established in the literature to balance the neutral point voltage for 3-level inverter. These techniques employ either Carrier based pulse width modulation (CBPWM), Space vector pulse width modulation (SVPWM) or hybrid of both the PWM techniques. Balancing becomes complicated as the level of the inverter increases due to addition of capacitor junctions. The imbalance in capacitor voltages may cause uneven voltage distribution among switching devices and sometimes may cause failure. It also increases harmonic content in its output waveform. This paper develops new modulation scheme for balancing capacitor voltages for 5level inverter .The scheme is a hybrid PWM which is a combination of both CBPWM and SVPWM techniques. As per this scheme CBPWM is applied to meet the load demand and at the zero crossings of the reference signal, CBPWM is blocked and for one carrier cycle. During this SVPWM is applied with appropriate switching state selection to neutralize the imbalance in capacitor voltage.

> Copyright © 2018 Institute of Advanced Engineering and Science. All rights reserved.

# **Corresponding Author:**

K.Narasimha Raju, Departement of Electrical and Electronics Engineering, Research scholar K.L.University EEE department Vaddeswaram narasimharaju\_eee@kluniversity.in

## 1. INTRODUCTION

Now-a-days, multilevel converters are playing an important role in most of the medium and high power industrial and utility applications. This is because of their capability to operate at lower switching losses, reduction of electromagnetic interference, improved <u>THD</u>, less stress on the switches compared to two level converters. Among the wide varieties of multilevel converters, <u>NPC MLI</u> is widely chosen for many high power applications due to the following reasons

- 1) Static voltage equalization among switches.

- 2) Reduced dV/dt.

- 3) No dynamic voltage sharing problem.

- 4) Economics of the converter.

Despite of the above advantages, NPC MLI has an inherent drawback of unbalance in capacitor voltages at its DC side. Due to the difference in tolerance values of the capacitors and turn on-off times of the switches increases the unbalance to large extent making the converter operation undesirable [1]. A 3-level NPC converter consists of only two capacitors which make the control over the unbalance in capacitor voltages in a straight forward approach [8]. There exist many stabilization techniques in literature for three level clamped converters such as level shifted reference PWM, SVPWM techniques, in which control is done inherently without any use of external circuit [10]. But as the level of inverter increases capacitor junctions

**D** 277

increase which makes the control quite difficult. This unbalance of capacitor voltages leads to device failure and distorted voltage and current waveforms in the output. As a remedy to this usage of auxiliary dc/dc converters in the place of capacitors were proposed in [3].And techniques with back-back connection i.e. use an active rectifier as a front end to a multilevel inverter system in which both requires an external circuit[4]. Both these add to increased cost and complexity in control. This paper presents a novel control technique which provides inherent control over the saturation of capacitor voltages for a five level NPC converter without usage of any external circuit. The control scheme proposed is a hybrid of carrier based and SVPWM techniques with selection of appropriate switching states for stabilization of neutral point voltage [9]. Figure 1 describes the structure of five level diode clamped converter.

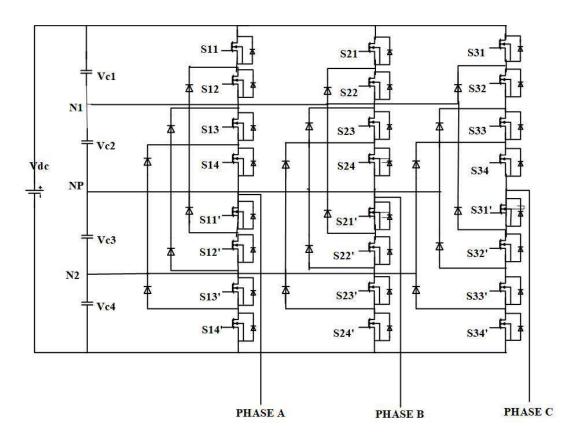

Figure 1. Five level DCMLI Topology

## 2. FIVE-LEVEL INVERTER

Figure 1 describes the structure of five level diode clamped converter. This converter topology employs clamped diodes that are responsible for equal voltage sharing among switches making them more reliable [2]. A 3-phase N level diode clamped inverter needs (N-1) capacitors, 3(N-1) (N-2) clamped diodes, 6(N-1) active switches. This paper deals with the five level NPC which consists of 4 capacitors forming 3 capacitor junctions [1]. The current through these capacitor junctions is responsible for unbalance in capacitor voltages making the inverter operation undesirable. It uses 36 clamped diodes and 24 active switches of same voltage sharing making it more economical compared to other converters. The following table provides the phase to neutral point voltages according to the switching positions. Figure 2 shows DC bus capacitors and their junction currents

| uU | 10 1.1 | 5 1110 | iiiig u |       |                 | CIU |

|----|--------|--------|---------|-------|-----------------|-----|

|    | $S_1$  | $S_2$  | $S_3$   | $S_4$ | V <sub>an</sub> |     |

|    | 1      | 1      | 1       | 1     | V <sub>dc</sub> |     |

|    | 1      | 1      | 1       | 0     | $3V_{dc}/4$     |     |

|    | 1      | 1      | 0       | 0     | $V_{dc}/2$      |     |

|    | 1      | 0      | 0       | 0     | $V_{dc}/4$      | _   |

|    |        |        |         |       |                 |     |

Appropriate Switching State Selection to Avoid Capacitor Imbalance in Five-Level NPC (K.Narasimha Raju)

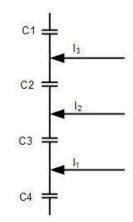

Figure 2. DC bus capacitors and their junction currents

As shown in Figure 2 I1,I2,I3 represents the average values of the currents entering the capacitor junctions.

# 3. BALANCING STRATEGY

The Underlining principle in maintaining balance of DC capacitor voltages is by making average capacitor junction currents zero. Figure 3 shows junction currents waveforms.

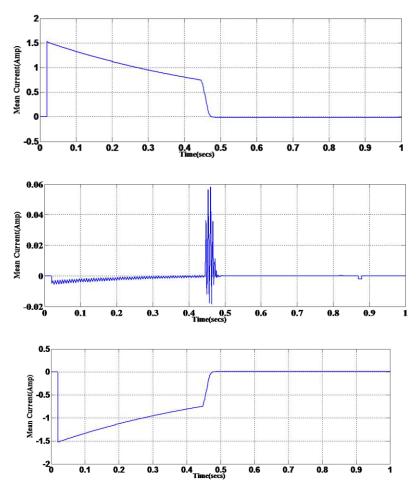

Figure 3. Junction currents waveforms

When the average currents of the capacitor junctions are maintained at zero, saturation of capacitor voltages can be avoided [7]. As shown in Figure 3 the average capacitor junction currents are non-zero when a conventional sine PWM technique (IPD) is applied to a 5-level clamped converter. The non-zero capacitor junction currents lead to saturation of capacitor voltages [2]. This in-turn reduces the level of inverterfrom five to three.

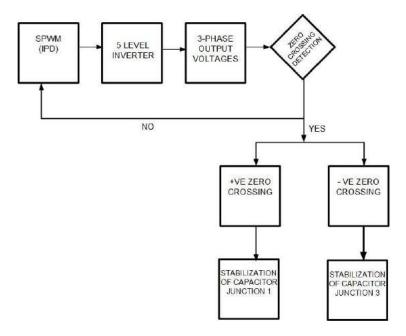

Figure 4. Flow chart of the proposed control logic

| _ | Table  | Table 2. Appropriate switching state selection |          |                 |                 |  |  |  |

|---|--------|------------------------------------------------|----------|-----------------|-----------------|--|--|--|

|   | States | $V_{c1}$                                       | $V_{c2}$ | V <sub>c3</sub> | V <sub>c4</sub> |  |  |  |

|   | 433    | disch                                          | ch       | ch              | ch              |  |  |  |

|   | 100    | ch                                             | ch       | ch              | disch           |  |  |  |

|   | 231    | ch                                             | ch       | disch           | ch              |  |  |  |

|   | 104    | disch                                          | disch    | disch           | ch              |  |  |  |

|   | 214    | disch                                          | disch    | ch              | ch              |  |  |  |

| _ | 322    | ch                                             | disch    | ch              | ch              |  |  |  |

Table 2. Appropriate switching state selection

The block diagram of the proposed technique is shown in Figure.4 as per the novel modulation technique proposed carrier PWM is applied to meet the load demand and at zero crossings of the reference appropriate switching state is applied to balance the capacitor voltages. The appropriate switching state is selected based on capacitor voltage difference, the switching state is selected to discharge the overcharged capacitor and charge the undercharged capacitor. This is done with the help of suitable application of states shown in table from available 125 states, these states injects opposite current into each capacitor junction making the average current zero [6]. This controlling is done only at zero crossings of three phase output voltage for about 1carriercycle. The selection of control during zero crossings reduces distortion in output voltage [5]. Application of control technique other than zero crossing might increase the distortion in output. The stabilization of these capacitor junctions makes the neutral point balanced.

The control technique to avoid the saturation of capacitor voltages is done only during the zero crossings. For the time period other than zero crossings, a conventional carrier PWM (IPD) is applied. The balance of capacitor junction-1 is done during the positive zero crossings for about 1 carrier cycle. Similarly during the negative zero crossings junction 2 is balanced by injecting current of opposite polarity [3]. This makes the capacitors changing their behaviour i.e. charging to discharging or discharging to charging. The injection of current into capacitor junctions is done with the help of following states represented in the Table.3.

Appropriate Switching State Selection to Avoid Capacitor Imbalance in Five-Level NPC (K.Narasimha Raju)

# 4. **RESULTS AND ANALYSIS**

To evaluate the proposed technique a 5-level NPC inverter supplied from a 1000V DC source supplying unity power factor load is taken. It has been supplied with conventional carrier PWM, proposed PWM technique and observations have been made.

## 4.1 Carrier based PWM (CBPWM)

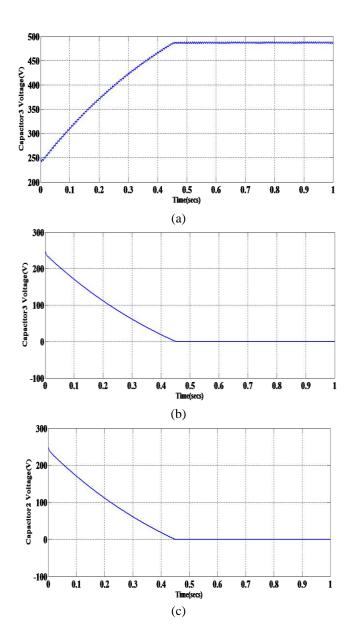

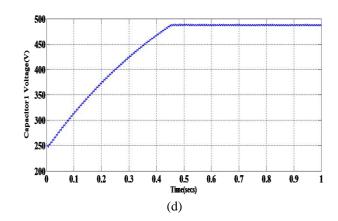

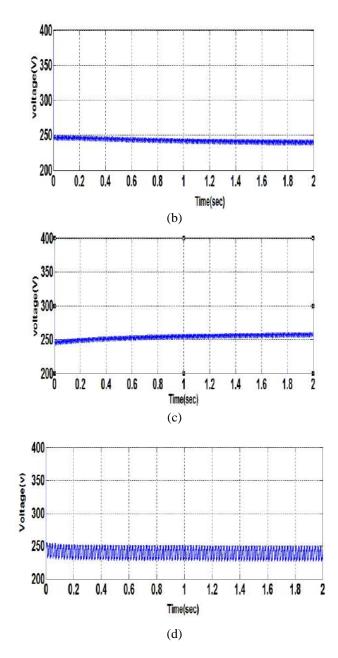

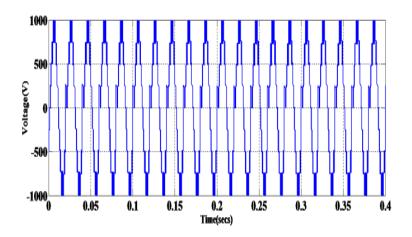

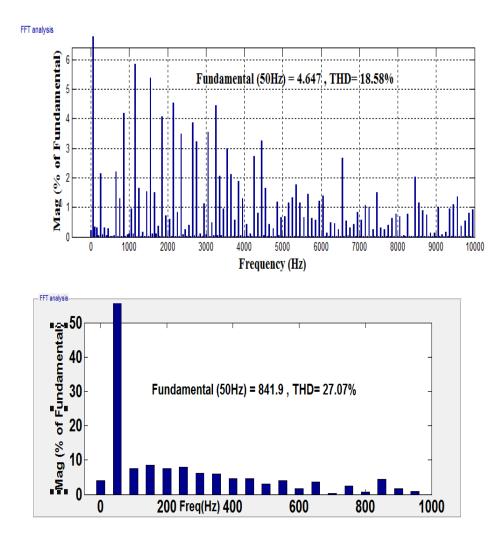

This paper employs in-phase disposition with modulation index=1and frequency modulation ratio 21 to demonstrate the saturation of capacitor voltages. From Figure 5 it can be observed that the outer capacitors get overcharged to twice the intended voltage and the inner capacitors are discharged to zero voltage. Figure 6 shows the output phase voltages which approach three-level after the capacitors get saturated. Figure 7 shows the Fast Fourier transform of output waveform indicating its harmonic profile.

Figure 5 Capacitor voltages with conventional carrier PWM technique a) C1 b) C2 c) C3 d) C4

## 4.2. Proposed Control technique

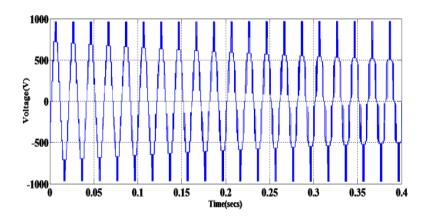

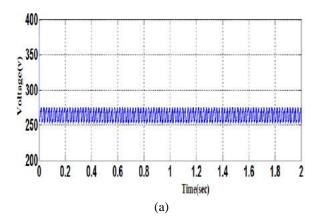

The proposed control technique is applied by following the block diagram illustrated in Figure 4. The Figure 7 shows that the capacitors share the voltage equally and the unbalance in capacitor voltage can be avoided by employing the proposed technique. Figure 8 shows the output phase voltage, the five-levels in output can be observed with some distortion. Figure 9 shows the FFT of the output with proposed technique, It can be observed there is slight increase in THD. This increase in THD can be attributed to application of Space vector to neutralize the capacitor voltage difference.

Figure 6 Output phase voltages

Appropriate Switching State Selection to Avoid Capacitor Imbalance in Five-Level NPC (K.Narasimha Raju)

Figure 7 Capacitor voltages with proposed PWM technique a) C1 b) C2 c) C3 d) C4

Figure 8 Output phase voltages

Figure 9 Output phase voltages THD with (a)Conventional CBPWM (b)Proposed PWM

Appropriate Switching State Selection to Avoid Capacitor Imbalance in Five-Level NPC (K.Narasimha Raju)

# 5. CONCLUSION

Despite of many applications of Five-Level inverter in Medium and high power range, its usage is limited due to unbalance in capacitor voltages. Techniques were proposed in literature to solve this problem, but these techniques either used external circuitry like dc-dc converters in place or used front end converters. But there isn't a control technique which provides an inherent solution to this problem. This paper attempts to find a solution to this problem, a novel control technique to this problem for five-level inverter has been proposed. It can be observed from the results that the capacitor saturation problem is solved but with slight increase in THD.

## REFERENCES

- [1]. A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clampe PWM inverter," IEEE Trans. Ind. Appl.,,vol. IA-17, no. 5, pp. 518523, Sep./Oct. 1981.

- [2]. Nikola Celanovic, and Dushan Boroyevich,"A Comprehensive Study of Neutral-Point Voltage BalancingProblem in Three-Level Neutral-Point-Clamped Voltage Source PWM Inverters" IEEE trans. power elec.,vol. 15, no. 2, march 2000

- [3]. I. Georgios Orfanoudakis, A. Yuratich, and Suleiman M. Sharkh "Hybrid Modulation Strategies for Eliminating Low-Frequency Neutral-Point Voltage Oscillations in the Neutral-Point-Clamped Converter", IEEE trans. power elec., vol. 28, no. 8, august 2013

- [4]. Jose Rodriguez, Steffen Bernet, Peter K. and Ignacio E. Lizama "A Survey on Neutral-Point-Clamped Inverters" IEEE Trans. Ind. Electron., vol. 57, no. 7, july 2010

- [5]. J. Pou, D. Boroyevich, and R. Pindado, New feedforward space-vector PWM method to obtain balanced AC output voltages in a three-level neutral-point-clamped converter, IEEE Trans. Ind. Electron., vol. 49,no. 5, pp. 10261034, october. 2002.

- [6]. M. Tallam, Rangarajan, Rajendra Naik, and Thomas A. Nondahl,"A Carrier-Based PWM Scheme for Neutral-Point Voltage Balancing in Three-Level Inverters" IEEE Trans. Ind. Appl., vol. 41, no. 6, november/december 2005.

- [7]. "Voltage Balancing Control of Diode-Clamped Multilevel Recti\_er/Inverter Systems", Zhiguo Pan, Stu- dent Member, IEEE, Fang Zheng Peng, Fellow, IEEE, KeithA.Corzine, Member, IEEE, Victor R. Stefanovic, Fellow, IEEE, John M. (Mickey) Leuthen, Member, IEEE, and Slobodan Gataric, Member, IEEE

- [8]. Muhammad Jamil ,"Comparison of Multilevel Inverters for the Reduction of Common Mode Voltage "

- International Journal of Power Electronics and Drive System (IJPEDS), Vol. 3, No. 2, June 2013, pp. 170 178 [9]. K Narasimha Raju, M Rao, M Ramamoorthy. (2015), "Hybrid modulation technique for neutral point clamped

- inverter to eliminate neutral point shift with minimum switching loss' " TENCON conf. 2015, pp.1-6. [10]. Till Boller, Joachim Holtz, and Akshay K. Rathore. ,"Neutral-Point Potential Balancing Using Syn-chronous

- Optimal Pulsewidth Modulation of Multilevel Inverters in Medium-Voltage High-Power AC Drives " IEEE Transactions on Industrial Applications , 2014 Vol. 50, No. 1, PP.549-557.

# **BIOGRAPHIES OF AUTHORS**

Is Research scholar in the department of Electrical and Electronics Engineering, K L University, Guntur, Andhra Pradesh, India. He received B.Tech degree in Electrical and Electronics Engineering from DMSSVH College of Engineering and Technology, Machilipatnam,affiliated to JNTU University Hyderabad, Andhra Pradesh, India in June 2002 and Masters (M.Tech) in Power Electronics and Drives from JNTU College of Engineering, Hyderabad, India in May 2012. He is currently working as Assoc. Prof in K L University in Electrical and Electronics Engineering. His research interest includes Power Electronics and Drives, Power Converters.

Is currently the Professor and Head of EEE Department. He had worked in different capacities in technical institutions of higher learning for a period of over ten years. He obtained B.Tech. and M.Tech. degrees from JNT University, Hyderabad. Dr. O. Chandra Sekhar obtained Ph.D. in the year 2014 from JNT University, Hyderabad in the area of Modulation and Control of Multi-Level Inverter- Fed Direct Torque Control of Induction Motor Drives. He has over 25 publications in International and National Journals/Conferences. He received prestigious young scientist award from SERB/DST. His current research interests are in Multi-Level Inverters, FACTS Controllers, Micro Grids and Smart Grids.

M. Ramamoorty (LF) is a Chancellor of KL University, Vijayawada and Distinguished Visiting Professor in the Department of Electrical Engineering, IIT Kanpur, India. He was a Common Wealth Fellow at Toronto University Canada, Professor in the Department of Electrical Engineering, IIT Kanpur, India, Chief of Research at ABB Ltd Baroda, Director General of CPRI Bangalore and Director ERDA Vadodara. His research interests include applications of

power electronics in utilities and industries, power system protection, electrical machines, power quality improvement, fault detection in machines, etc. He is a Life Fellow of the IEEE, Fellow of INAE (India) and distinguished IEEE lecturer