ISSN: 2088-8694, DOI: 10.11591/ijpeds.v10.i3.pp1133-1140

# A novel single-phase PWM asymmetrical multilevel inverter with number of semiconductor switches reduction

S. Kakar, S. M. Ayob, N. M. Nordin, M. S. Arif, A. Jusoh, N. D. Muhamad School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia, Malaysia

#### **Article Info**

# Article history:

Revised Feb 22, 2019 Accepted Mar 3, 2019

# Keywords:

Asymmetric Multilevel inverter Phase-disposition PWM Switching frequency Voltage stress

#### ABSTRACT

In this paper, a new asymmetrical multilevel inverter topology (MLI) is proposed with the objectives of using decreased number of semiconductor switches, dc voltage sources, gate driver circuits and dc links. The structure of presented MLI is very simple and modular. The fundamental module of this structure consists of nine semiconductor switches (eight unidirectional and one bidirectional) and four asymmetrical configured DC sources (ratio of 1:2), which can generate 13-level output voltage. To validate the design, a Matlab-Simulink based model is developed. For this paper, a Sinusoidal Pulse Width Modulation (SPWM) is deployed as the switching strategy of the proposed MLI. The circuit model is simulated under pure resistive and inductive loads. It will be shown that the circuit performs well under both loads. Comparison with traditional MLIs and other recently introduced MLIs will be conducted to show the superiority of the proposed MLI in terms of reduced number of devices and lower voltage stress across the switches.

Copyright © 2019 Institute of Advanced Engineering and Science.

All rights reserved.

1133

# Corresponding Author:

S. M. Ayob, School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia, Skudai, 81310 UTM Skudai, JOHOR, Malaysia. Email:shahrin@fke.utm.my

# 1. INTRODUCTION

Multilevel inverters (MLI) are gaining more attention in industry and academia due to their performance superiority over traditional two-level inverter in terms of high power quality, lower voltage/current harmonics, and lower voltage stresses on switches. The MLI are used in various applications such as renewable energy sources [1-3], distributed generations and high voltage direct current [4, 5], electrical motor drives[6, 7], active power filters [8], electrical vehicle, micro-grid[9], distribution static compensator [10] and flexible alternating current transmission devices [11, 12].

The traditional MLI circuit are the cascaded H-bridge MLI, neutral-point clamped [13] and flying-capacitor clamped MLI [14]. Among them, the cascaded H-bridge MLI receives wider attention in practice due to its simplicity of control and modularity in structure. The idea of MLI circuit was first introduced by Baker and Bannister [15] in 1970s by describing a converter topology that is able to produce staged-output voltage that resembles a sinusoidal waveform by connecting several H-bridge inverters in cascaded fashion. The neutral-point clamp was presented by Baker in 1980. This topology uses clamping diodes to clamp the switch voltage from a single dc source [13]. The flying-capacitor MLI [14] was proposed by T.Meynard in 1992. The topology has identical structure with the former topology but uses clamping capacitors instead of clamping diodes.

For MLI, higher number of output voltage level generation is desirable to improve the harmonics profile of the output voltage. Moreover, it can reduce the size of the output filter. However, it was known that MLI requires more components if extended for higher voltage levels production. This can lead to overall system to be costly, bulky and reliability is reduced. To overcome this limitation, research on reduced device

count MLI topologies are gaining momentum. Several promising topologies have been introduced in recent years [16-21]. Generally, the MLI topologies can be categorized under two groups, namely the symmetrical topologies, where all dc sources are have equal magnitudes and asymmetrical topologies, where dc voltage sources have distinct voltage ratios. The former type of topology is preferred since it can produce higher number of output voltage level using the same amount of devices. Several number of asymmetrical MLI topologies have been proposed in [22-27]. In [28] new multilevel inverter topology known as packed U-cell (PUC) is presented. This topology consists of packed U-cell where each cell is comprised of two semiconductor devices and a dc voltage source.

In this paper, a new multilevel inverter with the objective to reduce the number of components count is proposed. It uses a nine switches and four assymetric dc sources to generate 13-level of output voltage. The proposed topology model will be developed via Matlab-Simulink software and simulate under different type of load to validate its viability. The sinusoidal pulse width modulation (SPWM) strategy will be deployed as the switching strategy for the proposed MLI. From the result, the proposed MLI performs well under inductive load.

#### 2. PROPOSED TOPOLOGY

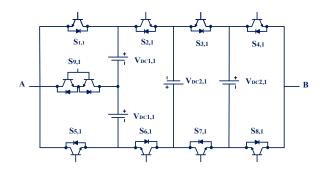

In this paper, a new MLI with reduced device count is proposed. Fundamental unit of the proposed MLI topology is shown in Figure 1. It comprises of eight unidirectional S<sub>1</sub> to S<sub>8</sub>, one bidirectional switch S<sub>9</sub> and four voltage sources. The unidirectional switches consist of an IGBT and an antiparallel diode. The bidirectional switch consists of two IGBTs, two diodes and a gate driver circuit. An anti-parallel diode is used to conduct current in both directions and block voltage in one direction.

Figure.1 Fundamental block of the proposed MLI topology

|            | Table 1. Switching states for 13-level MLI |       |       |       |       |       |       |       |       |       |                       |

|------------|--------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|

|            | States Switch states V <sub>0</sub>        |       |       |       |       |       |       |       |       |       |                       |

|            | States                                     | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ | $S_8$ | $S_9$ | <b>v</b> <sub>0</sub> |

|            | 1                                          | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1V                    |

|            | 2                                          | 1     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 0     | 2V                    |

| Positive   | 3                                          | 0     | 0     | 1     | 1     | 0     | 1     | 0     | 0     | 1     | 3V                    |

| levels     | 4                                          | 1     | 0     | 1     | 1     | 0     | 1     | 0     | 0     | 0     | 4V                    |

|            | 5                                          | 0     | 0     | 1     | 0     | 0     | 1     | 0     | 1     | 1     | 5V                    |

|            | 6                                          | 1     | 0     | 1     | 0     | 0     | 1     | 0     | 1     | 0     | 6V                    |

| Zero level | 7                                          | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0V                    |

|            | 8                                          | 0     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 1     | -1V                   |

|            | 9                                          | 0     | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | -2V                   |

| Negative   | 10                                         | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | -3V                   |

| levels     | 11                                         | 0     | 1     | 0     | 0     | 1     | 0     | 1     | 1     | 0     | -4V                   |

|            | 12                                         | 0     | 1     | 0     | 1     | 0     | 0     | 1     | 0     | 1     | -5V                   |

|            | 13                                         | 0     | 1     | 0     | 1     | 1     | 0     | 1     | 0     | 0     | -6V                   |

Magnitude of the two DC input voltage sources is  $V_1$  each and the other two sources has magnitude of  $V_2$  each as shown in (1) and (2). The fundamental unit is capable to produce thirteen voltage levels in the output. To avoid short-circuit of dc voltage inputs, simultaneous conduction of switch pairs  $(S_1, S_9)$   $(S_5, S_9)$   $(S_2, S_6)$   $(S_3, S_7)$  and  $(S_4, S_8)$  should be avoided. Switching states to produce 13-level output voltage are shown in Table 1.

$$V_1 = 1V_{DC}; (1)$$

$$V_2 = 2V_{DC}; (2)$$

This voltage source configuration can produce thirteen voltage levels of 0V,  $\pm 1V_{DC}$ ,  $\pm 2~V_{DC}$ ,  $\pm 3~V_{DC}$ ,  $\pm 4~V_{DC}$ ,  $\pm 5~V_{DC}$  and  $\pm 6~V_{DC}$  in the output.

#### 2.1. Total voltage stress

One of important parameter in evaluating the performance of the MLI topologies is the total voltage stress (TVS) of topology. It is desirable to obtain low TVS since it also reflects the development cost of the topology. Higher TVS, meaning that one need to use switch that has high blocking voltage capability, which normally expensive to procure [22]. The blocking voltage of the semiconductor switch is the total voltage stress to withstand in its off-state. The maximum blocking voltage by each switch in proposed topology can be obtained through (3)-(7).

$$V_{S1} = V_{S5} = 1V_{DC} + 1V_{DC} = 2V_{DC};$$

(3)

$$V_{S3} = V_{S7} = 2V_{DC} + 2V_{DC} = 4V_{DC};$$

(4)

$$V_{S9} = 2V_{DC}; (5)$$

$$V_{S4} = V_{S8} = 2V_{DC} + 2V_{DC} = 4V_{DC};$$

(6)

$$V_{S2} = V_{S6} = 1V_{DC} + 1V_{DC} + 2V_{DC} = 4V_{DC};$$

(7)

Therefore, Total voltage stress (TVS) of all the semiconductor switches utilized in fundamental block can be calculated by adding all the blocked voltages as shown in (8).

$$TVS = V_{S1} + V_{S2} + V_{S3} + V_{S4} + V_{S5} + V_{S6}$$

$$V_{S7} + V_{S8} + V_{S9} = 2V_{DC} + 4V_{DC} + 4V_{DC} + 2V_{DC} + 4V_{DC} + 2V_{DC} + 2V_{DC} + 2V_{DC} + 2V_{DC}$$

$$TVS = 26V_{DC};$$

(8)

# 2.2. Extention to n-level output voltage

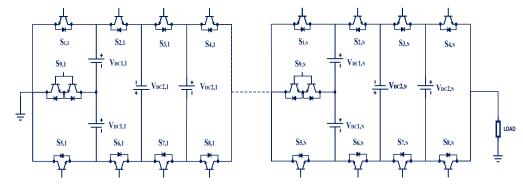

Fundamental unit of the proposed topology can be easily cascaded to generate higher number of output voltage levels. Figure 2 depicts the generalized circuit of the presented topology for n-level output. The cascaded structure is able of produce higher number of level with suitable DC source selection. The number of levels of the output voltage waveform for n blocks structure can be determined using equation (9). Term (10) and (11), represent the maximum output voltage for n units and the total number of IGBTs required, respectively.

$$N_L = 12n + 1; (9)$$

$$V_{o,max} = V_{o,1} + V_{0,2} + V_{0,3} + \dots + V_{o,n};$$

(10)

$$N_{IGBT} = 5(N_L - 1)/6; (11)$$

Figure 2. Generalized structure of MLI topology

#### 3. COMPARISON WITH OTHER TOPOLOGIES

Comparison with the traditionals and recent reduced components MLI topologies is conducted to validate the effectiveness of the proposed MLI. Table 2 summarised the comparison for several MLI topologies for 13-level output voltage. In terms of IGBT counts, it is confirmed that the proposed MLI structure has the least number of IGBT counts. The proposed MLI has the lowest number of TVS as compared to other recent MLI topologies except when comparing with MLI of [16]. However, it should be noted that the MLI proposed in [16] employs H-bridge for polarity reversal. The voltage stress across the switches of the H-bridge are equals to its MLI's output voltage, hence may limit its usage to medium power applications only. As for traditional MLIs, all of them yield TVS of 24, which is lower than the proposed MLI, which is 26. However, the proposed MLI is still considered as a good alternative to the traditional MLIs due to low IGBT counts. The proposed MLI multilevel inverter has higher amount of variety of dc input voltage sources (N<sub>variety</sub>) compared to other mentioned topologies. Higher variety of dc source means that the proposed MLI can be configured as symmetrical of asymmetrical MLI.

| T 11 0   | ~ .        | 1.1 .1     | 101     |                  | 1 .        |

|----------|------------|------------|---------|------------------|------------|

| Table 7  | Comparison | with other | 13-leve | l inwerter t     | Onologies  |

| Table 2. | Comparison | with other | 13-10/0 | i iii v Ci tCi t | CODUIDEICS |

|          |       |         |                      |        |          |              | 0               |

|----------|-------|---------|----------------------|--------|----------|--------------|-----------------|

| Type     | IGBTs | Drivers | N <sub>variety</sub> | Diodes | De links | $TVS*V_{DC}$ | Negative levels |

| CHB      | 24    | 24      | 1                    | 24     | 6        | 24           | With H-bridge   |

| FC       | 24    | 24      | 1                    | 24     | 6        | 24           | Inherent        |

| NFC      | 24    | 24      | 1                    | 24     | 6        | 24           | inherent        |

| MLDCL    | 16    | 16      | 1                    | 16     | 6        | 36           | With H-bridge   |

| ST-Type  | 12    | 9       | 2                    | 12     | 4        | 30           | inherent        |

| [16]     | 14    | 14      | 2                    | 14     | 6        | 24           | With H-bridge   |

| proposed | 10    | 9       | 2                    | 10     | 4        | 26           | inherent        |

#### 4. DESIGN OF SIMULATION MODEL

To validate the performance of proposed MLI topology, simulations are performed using computer software tool Matlab/Simulink. Simulation model of the proposed fundamental unit is illustrated in Figure 3. The value of the DC sources are configured in the ratio of 1:2. The value for  $V_{dc1,1}=15~V$  while  $V_{dc1,2}=30~V$ , respectively. The simulation model will be tested under different load type. The first test will be for pure resisitive load with  $R=100~\Omega$  and the second test will be an inductive load with  $R=40\Omega$  and L=200~mH.

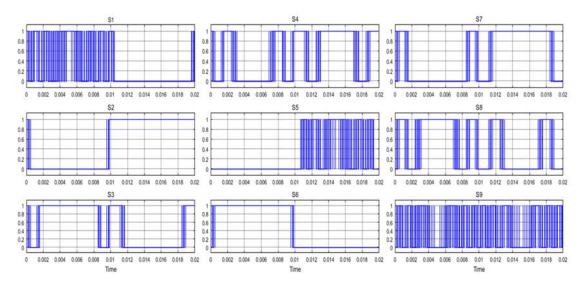

For switching strategy, a multi-carrier based Phase-Disposition sinusoidal pulse width modulation will be deployed for producing the gating signals. Figure 4 shows the PD-PWM waveform diagram. The frequency of the triangular carriers is depends on the switching frequency of the proposed MLI. The number of triangular carriers can be calculated as (12).

Number of carrier =

$$N_L - 1$$

(12)

Sinusoidal reference wave of 50 Hz is compared with all carrier waves to create pulses for switching of devices. Figure 5 shows the gate pulses of the switches  $S_1$  to  $S_9$  for 13-level MLI. The triangular carrier frequency is 5k Hz.

Figure 3. Simulation model of the proposed multilevel inverter for 13-level voltage generation

Figure 4. Phase disposition PWM waveform generation

Figure 5. Switching pulses for 13-level MLI topology

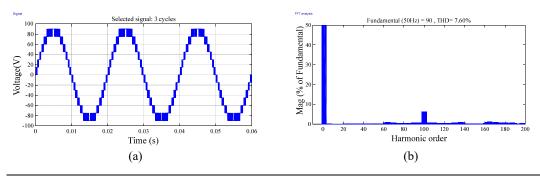

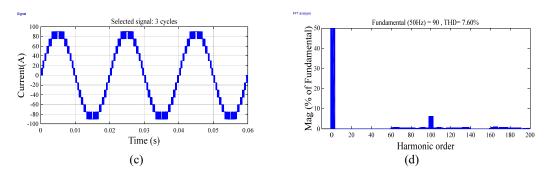

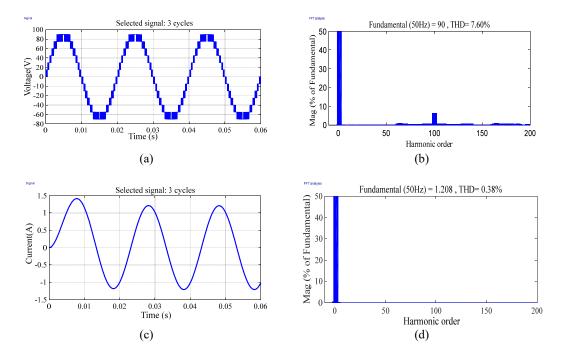

Figures 6(a)–(d) exhibit the output voltage, output current and the hamronics spectrum when connected with R=100  $\Omega$ . As clearly be seen from Figure 6(a), the simulation model is able to produce output voltage of 13-level as expected. The fundamental voltage component is 90 V and the total harmonics distortion is 7.6%. Figures 7(a)–(d) exibit the output voltage, current and the harmonics spectrum when connected with inductive load R=40  $\Omega$  and L=200m H. The total harmonics distortion for voltage and current is 7.6% and 0.38%, respectively. Frequency spectrum for output voltage confirms that the magnitude of each harmonic is less than 5% which meet IEEE519 standards (magnitude of THD is equal to or less than 8% and magnitude of each order harmonic is equal to or less than 5%).

Figure 6. Simulation results of output voltage and current waveform when connected with  $R=100\Omega$ , (a) Output voltage, (b) Output Voltage THD, (c) Output Current, (d) Output Current THD

Figure 7. Simulation results for output voltage and current when connected with inductive load  $R=40\Omega$  and L=200m H, (a) Output voltage, (b) Output Voltage THD, (c) Output Current, (d) Output Current THD

#### 5. CONCLUSION

In this paper, a new multilevel inverter topology utilizing less device count is presented. It can generate 13-level output voltage using nine switches and four asymmetrical DC sources. It can be easily extended for higher number of voltage levels with less number of power devices and decreased voltage stress on semiconductor devices. The main characteristic of the presented topology is that it has the capability to produce all voltage levels without need of H-bridge circuit. A Phase-Disposition PWM switching strategy is employed to generate switching signals for the proposed MLI topology. From the simulation results, it was found that the proposed topology is able to generate 13-level output voltage with low total harmonics distortion.

# ACKNOWLEDGEMENTS

This research is sponsored under Universiti teknologi Malaysia Research University Grant (RUG) Tier 2 (Vote no. 15J40)

#### REFERENCES

- C. Cecati, F. Ciancetta, and P. Siano, "A multilevel inverter for photovoltaic systems with fuzzy logic control," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 12, pp. 4115-4125, 2010.

- [2] P. G. Barbosa, H. A. C. Braga, M. d. C. B. Rodrigues, and E. C. Teixeira, "Boost current multilevel inverter and its application on single-phase grid-connected photovoltaic systems," *IEEE transactions on power electronics*, vol. 21, no. 4, pp. 1116-1124, 2006.

- [3] X. Yu, C. Cecati, T. Dillon, and M. G. Simoes, "The new frontier of smart grids," *IEEE Industrial Electronics Magazine*, vol. 5, no. 3, pp. 49-63, 2011.

- [4] H. Ding, Y. Zhang, A. M. Gole, D. A. Woodford, M. X. Han, and X. N. Xiao, "Analysis of coupling effects on overhead VSC-HVDC transmission lines from AC lines with shared right of way," *IEEE Transactions on Power Delivery*, vol. 25, no. 4, pp. 2976-2986, 2010.

- [5] S. Li, T. A. Haskew, and L. Xu, "Control of HVDC light system using conventional and direct current vector control approaches," *IEEE Transactions on Power Electronics*, vol. 25, no. 12, pp. 3106-3118, 2010.

- [6] M. Veenstra and A. Rufer, "Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives," *IEEE Transactions on industry applications*, vol. 41, no. 2, pp. 655-664, 2005.

- [7] H. Akagi, "Classification, terminology, and application of the modular multilevel cascade converter (MMCC)," *IEEE Transactions on Power Electronics*, vol. 26, no. 11, pp. 3119-3130, 2011.

- [8] A. Varschavsky, J. Dixon, M. Rotella, and L. Morán, "Cascaded nine-level inverter for hybrid-series active power filter, using industrial controller," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2761-2767, 2010

- [9] M. Hamzeh, A. Ghazanfari, H. Mokhtari, and H. Karimi, "Integrating hybrid power source into an islanded MV microgrid using CHB multilevel inverter under unbalanced and nonlinear load conditions," *IEEE Transactions on energy Conversion*, vol. 28, no. 3, pp. 643-651, 2013.

- [10] S. Srikanthan and M. K. Mishra, "DC capacitor voltage equalization in neutral clamped inverters for DSTATCOM application," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2768-2775, 2010.

- [11] T.-T. Ma, "P-Q decoupled control schemes using fuzzy neural networks for the unified power flow controller," International Journal of Electrical Power & Energy Systems, vol. 29, no. 10, pp. 748-758, 2007.

- [12] L. Liu, P. Zhu, Y. Kang, and J. Chen, "Power-flow control performance analysis of a unified power-flow controller in a novel control scheme," *IEEE transactions on power delivery*, vol. 22, no. 3, pp. 1613-1619, 2007.

- [13] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Transactions on industry applications*, no. 5, pp. 518-523, 1981.

- [14] T. A. Meynard and H. Foch, "Multi-level conversion: high voltage choppers and voltage-source inverters," pp. 397-403: IEEE.

- [15] R. H. 1 Baker, Bannister, L.H., "'Electric power converter'," 1975.

- [16] E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," Energy Conversion and Management, vol. 50, no. 11, pp. 2761-2767, 2009.

- [17] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Transactions on industrial electronics*, vol. 57, no. 7, pp. 2197-2206, 2010.

- [18] J. Dixon and L. Moran, "High-level multistep inverter optimization using a minimum number of power transistors," *IEEE Transactions on Power Electronics*, vol. 21, no. 2, pp. 330-337, 2006.

- [19] R. S. Alishah, S. H. Hosseini, E. Babaei, M. Sabahi, and A. Z. Gharehkoushan, "Optimal design of new cascade multilevel converter topology based on series connection of extended sub-multilevel units," *IET Power Electronics*, vol. 9, no. 7, pp. 1341-1349, 2016.

- [20] M. Sadeghi, S. H. Hosseini, R. Alizadeh, and M. Banaei, "New mixed stacked multicell converter with interesting advantages," *IET Power Electronics*, vol. 5, no. 8, pp. 1298-1304, 2012.

- [21] M. Arif, S. Ayob, and Z. Salam, "Asymmetrical Nine-level inverter topology with reduce power semicondutor devices," TELKOMNIKA (Telecommunication Computing Electronics and Control), vol. 16, no. 1, pp. 38-45, 2018

- [22] E. Babaei, "A cascade multilevel converter topology with reduced number of switches," *IEEE Transactions on power electronics*, vol. 23, no. 6, pp. 2657-2664, 2008.

- [23] E. Babaei, S. Hosseini, G. Gharehpetian, M. T. Haque, and M. Sabahi, "Reduction of dc voltage sources and switches in asymmetrical multilevel converters using a novel topology," *Electric Power Systems Research*, vol. 77, no. 8, pp. 1073-1085, 2007.

- [24] S. Laali, K. Abbaszadeh, and H. Lesani, "A new algorithm to determine the magnitudes of dc voltage sources in asymmetric cascaded multilevel converters capable of using charge balance control methods," in *Electrical Machines and Systems (ICEMS)*, 2010 International Conference on, pp. 56-61: IEEE, 2010.

- [25] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel dc voltage sources," IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2643-2650, 2010.

- [26] M. S. b. Arif, S. M. Ayob, and Z. Salam, "Asymmetrical multilevel inverter topology with reduced power semiconductor devices," in 2016 IEEE Industrial Electronics and Applications Conference (IEACon), pp. 20-25, 2016.

- [27] M. S. B. Arif and S. M. Ayob, "A novel single phase five-level photovoltaic based grid-connected inverter," in 2014 IEEE Conference on Energy Conversion (CENCON), pp. 325-330, 2014.

- [28] Y. Ounejjar, K. Al-Haddad, and L.-A. Grégoire, "Packed U cells multilevel converter topology: theoretical study and experimental validation," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 4, pp. 1294-1306, 2011.

#### **BIOGRAPHIES OF AUTHORS**

Saifullah Khan received B.E. in Electrical Engineering from NED university of Engineering and Technology Karachi Pakistan from 2011 to 2014. Currently he is Pursuing MPhil degree in power electronics from School of Electrical Engineering, UTM Malaysia. His research interest includes power converter topologies and modulation strategies for renewable energy integration.

Shahrin bin Md. Ayob was born in Kuala Lumpur, Malaysia. He obtained his first degree in Electrical Engineering, Master in Electrical Engineering (Power) and Doctor of Philosophy (PhD) from Universiti Teknologi Malaysia in 2001, 2003 and 2009, respectively. Currently he is an associate professor at School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia. He is a registered Graduate Engineer under Board of Engineer Malaysia (BEM) and Senior Member of IEEE (2018). His current research interest is solar photovoltaic system, electric vehicle technology, fuzzy system, and evolutionary algorithms for power electronics applications.

Norjulia Mohamad Nordin received her Bachelor's degree in Electrical Engineering from Universiti Teknologi Malaysia, Johor, Malaysia, in 2006, M. Eng. Sc. Degree in Energy System from The University of New South Wales, Australia, in 2008 and Ph.D from Universiti Teknologi Malaysia (UTM) in 2016. Currently she is a senior lecturer at the Universiti Teknologi Malaysia, Johor, Malaysia. Her research interests are AC and DC drive system, multilevel inverter and wide bandgap based power electronic converter.

M Saad Bin Arif received M. Tech degree in Electrical Engineering with specialization in Power System and Drives and Graduation in Electrical Engineering in 2010 and 2010 respectively. His research area of interest - power electronics, application of power electronics in renewable energy systems, energy systems, and engineering education.

Awang Jusoh was born in Terengganu, Malaysia in 1964. He received his B. Eng. (Hons) from Brighton Polytechnic, UK, in 1988. He obtained his MSc. and PhD. from The University of Birmingham, UK in 1995 and 2004, respectively. Since 1989, he has been a lecturer at Universiti Teknologi Malaysia and is now an Associate Professor at the Department of Power Engineering, School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia, Malaysia. His research interests include all areas of power electronics systems and renewable energy.

Nik Din Muhamad is currently a Senior Lecturer at School of Electrical Engineering, Universiti Teknologi Malaysia. He has experience in teaching and researc for over than 20 years. His current research interest is dc-dc converter design, LED driver technology, converter modelling and feedback control design for power electronics converter.