Vol. 11, No. 4, December 2020, pp. 1866~1871

ISSN: 2088-8694, DOI: 10.11591/ijpeds.v11.i4.pp1866-1871

# A narrative 3-phase 9-level voltage source inverter

# M. Selvaperumal<sup>1</sup>, D. Kirubakaran<sup>2</sup>

<sup>1</sup> Department of Electrical and Electronics Engineering, Sathyabama University, India. <sup>2</sup> Department of Electrical and Electronics Engineering, St. Josph's Institute of Technology, India.

# **Article Info**

### Article history:

Received Dec 4, 2019 Revised Feb 22, 2020 Accepted Jun 18, 2020

### Keywords:

Bidirectional switches MATLAB Simulink Multilevel inverters

# **ABSTRACT**

A tale technique for a 3-stage nine-level voltage source inverter utilizing sixteen switches is presented. The given system utilizes ordinary 3-stage scaffolds of two-level as a diode braced model. A DC interface voltage is provided so that the fell H-connect produces the nine voltage levels. The exchanging designs are expressed as the levels expand then the example is hard to create three-stage yields with key balance procedures. Here an answer for an a-level inverter to create required voltage-level with less power electronic parts by setting up in the look-into tables. This investigation diagrams the correlations between nine-level voltage source inverters in various arrangements and proposed novel, sixteen switch three-stage inverter structured with a smaller number of intensity electronic parts and reenacted in MATLAB/Simulink.

This is an open access article under the CC BY-SA license.

1866

### Corresponding Author:

M. Selvaperumal, Research scholar, Department of Electrical and Electronics Engineering, Sathyabama University Chennai, India.

Email: ponselva.eee@gmail.com

#### 1. INTRODUCTION

The standard voltage source inverter connects with the blend of sinusoidal yield voltage from two or three periods of voltages. The word, astounded has begun with the three-level converter looked for after by changed dazed converter topologies. A wide degree of topologies and control strategies appear in the forming [1-3]. A heap of astonishing inverter modules is normal for accomplishing low DV/DT characteristics, low exchanging misfortunes low sounds in the yield voltage, and present and better electromagnetic impedance. Taking into account a few decent conditions, dazzling inverters have been applied in different application fields [4-8]. The fell staggered inverter is made by various single-organize Hpartner inverters and is mentioned into symmetric and Topsy turvy dependent on the essentials of the DC voltage sources. In the symmetric flabbergasted inverter, the proportions of the DC voltages are a relative while, the lopsided paralyzed inverter, the estimations of the DC voltages are clashing. Beginning late, Hilter kilter astounded inverter and mix multistage topologies are getting one of the most intriguing examination zones. This topology diminishes the expense and size of the inverter and improves relentlessness since the base number of power electronic segments, capacitors, and DC supplies utilized. The half and half multistage converters include diverse dazzling game-plans with clashing DC voltage supplies. With such converters, unquestionable change strategies, and force electronic parts advances are required [9-15]. Regardless, the clarification behind improving the presentation of the standard single and three-compose inverters, various topologies utilized with various sorts of bidirectional switches has introduced. By separating the unidirectional and bidirectional switches, a bidirectional switch can lead the current and withstanding the voltage in two-habits. For accomplishing the higher voltage levels, bidirectional switches with a fitting evening out framework can improve the showcase of voltage source inverter to the degree, reducing the semi-conductor parts and limiting the withstanding voltages. In the context of the particular foundation, this paper endorses a novel topology for a three-arrange nine-level voltage source inverter with sixteen switches. In addition, an extended structure for N-level is appeared and inspected by changed gliding topologies [16-26].

### 2. PROPOSED METHOD

### 2.1. Modeling

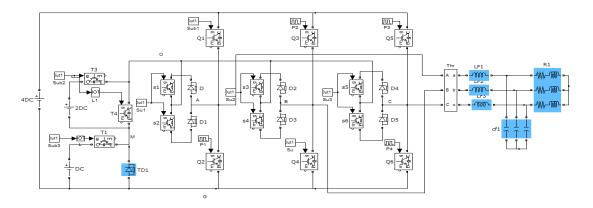

The proposed nine-level voltage source inverter contains three-bidirectional switches (S1-S6), two diodes (Da1-Da2), are added to the standard three-compose two-level growth (Q1-Q6) as appeared in Figure 1. The restriction of these bidirectional switches is to forestall the higher voltage and ease the current stream to and from the midpoint (o). As such, VSI is bolstered with a fixed voltage of 4Vdc and two fell systems are continuing with clashing voltages Vdc and 2Vdc are connected with (+, -, o) terminals. Accordingly, the demonstrated VSI is endeavored to convey nine relative and specific voltage levels, the force circuit of the fell H-partner utilizes two approaches cells having clashing voltage supplies. In every cell, two switches are turned On and OFF under changed conditions to yield two voltage levels.

Figure 1. Circuit diagram for proposed sixteen switch nine-level voltage source inverter

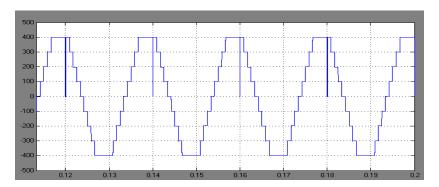

A title of the article ought to be the least potential words that precisely with contrasting voltages Vdc,2Vdc,3Vdc,4Vdc.0-Vdc,-2Vdc, The essential cell dc voltage gracefully Vdc is consolidated if switch T1 is turned ON inducing Vmg=Vdc where Vmg is the voltage at the middle point (m)with regard to inverter ground (g)or dodge if switch T2 is turned ON driving toVmg= 0. Also, the second cell dc voltage flexibly 2Vdc is joined when switch T3 is turned ON happening in Vom=+2Vdc where Vom is the voltage at the midpoint (o) concerning focus (m) or circumvent when switch T4 is turned ON coming about compensation=0. The pinnacle voltage rating of the switches of the standard two-level growth (Q1–Q6) is 4Vdcwhereas the bidirectional switches (S1–S6) have a peak voltage rating of 3Vdc.InCHBcells, the summit voltage rating of second cell switches (T3 and T4) is2Vdc while the zenith voltage rating of T1 and T2 in the basic cell is Vdc. By preeminent Vab, Vbc, Vca with relating voltages Vdc,2Vdc,3Vdc,4Vdc.0-Vdc,-2Vdc,-4Vdc as appeared in Figure 2.

The sensible weight voltages can be practiced if the proposed inverter chips away at the trading states depicted in Table 1. The inverter may incorporate 24 unmistakable modes inside a pattern of the yield waveform. The inverter line-to-line voltage waveforms Vab, Vbc, and Vca with relating trading door signals are portrayed in Table 1.

$$\begin{bmatrix} v_{ab} \\ v_{bc} \\ v_{ca} \end{bmatrix} = \begin{bmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \\ -1 & 0 & 1 \end{bmatrix} * \begin{bmatrix} v_{ag} \\ v_{bg} \\ v_{cg} \end{bmatrix}$$

(1)

1868 ISSN: 2088-8694

Figure 2. Simulated waveforms of Vab, Vbc, Vca

Table 1. Lookup tables sequence of the proposed nine-level innverter

| S   | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | S1 | S2 | S3 | S4 | S5 | S6 | T1 | T2 | T3 | T4 | VA | VB | VC |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| t1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 4  | 0  | 0  |

| t2  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 4  | 1  | 0  |

| t3  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 4  | 2  | 0  |

| t4  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 4  | 3  | 0  |

| t5  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 4  | 4  | 0  |

| t6  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 3  | 4  | 0  |

| t7  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 2  | 4  | 0  |

| t8  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 4  | 0  |

| t9  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 4  | 0  |

| t10 | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 4  | 1  |

| t11 | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 4  | 2  |

| t12 | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 4  | 3  |

| t13 | 0  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 4  | 4  |

| t14 | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 3  | 4  |

| t15 | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 2  | 4  |

| t16 | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 4  |

| t17 | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 4  |

| t18 | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 4  |

| t19 | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 2  | 0  | 4  |

| t20 | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 3  | 0  | 4  |

| t21 | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 4  | 0  | 4  |

| t22 | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 4  | 0  | 3  |

| t23 | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 4  | 0  | 2  |

| t24 | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 4  | 0  | 1  |

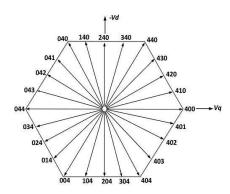

It is important that every reenacted waveform is gotten at t1=t2=•••=t24=0.02/24 s. So as to plot the space vector graph of the proposed inverter in a stationary d-q reference outline, the accompanying conditions can be utilized to determine d and q voltage parts for all inverter vectors:

$$V_d = \frac{4V_{dc}}{\sqrt{3}(N-1)} (S_c - S_b)$$

(2)

$$V = V_q - JV_d$$

(3)

$$V = V_0 - JV_d \tag{3}$$

Percentage of t total harmonic distortion determined the valve

$$THD\% = \frac{\sqrt{\sum_{k=2}^{\infty} V_k^2}}{V_1} * 100\% \tag{4}$$

#### SWITCHING ALGORITHM **3.**

The carrier based is the least complex tweak procedure for inconsistent voltage sources. Bearer with Selective symphonious is the most widely recognized regulation strategy used to control the central yield voltage just as to dispose of the unwanted consonant segments from the yield voltages. Notwithstanding, an iterative technique, for example, the Newton-Rapson strategy is typically used to discover the answers for (N-1) nonlinear supernatural conditions. The troublesome figurings and the requirement for an elite controller for the genuine application are the fundamental impediments of such a technique.

Thusly, an elective procedure is proposed to convey the inverter's exchanging door signals. It is less perplexing to control the proposed inverter and accomplish the basic yield voltage waveforms to the degree Sa, Sb, and Sc as appeared Figure 3. The reason of the proposed strategy can be explained as seeks after: For a given estimation of parity record Ma and inside a full cycle of the activity of the proposed inverter, the exchanging states Sa, Sb, and Scare picked immediately.

Figure 3. Exchanging states vectors of the proposed DC to ac in d-q reference outline

### 4. EXTENDED STRUCUTRE

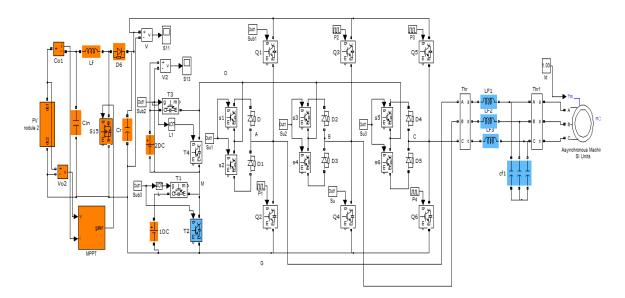

We can see that there is a likelihood to land at a yield voltage with a higher number of steps in the proposed voltage source inverter by consolidating fell H-partner in a course of action as appeared in Figure 4.

So as to accomplish the ideal number of voltage levels, going with a framework for the degrees of DC voltage supplies are:

By making the twofold relationship between the DC supplies of the fell h-interface structure as looks for after the MATLAB/Simulink model of the proposed inverter appeared in Fig. 1 has been made to consider conduction and exchanging impact difficulties. The proposed inverter is relied upon to pass on a yield power of Pout=1890watts. Three-sort out a strategy resistive–inductive (230hm–3 mH/Phase) in star alliance is utilized as a store. The stunned DC-interface is settled as Vdc=75 V, 2Vdc=150 V, and V cons=4Vdc=300 V and the proposed transport change structure at Ma=1 is acknowledged to make the most ideal exchanging entry signals. Three specific sorts of semiconductor parts are picked to make the model of the proposed inverter control circuit as following: IGBT (HGTG20N60B3D) 600 V/40 A for the two-level Bridge and CHB switches, IGBT (IRG4BC40W) 600 V/20 A for bidirectional switches, and Diode (RHRP1540) 440 V/15 A for installed diodes in bidirectional switches and freewheeling diodes.

Figure 4. Circuit graph of the proposed three-stage N-level voltage source inverter.

1870 □ ISSN: 2088-8694

#### 5. COMPARISION STUDY

In view of the examination conveyed among the proposed technique, the accompanying perceptions are taken. Compared to every one of the perspectives, the proposed three-stage voltage source inverter requires fewer power gadgets segments and less size with low voltage taking care of pressure Then again, the voltage and current examinations of the force portions influence the cost and affirmation of the voltage source inverter. Tolerating that all force parts have a comparable current rating which is then assessed current of the store (IL), the voltage examinations of these fragments depend upon the significance of DC voltage supplies, voltage stress, and structure of the inverter.

Considering that all inverters have a comparable data DC-interface which ascends to (N-1) Vdc. The proposed inverter is expected to pass on a yield power of Pout=1900WATTS.3-stage course of action R-L (23ohm-3 millihentry/Phase) in star affiliation is used as a store. The amazed DC-associate is settled as Vdc=75V, 2Vdc=150V, and Fix=4 Vdc=300V and the proposed transporter balance procedure at Modulation index=1 is executed to make the fitting trading entryway signals. Three extraordinary sorts of semiconductor parts are picked to collect the proposed inverter control circuit as following: Insulated gate bipolar transistor(HGTG20N60B3D) .600 V/40 A for the two-level Bridge and CHB switches, IGBT (IRG4BC40W) 600 V/20 A for bidirectional switches, and Diode (RHRP1540) 440 V/12A for introduced diodes in bidirectional switches and freewheeling diodes.

Table 2. Comparison of inverters with the proposed inverter

| Topology                     | Clamped Diodes | Flying Capacitors | Cascaded H-bridge | Proposed |

|------------------------------|----------------|-------------------|-------------------|----------|

| Power Semiconductor Switches | 48 S           | 48 S              | 48 S              | 16S      |

| Clamped Diodes three phases  | 8              | 0                 | 0                 | 12       |

| DC bus capacitor             | 8              | 8                 | 4                 | 3        |

| Balancing capacitors         | 0              | 28                | 0                 | 0        |

| Voltage unbalance            | Average        | High              | Very small        | Small    |

#### 6. CONCLUSION

In this paper, a novel control system proper for high force low trading repeat sixteen switches three-phase nine-level inverter is introduced. So as to limit the exchanging gadgets diverse voltage sources as designed by connect circuits and clasped by the diode. Along these lines, the proposed topology brings about a decrease in establishment territory and cost. The central recurrence adjustment was easily utilized and demonstrated high versatility and ease in control. Likewise, the proposed system was connected with N-level with different procedures. The proposed topology was contrasted and the various types of methods in writing from various perspectives. As per the examination results, the proposed topology requires a lesser number of power diodes, IGBTs, driver circuits, and DC voltage sources. The introduction precision of the proposed sixteen switches three-phase nine-level inverter was confirmed through the MATLAB recreation.

#### REFERENCES

- [1] Mohsen Aleenejad, Seyyedmahdi Jafarishiadeh, Hamid Mahmoudi, Reza Ahmadi, "Reduced number of auxiliary H-bridge power cells for post-fault operation of three phase cascaded H-bridge inverter," *IET Power Electronics*, vol. 12, no. 11, pp. 2923-2931, Aug. 2019.

- [2] M. Selvaperumal, D. kirubakaran, "PV Based Asymmetrical Cascade Three Phase Nine Level Multi Level Inverter Fed Induction Motor," *International Journal of Engineering and Advanced Technology*, vol. 8, no. 6, 2019.

- [3] Niraj Rana, Mukesh Kumar, Arnab Ghosh, Subrata Banerjee. "A Novel Interleaved Tri-State Boost Converter with Lower Ripple and Improved Dynamic Response," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 7, pp. 5456-5465 2018.

- [4] R. Barzegarkhoo, M. Moradzadeh, E. Zamiri, H. Madadi Kojabadi and F. Blaabjerg, "A New Boost Switched-Capacitor Multilevel Converter with Reduced Circuit Devices," in *IEEE Transactions on Power* Electronics, vol. 33, no. 8, pp. 6738-6754, 2018.

- [5] A. Taghvaie, J. Adabi and M. Rezanejad, "A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure," *IEEE Transactions on Power Electronics*, vol. 33, no. 1, pp. 199-209, 2017.

- [6] R. Shalchi Alishah, S. H. Hosseini, E. Babaei, M. Sabahi and G. B. Gharehpetian, "New High Step-Up Multilevel Converter Topology with Self-Voltage Balancing Ability and Its Optimization Analysis," in *IEEE Transactions on Industrial Electronics*, vol. 64, no. 9, pp. 7060-7070, 2017.

- [7] Kumar, G K Naveen, and Yash Pal, "A new switching scheme for fuel cell supported reduced switch three phase multilevel inverter topology," 2015 International Conferenceon Energy Power and Environment Towards Sustainable Growth (ICEPE), pp. 1-4, 2015.

- [8] J. Liu, J. Wu and J. Zeng, "Symmetric/Asymmetric Hybrid Multilevel Inverters Integrating Switched-Capacitor Techniques," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 3, pp. 1616-1626, 2018.

- [9] S. Lee, "Single-Stage Switched-Capacitor Module (S3CM) Topology for Cascaded Multilevel Inverter," *IEEE Transactions on Power Electronics*, vol. 33, no. 10, pp. 8204-8207, 2018.

- [10] Hossein Ardi, Ali Ajami, Mehran Sabahi, "A novel high step-up DC–DC converter with continuous input current integrating coupled inductor for renewable energy applications," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 2, pp. 1306-1315, 2017.

- [11] Mojtaba Forouzesh, Yam P. Siwakoti, Saman A. Gorji, Frede Blaabjerg, Brad Lehman, "Step-up DC–DC converters: a comprehensive review of voltage-boosting techniques, topologies, and applications," *IEEE transactions on power electronics*, vol. 32, no. 12, pp. 9143-9178, 2017.

- [12] Minh-Khai Nguyen, Truong-Duy Duong, Young-Cheol Lim, "Switched-capacitor-based dual-switch high-boost DC–DC converter," *IEEE transactions on power electronics*, vol. 33, no. 5, pp. 4181-4189, 2017.

- [13] Sathyan, Shelas, H. M. Suryawanshi, Makarand Sudhakar Ballal, and Amardeep B. Shitole, "Soft-switching DC—DC converter for distributed energy sources with high step-up voltage capability," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 11, pp. 7039-7050, 2015.

- [14] K. I. Hwu, W. Z. Jiang, L. C. Yang. "A novel voltage-boosting converter with leakage inductance energy recycling," 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), pp. 1297-1302 2015.

- [15] P. Sung-Jun *et al.*, "A new single-phase five-level PWM inverter employing a deadbeat control scheme," *IEEE Transactions on power electronics*, vol. 18, no. 3, pp. 831–843, 2003.

- [16] Mekhilef and A. Masaoud, "Xilinx FPGA based multilevel PWM single phase inverter," 2006 IEEE International Conference on Industrial Technology, pp. 259–264, 2006.

- [17] C. Klumpner and F. Blaabjerg, "Using reverse-blocking IGBTs in power converters for adjustable-speed drives," IEEE Transactions on Industry Applications, vol. 42, no. 3, pp. 807–816, 2006.

- [18] E. A. Mahrous *et al.*, "Three-phase three-level voltage source inverter with low switching frequency based on the two-level inverter topology," *IET Electric Power Applications*, vol. 1, no. 4, pp. 637–641, 2007.

- [19] E. A. Mahrous and S. Mekhilef, "Design and implementation of a multi level three-phase inverter with less switches and low qutput voltage distortion," *Journal of Power Electronics*, vol. 9, no. 4, pp. 593–603, 2009.

- [20] H. W. Ping, N. A. Rahim, and J. Jamaludin, "New three-phase multilevel inverter with shared power switches," *Journal of Power Electronics*, vol. 13, no. 5, pp. 787–797, 2013.

- [21] S. Suroso and T. Noguchi, "Multilevel current waveform generation using inductor cells and H-bridge current-source inverter," *IEEE transactions on power electronics*, vol. 27, no. 3, pp. 1090–1098, 2012.

- [22] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of submultilevel inverters," *IEEE transactions on power electronics*, vol. 28, no. 2, pp. 625–636, 2013.

- [23] C. Govindaraju and K. Baskaran, "Efficient sequential switching hybrid-modulation techniques for cascaded multilevel inverters," *IEEE Transactions on Power Electronics*, vol. 26, no. 6, pp. 1639–1648, 2011.

- [24] A. Nami *et al.*, "A hybrid cascade converter topology with series-connected symmetrical and asymmetrical diodeclamped H-bridge cells," *IEEE transactions on power electronics*, vol. 26, no. 1, pp. 51–65, 2011.

- [25] S. Mekhilef *et al.*, "Digital control of three phase three-stage hybrid multilevel inverter," *IEEE Trans. Ind. Electron. IEEE Transactions on Industrial Informatics*, vol. 9, no. 2, pp. 719–727, 2013.

- [26] J. Mathew et al., "A hybrid multilevel inverter system based on dodecagonal space vectors for medium voltage IM drives," IEEE transactions on power electronics, vol. 28, no. 8, pp. 3723–3732, 2013.

### **BIOGRAPHIES OF AUTHORS**

M.Selvaperumal has done her B.E EEE from Madras University, in the year 2002 and M.E in Power Electronics and Industrial Drives from Sathyabama University, Tamil Nadu in the year 2005. He is by and by a research Scholar at Sathyabama University Chennai, India. His examination intrigue incorporates Pv Based Asymmetrical Cascade Three Phase Nine Level Multi Level Inverter Fed Induction Motor.

D. Kirubakaran has gotten his Ph.D. from Anna University in 2010 and an M.E. Degree from Bharathidasan University in 2000. His territory of intrigue is AC-AC converters for acceptance warming, non-traditional vitality sources. By and by controlling in excess of ten exploration researchers at different Universities and has distributed in excess of 20 papers in the filed Journals. He has taken an interest as a keynote speaker, and as a commentator in numerous International gatherings. He has 15 years of showing experience and by and by he is Professor and Head of EEE, St. Joseph's Institute of Technology, Chennai – 119.