ISSN: 2088-8694, DOI: 10.11591/ijpeds.v11.i4.pp1945-1957

# Bidirectional single-loop current sensorless control applied to NPC multi-level converter considering conduction losses

### Alexander Suzdalenko, Janis Zakis, Pavels Suskis, Leonids Ribickis

Institute of Industrial Electronics and Electrical Engineering, Riga Technical University, Latvia

### **Article Info**

### Article history:

Received Jan 6, 2020 Revised Apr 26, 2020 Accepted Jun 26, 2020

### Keywords:

AC-DC power converters Current control Pulse width modulation Sensorless control

### ABSTRACT

The current feedback is considered as unavoidable part of most control system driving power electronic converters. However, it is possible to eliminate the use of current sensor, if properly calculated volt-second balance is applied to input inductor. This paper describes the implementation of current sensorless control technique applied to neutral point clamped multi-level converter, where only voltage control-loop is used to stabilize internal capacitors voltage, while inductor's current is shaped by means of current sensorless control block in both discontinuous and continuous current modes. The capacitor voltage balancing is implemented by means of delta-controller that selects alternative capacitor in respect to main switching scheme. Finally, the analytical study of proposed solution is verified with simulation results.

This is an open access article under the CC BY-SA license.

1945

### Corresponding Author:

Alexander Suzdalenko, Institute of Industrial Electronics and Electrical Engineering, Riga Technical University,

Azenes str. 12/1-515, Riga, Latvia, LV1048. Email: aleksandrs.suzdalenko@rtu.lv

## 1. INTRODUCTION

Awareness of human impact on the environment resulted in increasing use of renewable energy sources [1] that in turn contributed to the development of power electronics applications: interface converters for renewable energy sources [2], reversible converters for energy storage systems [3]. Moreover, standards that govern the quality of electrical energy consumed from the network forces to use more efficient power supply blocks with utilisation of power factor correction schemes. As a result, the application sphere of modern switched mode power supplies is targeting wide range of nominal power [4]. The necessity of PFC is clearly demonstrated in [5], where it is concluded that household electrical appliances with poor PF can impact the voltage at the feeder terminal. Variety of power electronic topologies with power factor correction feature have been introduced and studied in the literature [6–14]. The effect of different PFC control approaches operating at distorted input voltage have been studied in [15], where it is stated that sinusoidal current consumption is better than emulated resistor behavior.

New enabling materials for power switches allow designing transistors with high electron mobility featuring higher switching frequencies, wide bandgap transistors allow higher blocking voltages, as well as production technology itself (GaN multi block) allows minimizing switching losses [16–21]. At the same time, development of digital control systems allows implementing advanced control algorithms for power electronic converters that also leads to increased converter's total performance. Specifically, the focus is made on new current control approaches that directly influence overall merits: the total harmonic distortion, unity power factor, converters' dynamics, ability to control current in mixed conduction mode, etc [22–28].

Journal homepage: http://ijpeds.iaescore.com

1946 □ ISSN: 2088-8694

### 2. LITERATURE OVERVIEW ON CONTROL METHODS

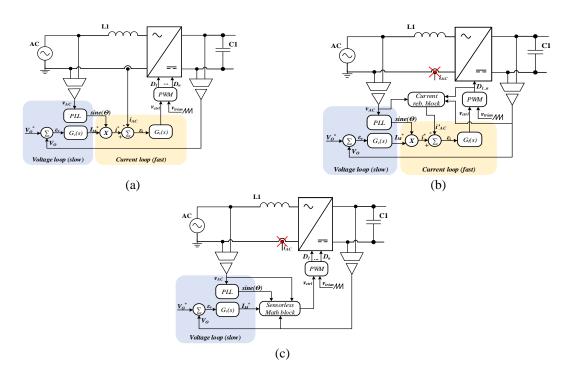

Presently most of current controlled power electronics converters are usually driven with traditional type of control strategies, where two control loops are implemented – one (slow) voltage control loop that stabilizes DC bus voltage, second (fast) current control loop that shapes the current form sinked/sourced from/to the grid (see Figure 1(a)). The current control loop is usually implemented with one of traditional current control techniques: hysteresis control, PID, proportional resonant, space vector PWM. All mentioned current control approaches are based on instantaneous current sampling, that ustilises shunt resistor or galvanically isolated current sensor. The first one introduces additional power losses due to active resistance, while latter is costly and has limited bandwidth that limits its application with modern power electronic converters operating at higher commutation frequencies.

Thus, to eliminate drawbacks caused by current sensor, current sensorless control algorithm has been studied. It allows eliminating instantaneous current measurement. Various researches have been conducted in this relation, where different implementations have been demonstrated. In [29–32] researchers have implemented CSC, where mathematical current rebuilding block is introduced that rebuilds the current based on PWM signals and precise model of converter (see Figure 1 (b)). Calculated value from mathematical block is compared with reference current shape and error is entered to PI block that adjusts the duty ratio of PWM signals. In this case, still two control loops are utilized.

Some other researches [33–35] have minimized the number of current sensors by introducing current decoder block. It estimates AC-side and each capacitor currents depending on the state of transistors. These researches are usually entitled "AC current sensorless approach...", meaning that only AC current sensor is eliminated. Interesting research results are published in [36], where only one DC-side voltage sensor is used to control three-phase boost PFC converter, while all other parameters are estimated based on predefined converter parameters and pulsations of DC capacitor.

So-called single-loop current sensorless control (CSC) approach has been introduced in 2000 [37]. This type of control utilises only one control loop with feedback from the output capacitor voltage and does not use any current feedback signal as it is assumed that inductor's volt-second balance is perfectly calculated and inductor's current follows the reference signal (see Figure 1 (c)). Since that time the CSC has been applied to multiple type of PFC topologies: single switch PFC (diode bridge and boost converter) [38, 39], interleaved [40, 41], bridgeless [42, 43], half-bridge [44–46], full-bridge [47, 48] and also neutral-point clamped multi-level converter (NPC MLC) [49, 50]. Several recently published papers have been devoted to different type of three-phase converter topologies operated under CSC [51–53] that makes evidence of CSC use in high power applications.

Figure 1. Preview of different control schemes used in PFC converters: (a) Traditional double loop control scheme, (b) CSC scheme with current rebuilding block, (c) Single-loop CSC scheme

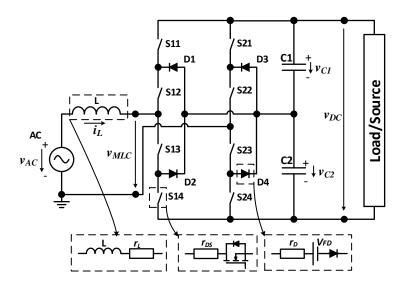

Most of mentioned CSC research papers deal with ideal models of semiconductor switches and do not consider conduction losses caused by parasitic circuit elements. The effect of neglecting parasitic losses on the shape of grid current is discussed in the literature [54–57], where multiple solutions are proposed to overcome this problem: current error compensators, adaptive inductor model and continuous estimation of parasitics based on zero-current detection. Negative effect of parasitic circuit components on the current shape increases with the number of transistors in the current path of the converter topology that is actual to MLC type of converter (see Figure 2). Thus, this paper is devoted to definition of single-loop CSC algorithm for NPC MLC with bidirectional current control and consideration of conduction losses. To the best knowledge of the authors, this type of control has not been described in the literature yet and potentially is interesting to industry due to economical and efficiency effect that will be stated at the end of this paper.

Figure 2. Power circuit topology of a neutral point clamped multilevel converter with considered parasitic components

### 3. RESEARCH METHOD

The research of original idea is based on analytical study of electrical circuit. The analytical analysis for duty cycle calculation equations are made describing both continuous and discontinuous operation modes. The analysis of all switching states of MLC converter is done, for each of which the identification of inductor voltage equation is made. In order to minimise the number of equations that are used to describe inductor's voltage the single-switch model is utilised. The proposed control approach is verified by means of simulation analysis demonstrating its performance during different step-response cases: changing load from light to nominal value, changing power flow direction back and forward, as well as THD performance is provided at different power ratings.

# 3.1. Definition of transition between operational voltage levels

The main goal of CSC is to provide proper volt-second balance applied to input inductor that would keep average inductor current to follow the sinusoidal reference. As the inductor might operate in discontinuous and continuous conduction mode (DCM and CCM), two calculation equations should be obtained.

The MLC converter is driven with PWM signal generated by control system that determine two basic states: 1) boosting inductor's energy and 2) releasing inductor's energy. The duty ratio of PWM signal is set by output signal ( $v_{CTRL}$ ) from control system that is compared with triangle voltage as follows:

$$d(t) = \begin{cases} 1, & \text{if } v_{CTRL}(t) > v_{trian}(t) \\ 0, & \text{otherwise} \end{cases}$$

(1)

Transition between different voltage levels are defined depending on the grid voltage  $(V_{AC})$  in trespect to internal DC bus voltage  $(V_{DC})$ :

1948 ISSN: 2088-8694

$$LVL(t) = \begin{cases} 1, if & |v_{AC}(t)| \ge 0.5 \cdot v_{DC}(t) \\ 0, otherwise \end{cases}$$

(2)

Depending on MLC power flow direction (positive current amplitude  $(I_M>0)$ ) is assumed as rectifier mode, negative current amplitude  $(I_M < 0)$  – inverter mode) and value of AC voltage different DC voltage is commutated at the AC-side of MLC converter during two states of PWM signal:

$$V_{MLC}^{d=1} = \begin{cases} 0, if \ I_{M} > 0 \ and \ LVL(t) = 0 \\ V_{DC}/2, if \ I_{M} > 0 \ and \ LVL(t) = 1 \\ V_{DC}/2, if \ I_{M} < 0 \ and \ LVL(t) = 0' \\ V_{DC}, if \ I_{M} < 0 \ and \ LVL(t) = 1 \end{cases}$$

$$V_{MLC}^{d=0} = \begin{cases} V_{DC}/2, if \ I_{M} > 0 \ and \ LVL(t) = 0 \\ V_{DC}, if \ I_{M} > 0 \ and \ LVL(t) = 1 \\ 0, if \ I_{M} < 0 \ and \ LVL(t) = 0 \\ V_{DC}/2, if \ I_{M} < 0 \ and \ LVL(t) = 1 \end{cases}$$

$$(4)$$

$$V_{MLC}^{d=0} = \begin{cases} V_{DC}/2, & \text{if } I_M > 0 \text{ and } LVL(t) = 0 \\ V_{DC}, & \text{if } I_M > 0 \text{ and } LVL(t) = 1 \\ 0, & \text{if } I_M < 0 \text{ and } LVL(t) = 0 \end{cases}$$

$$V_{DC}/2, & \text{if } I_M < 0 \text{ and } LVL(t) = 1$$

$$(4)$$

### 3.2. Definition of control laws for DCM and CCM

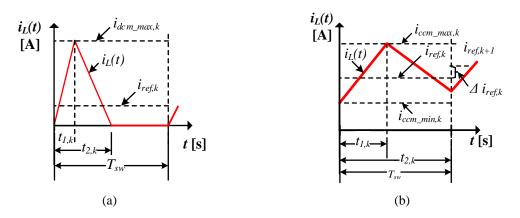

The control law of inductor's current in DCM differs significantly from CCM. The current always starts from zero in DCM and average inductor current has squared ratio to transistor's conduction time (see Figure 3(a)). Contrary to DCM, average current value has proportional ratio to conduction time during CCM and starting point of rising current is equal to the end value falling edge of previous switching cycle (Figure 3(b)). This potentially leads to the problem that the error of control signal can be accumulated and the current form can degrade significantly.

Figure 3. Current waveform during (a) DCM and (b) CCM

The equation that would allow to calculate the duty ratio for PWM signal during DCM could be estimated from the following definition:

$$i_{ref,k} = \frac{1}{T_{SW}} \int_{k \cdot T_{SW}}^{(k+1) \cdot T_{SW}} I_M \cdot \sin(t) \, dt = \int_{k \cdot T_{SW}}^{(k+1) \cdot T_{SW}} i_L(t) dt. \tag{5}$$

Assuming that inductor current is rising and falling linearly, the equation above can be rewritten as

$$i_{ref,k} = \frac{1}{T_{cw}} \left( \int_0^{t_1} \frac{v_L^{d=1}(t)}{L} dt + \int_{t_1}^{t_2} \frac{v_L^{d=0}(t)}{L} dt \right). \tag{6}$$

Taking into account, that grid voltage and also capacitor voltage are almost invariable during single switching cycle, the voltage applied to inductor can be assumed as constant. Thus, the equation above allows defining the ratio between turn-on and turn-off time ( $t_{2,k}$  and  $t_{1,k}$  correspondingly) for the converter operating in DCM:

$$t_{2,k} = \left(1 - \frac{v_{L,k}^{d=1}}{v_{L,k}^{d=0}}\right) \cdot t_{1,k}. \tag{7}$$

Inductor's peak current value can be defined as follows:

$$i_{DCM\_max,k} = \frac{v_{L,k}^{d=1}}{L} \cdot t_{1,k}. \tag{8}$$

The DCM control equation can be found by using simple triangle area definition formula, substituting height of the triangle with (8) and base with (7). The resulted control law is seen below:

$$D_{DCM,k} = \frac{t_{1,k}}{T_{SW}} = \sqrt{\frac{2 \cdot L \cdot i_{ref,k}}{T_{SW}} \cdot \frac{v_{L,k}^{d=0}}{v_{L,k}^{d=1} \cdot (v_{L,k}^{d=0} - v_{L,k}^{d=1})}}.$$

(9)

The control of transistor during CCM ensures that average inductor current will follow the changes of reference value that is described as:

$$\Delta i_{ref,k} = \frac{v_{L,k}^{d=1}}{L} \cdot t_{1,k} + \frac{v_{L,k}^{d=0}}{L} \cdot \left( T_{sw} - t_{1,k} \right). \tag{10}$$

Consequently, the CCM current control law can be defined as follows

$$D_{CCM,k} = \frac{t_{1,k}}{T_{sw}} = \frac{\frac{\Delta i_{ref,k} \cdot L}{T_{sw}} - v_{L,k}^{d=0}}{v_{L,k}^{d=1} - v_{L,k}^{d=0}}.$$

(11)

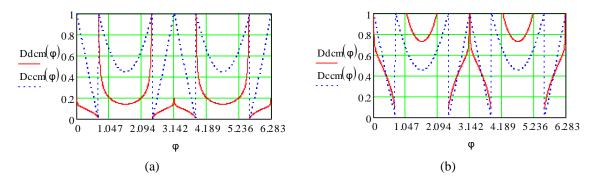

The  $D_{CCM}$  crosses the  $D_{DCM}$  control function at the boundary conduction mode and has smaller value in CCM (Figure 4). Thus, the resulted control law is selected as minimal value out of both control laws.

Figure 4. Preview of DCM and CCM duty ratios for (a) inductor operating only in DCM ( $I_M$ =0.1 A) and (b) in mixed conduction mode ( $I_M=2.5 A$ )

### 3.3. Definition of inductor voltage considering conduction losses

The Table 1 demonstrate all switching states of MLC for all operation modes and the equations of inductor's voltage are defined as well for each switching state. Keeping in mind that MLC allows commutating single capacitor voltage to AC input, it is assumed that during positive AC voltage the C1 capacitor is mainly used and capacitor C2 - during negative half-period. Opposite capacitor commutation logic can be used for capacitor voltage balancing (see Table 2).

As can be seen from Table 1, inductor's voltage equations are constituted by multiple variables, which might change its sign and integer coefficient. For this reason, two bool functions are defined that can help to track the changes of variables:

$$sign(x) = \begin{cases} -1, & \text{if } x < 0, \\ 1, & \text{if } x \ge 0 \end{cases}$$

$$gtz(x) = \begin{cases} 0, & \text{if } x < 0, \\ 1, & \text{if } x \ge 0 \end{cases}$$

(12)

$$gtz(x) = \begin{cases} 0, & \text{if } x < 0, \\ 1, & \text{if } x \ge 0 \end{cases}$$

(13)

1950 ISSN: 2088-8694

As previously mentioned, there is main capacitor that is commutated during half-period of input voltage that can be formulated as follows:

$$v_{C\_main,k} = gtz(v_{AC,k}) \cdot v_{C1,k} + gtz(-v_{AC,k}) \cdot v_{C2,k}. \tag{14}$$

The number of switches  $(N_{SW})$  and number of diodes  $(N_D)$  in the current path in both energy storing (d=1) and energy releasing (d=0) states can be defined as follows:

$$N_{SW,k}^{d=1} = gtz(I_M) \cdot (2 + LVL_k) + gtz(-I_M) \cdot (3 + LVL_k), \tag{15}$$

$$\begin{split} N_{SW,k}^{d=1} &= gtz(I_M) \cdot (2 + LVL_k) + gtz(-I_M) \cdot (3 + LVL_k), \\ N_{SW,k}^{d=0} &= gtz(I_M) \cdot (3 + LVL_k) + gtz(-I_M) \cdot (2 + LVL_k), \\ N_{D,k}^{d=1} &= 4 - N_{SW,k}^{d=1}, \\ N_{D,k}^{d=0} &= 4 - N_{SW,k}^{d=0}. \end{split} \tag{15}$$

$$N_{D,k}^{d=1} = 4 - N_{SW,k}^{d=1}, (17)$$

$$N_{Dk}^{d=0} = 4 - N_{SWk}^{d=0}. (18)$$

At last, the commutated DC voltage should be defined. It is implemented with two variable components that defines conditions, when single capacitor voltage  $(v_{DC/2,k})$  and full DC voltage  $(v_{DC,k})$  is commutated at AC-side of MLC. It is defined as

$$v_{DC/2,k}^{d=1} = v_{C\_main,k} \cdot \left( -gtz(I_M) \cdot LVL_k + gtz(-I_M) \cdot (1 - LVL_k) \right), \tag{19}$$

$$v_{DC/2,k}^{d=0} = v_{C\_main,k} \cdot (-gtz(I_M) \cdot (1 - LVL_k) + gtz(-I_M) \cdot LVL_k),$$

$$v_{DC,k}^{d=1} = v_{DC,k} \cdot gtz(-I_M) \cdot LVL_k,$$

$$v_{DC,k}^{d=0} = -v_{DC,k} \cdot gtz(I_M) \cdot LVL_k.$$

(21)

$$v_{DC,k}^{d=1} = v_{DC,k} \cdot gtz(-I_M) \cdot LVL_k, \tag{21}$$

$$v_{DCk}^{d=0} = -v_{DCk} \cdot gtz(I_M) \cdot LVL_k. \tag{22}$$

Having defined these functions, the final inductor's voltage during active and freewheeling state can be defined with two functions below

$$v_{L,k}^{d=1} = sign(v_{AC,k}) \cdot sign(I_M) \cdot v_{AC,k} + v_{DC/2,k}^{d=1} + v_{DC,k}^{d=1} - \\ -N_{D,k}^{d=1} \cdot V_{FD} - |i_{ref,k}| \cdot (r_L + N_{SW,k}^{d=1} \cdot r_{DS} + N_{D,k}^{d=1} \cdot r_{D}),$$

$$v_{L,k}^{d=0} = sign(v_{AC,k}) \cdot sign(I_M) \cdot v_{AC,k} + v_{DC/2,k}^{d=0} + v_{DC,k}^{d=0} - \\ -N_{D,k}^{d=0} \cdot V_{FD} - |i_{ref,k}| \cdot (r_L + N_{SW,k}^{d=0} \cdot r_{DS} + N_{D,k}^{d=0} \cdot r_{D}).$$

$$(23)$$

$$-N_{D,k}^{d=0} \cdot V_{FD} - \left| i_{ref,k} \right| \cdot \left( r_L + N_{SW,k}^{d=0} \cdot r_{DS} + N_{D,k}^{d=0} \cdot r_D \right). \tag{24}$$

where  $V_{FD}$  and  $r_D$  are forward voltage and dynamic resistance of diode's equivalent model respectively;  $r_{DS}$  is MOSFET's on-state resistance;  $r_L$  is inductor's parasitic active resistance.

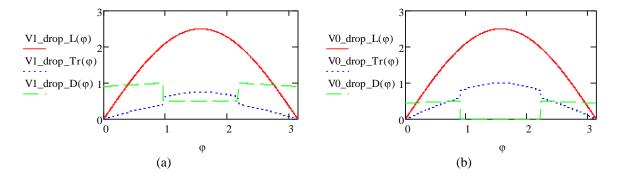

Defined equations allow easily tracking variable voltage drop caused by parasitic circuit elements that is demonstrated in the Figure 5.

Table 1. Summary of normal switching states of MLC converter and corresponding inductor voltage equation

| Power<br>flow         | Input<br>voltage<br>polarity | Input voltage<br>level  | Switch state $d(t)$ | S11 | S12 | S13 | S14 | S21 | S22 | S23 | S24 | Inductor's voltage                                                            |

|-----------------------|------------------------------|-------------------------|---------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------------------------------------------------------------------------------|

| Rectifier $(I_M > 0)$ | Positive                     | $ V_{AC}  < 0.5 V_{DC}$ | 1                   | -   | -   | 1   | -   | -   | 1   | -   | -   | $V_L = V_{AC} - 2 \cdot V_{FD} - I_{ref}(r_L + 2 \cdot r_{DS} + 2 \cdot r_D)$ |

|                       |                              |                         | 0                   | 1   | 1   | -   | -   | -   | 1   | -   | -   | $V_L = V_{AC} - V_{CI} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$        |

|                       |                              | $ V_{AC}  > 0.5 V_{DC}$ | 1                   | 1   | 1   | -   | -   | -   | 1   | -   | -   | $V_L = V_{AC} - V_{CI} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$        |

|                       |                              |                         | 0                   | 1   | 1   | -   | -   | -   | -   | 1   | 1   | $V_L = V_{AC} - V_{CI} - V_{C2} - I_{ref}(r_L + 4 \cdot r_{DS})$              |

|                       | Negative                     | $/V_{AC}/<0.5~V_{DC}$   | 1                   | -   | 1   | -   | -   | -   | -   | 1   | -   | $V_L = V_{AC} - 2 \cdot V_{FD} - I_{ref}(r_L + 2 \cdot r_{DS} + 2 \cdot r_D)$ |

|                       |                              |                         | 0                   | -   | -   | 1   | 1   | -   | -   | 1   | -   | $V_L = -V_{AC} - V_{C2} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$       |

|                       |                              | $ V_{AC}  > 0.5 V_{DC}$ | 1                   | -   | -   | 1   | 1   | -   | -   | 1   | -   | $V_L = -V_{AC} - V_{C2} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$       |

|                       |                              |                         | 0                   | -   | -   | 1   | 1   | 1   | 1   | -   | -   | $V_L = -V_{AC} - V_{C1} - V_{C2} - I_{ref}(r_L + 4 \cdot r_{DS})$             |

| Inverter $(I_M < 0)$  | Positive                     | $/V_{AC}/<0.5 \ V_{DC}$ | 1                   | 1   | 1   | -   | -   | -   | -   | 1   | -   | $V_L = -V_{AC} + V_{CI} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$       |

|                       |                              |                         | 0                   | -   | 1   | -   | -   | -   | -   | 1   | -   | $V_L = V_{AC} - 2 \cdot V_{FD} - I_{ref}(r_L + 2 \cdot r_{DS} + 2 \cdot r_D)$ |

|                       |                              | $/V_{AC}/>0.5 V_{DC}$   | 1                   | 1   | 1   | -   | -   | -   | -   | 1   | 1   | $V_L = -V_{AC} + V_{CI} + V_{C2} - I_{ref}(r_L + 4 \cdot r_{DS})$             |

|                       |                              |                         | 0                   | 1   | 1   | -   | -   | -   | -   | 1   | -   | $V_L = -V_{AC} + V_{CI} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$       |

|                       | Negative                     | $/V_{AC}/<0.5~V_{DC}$   | 1                   | -   | -   | 1   | 1   | -   | 1   | -   | -   | $V_L = V_{AC} + V_{C2} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$        |

|                       |                              |                         | 0                   | -   | -   | 1   | -   | -   | 1   | -   | -   | $V_L = V_{AC} - 2 \cdot V_{FD} - I_{ref}(r_L + 2 \cdot r_{DS} + 2 \cdot r_D)$ |

|                       |                              | $/V_{AC}/>0.5~V_{DC}$   | 1                   | -   | -   | 1   | 1   | 1   | 1   | -   | -   | $V_L = V_{AC} + V_{C1} + V_{C2} - I_{ref}(r_L + 4 \cdot r_{DS})$              |

|                       |                              |                         | 0                   | -   | -   | 1   | 1   | -   | 1   | -   | -   | $V_L = V_{AC} + V_{C2} - V_{FD} - I_{ref}(r_L + 3 \cdot r_{DS} + r_D)$        |

П

|                       |                              |                           | Table 2.            | Swite | ching | states | usec | l for o | capac | itor b | alanc | ring                          |           |           |

|-----------------------|------------------------------|---------------------------|---------------------|-------|-------|--------|------|---------|-------|--------|-------|-------------------------------|-----------|-----------|

| Power<br>flow         | Input<br>voltage<br>polarity | Input<br>voltage<br>level | Active state $d(t)$ | S11   | S12   | S13    | S14  | S21     | S22   | S23    | S24   | Simplified inductor's voltage | $dV_{CI}$ | $dV_{C2}$ |

| Rectifier $(I_M > 0)$ | Positive                     | $/V_{AC}/<0.5$            | 0                   | -     | -     | 1      | -    | -       | -     | 1      | 1     | $V_L = V_{AC} - V_{C2}$       | 0         | +         |

|                       |                              | $V_{DC}$                  |                     | 1     | 1     | -      | -    | -       | 1     | -      | -     | $V_L = V_{AC} - V_{CI}$       | +         | 0         |

|                       |                              | $/V_{AC}/>0.5$            | 1                   | 1     | 1     | -      | -    | -       | 1     | -      | -     | $V_L = V_{AC} - V_{CI}$       | +         | 0         |

|                       |                              | $V_{DC}$                  |                     | -     | -     | 1      | -    | -       | -     | 1      | 1     | $V_L = V_{AC} - V_{C2}$       | 0         | +         |

|                       | Negative                     | $/V_{AC}/<0.5$            | 0                   | -     | 1     | -      | -    | 1       | 1     | -      | -     | $V_L = V_{AC} - V_{CI}$       | +         | 0         |

|                       |                              | $V_{DC}$                  |                     | -     | -     | 1      | 1    | -       | -     | 1      | -     | $V_L = V_{AC} - V_{C2}$       | 0         | +         |

|                       |                              | $/V_{AC}/>0.5$            | 1                   | -     | 1     | -      | -    | 1       | 1     | -      | -     | $V_L = V_{AC} - V_{CI}$       | +         | 0         |

|                       |                              | $V_{DC}$                  |                     | -     | -     | 1      | 1    | -       | -     | 1      | -     | $V_L = V_{AC} - V_{C2}$       | 0         | +         |

| Inverter $(I_M < 0)$  | Positive                     | $/V_{AC}/<0.5$            | 1                   | 1     | 1     | -      | -    | -       | -     | 1      | -     | $V_L = V_{CI} - V_{AC}$       | -         | 0         |

|                       |                              | $V_{DC}$                  |                     | -     | 1     | -      | -    | -       | -     | 1      | 1     | $V_L = V_{C2} - V_{AC}$       | 0         | -         |

|                       |                              | $/V_{AC}/>0.5$            | 0                   | -     | 1     | -      | -    | -       | -     | 1      | 1     | $V_L = V_{C2} - V_{AC}$       | 0         | -         |

|                       |                              | $V_{DC}$                  |                     | 1     | 1     | -      | -    | -       | -     | 1      | -     | $V_L = V_{CI} - V_{AC}$       | -         | 0         |

|                       | Negative                     | $/V_{AC}/<0.5$            | 1                   | -     | -     | 1      | 1    |         | 1     | -      | -     | $V_L = V_{C2} + V_{AC}$       | 0         | -         |

|                       |                              | $V_{DC}$                  |                     | -     | -     | 1      | -    | 1       | 1     | -      | -     | $V_L = V_{CI} + V_{AC}$       | -         | 0         |

|                       |                              | $/V_{AC}/>0.5$            | 0                   |       |       | 1      |      | 1       | 1     |        |       | $V_L = V_{CI} + V_{AC}$       | -         | 0         |

|                       |                              | $V_{DC}$                  | 0                   | -     | -     | 1      | 1    | -       | 1     | -      | -     | $V_L = V_{C2} + V_{AC}$       | 0         | -         |

Figure 5. Graphical representation of voltage drop caused by different parasitic components: inductor  $(Vx\_drop\_L \text{ caused by } r_L=0.5 \ \Omega)$ , transistors  $(Vx\_drop\_Tr \text{ caused by } r_{DS}=0.025 \ \Omega)$  and diodes  $(Vx\_drop\_D \text{ caused by } V_{FD}=0.5 \ V \text{ and } r_D=0.012 \ \Omega)$  at reference current amplitude  $I_M=3.5 \ A$  during (a) energy storing state (d(t)=1) and (b) energy releasing state (d(t)=0)

# 3.4. Capacitor voltage balancing

In normal case, the converter having two serially connected capacitors in the DC link experience voltage fluctuation during period of grid's voltage. In ideal, capacitors' voltage difference is described as follows:

$$v_{C1}(t) - v_{C2}(t) = \frac{I_M \cdot \cos(\omega t)}{c}.$$

(25)

This however is not perfectly match to MLC as capacitor's current direction changes during half-period of grid voltage. In order to minimize the calculation complexity, the digital controller of capacitor balancing can be implemented by sampling capacitor voltages during  $\pi/2$  and  $3\pi/2$ , where capacitor voltage crossing occurs in ideal case. The voltage difference can be used as input error for P or PI controller, that would add additional component to input current amplitude, in this way, capacitor voltage balancing is implemented. Asymmetrical input current amplitudes can generate DC component in the spectrum of the AC current that is prohibited by the standards, like IEEE Std 519-2014. Nevertheless, capacitor balancing with assymetrical current amplitudes was utilized in some applications due to limitation of selected topology [46, 58].

Another solution is based on continuous monitoring of capacitor voltages and implementation of delta-controller that selects one of two switching options that minimizes capacitor voltage difference (defined

1952 □ ISSN: 2088-8694

in Table 2). This solution is interesting due to following pros: 1) reduces thermal stress of switching components during half-period of input voltage and 2) minimizes voltage pulsations on capacitors.

Alternative function of selection single capacitor voltage (previously defined with eq.14) that should be used for capacitor balancing is defined below:

$$v_{C\_main,k} = \begin{cases} if \left( gtz(v_{AC,k}) \ xor \ gtz(I_{M,k}) = 1 \right), then \begin{cases} gtz(v_{AC,k}) \cdot v_{C2,k} + gtz(-v_{AC,k}) \cdot v_{C1,k}, if \ v_{C1,k} < v_{C2,k} \\ gtz(v_{AC,k}) \cdot v_{C1,k} + gtz(-v_{AC,k}) \cdot v_{C2,k}, if \ v_{C2,k} \geq v_{C2,k} \end{cases} \\ if \left( gtz(v_{AC,k}) \ xor \ gtz(I_{M,k}) = 0 \right), then \begin{cases} gtz(v_{AC,k}) \cdot v_{C2,k} + gtz(-v_{AC,k}) \cdot v_{C1,k}, if \ v_{C2,k} < v_{C1,k} \\ gtz(v_{AC,k}) \cdot v_{C1,k} + gtz(-v_{AC,k}) \cdot v_{C2,k}, if \ v_{C2,k} \geq v_{C1,k} \end{cases} \end{cases}$$

$$(26)$$

### 4. SIMULATION RESULTS

The simulation model was built by means of PSIM software. Simplified C Block was used to program CSC algorithm. The simulation parameters are as follows: a) grid voltage (RMS)  $V_{AC}=230~V$ ; b) grid frequency  $f_{AC}=50~Hz$ ; c) capacitor nominal voltages  $V_{CI}$ ,  $V_{C2}=250V$ ; d) inductance L=2.2~mH; e) capacitance CI, C2=1~mF; f) switching frequency  $f_{SW}=25~kHz$ .

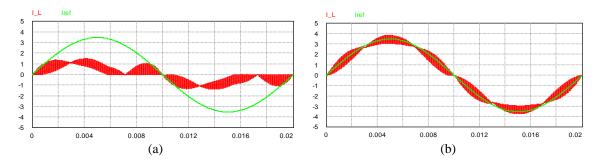

The impact of the parasitic circuit elements on the inductor current is clearly seen from the 0. The figure on the left demonstrates current shape if conduction losses are not considered, where the average current deviates from the reference signal each switching cycle due to error in calculation of volt-second balance. The figure on the right demonstrates the performance of proposed duty cycle control approach with consideration of conduction losses, where  $THD_i$  is below 10%.

Figure 6. Simulation result of sensorless control applied to NPC MLC without (a) and with (b) consideration of conduction losses (simulation parameters:  $I_M$ =3.5 A)

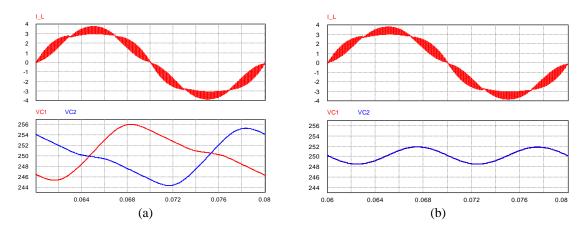

Demonstration of two capacitors' voltage balancing approaches is seen in the Figure 7. The current drawn from the grid is identical, while pulsations of capacitor voltages were decreased from 11 V to less than 4 V.

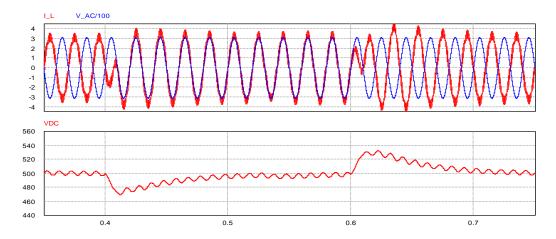

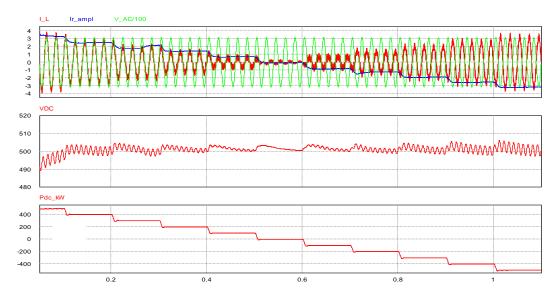

The simulation of step response was performed in order to evaluate transient responses of the proposed CSC. The controller consisted of single control loop with voltage feedback from DC voltage and reference signal of 500 V. It was based on PI controller with Notch filter, responsible for filtering out 100 Hz capacitor voltage pulsations. The current source was added to DC side that was sourcing 1 A, at 0.4 s changed to sinking of 1 A, and at 0.6 s changed back to sourcing of 1 A. The simulation results are presented in the Figure 8. The current was in phase with grid voltage before and after transient. The DC voltage overshoot was 30 V and transient time for voltage stabilisation was 150 ms that is comparable performance to similar control approaches implemented by other researchers [48, 52, 59, 60].

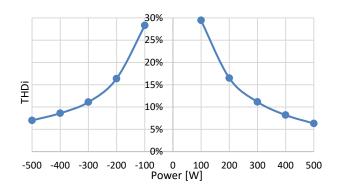

The Figure 9 demonstrate the performance of CSC at multiple points of power changing DC-side load from 500 W (consuming power) downto -500 W (sourcing power) with 100 W step each 100 ms. It can be seen that inductor current has sinusoidal shape at wide range of power with stable operation in DCM and CCM, contrary to other researches, where only CCM operation is considered and demonstrated [40, 46, 53]. The corresponding THD values are seen in the Figure 10.

Figure 7. Simulation results of two capacitor voltage balancing approaches – (a) semi-period modification current amplitude and (b) delta-controller that selects alternative capacitor according to equation 26.

Figure 8. Simulation of step response on changing the power flow: at 0.4 s schematic changed to sinking of 500 W from the grid then at 0.6 s changed back to sourcing of 500 W to the grid (top figure scales: 1 A/div, 100 V/div; bottom figure scale: 20 V/div)

Figure 9. Simulation of step-response changing DC-side power from 500 W downto -500 W with 100 W step each  $100~\mathrm{ms}$

1954 □ ISSN: 2088-8694

Figure 10. THD vs converter's DC power

#### 5. DISCUSSIONS AND CONCLUSIONS

The current sensorless control allows shaping inductor's current without feedback from the current sensor. The precise volt-second balance is calculated by means of digital control system taking into account grid's and both capacitors' voltages and major parasitic elements of the power circuit components. As a result, the current shape has acceptable THD and features stable sinusoidal current shape at wide range of input power.

The balancing of capacitor voltages is implemented by means of delta-controller that rapidly selects main or alternative capacitor for charging/discharging depending on converter mode (rectifier/inverter), polarity of input voltage and capacitor voltage mismatch. This is effective solution for voltage balancing and it is trivial for implementation in digital form. This type of controller minimizes the fluctuation of DC link capacitor voltages and eliminates the need of asymmetrical grid's current shape.

The practical implementation of CSC is useful for switched mode power supply engineers due to following facts:

- miniaturization of control system due to elimination of galvanically isolated current sensor;

- seamless sensorless detection of DCM and CCM by means of digital control system selecting minimal value from two duty ratios calculated for DCM and CCM operation;

- stable current shape in DCM due to precise calculation of volt-second balance applied to inductor, that is important in applications where light load operation is considered;

- immunity from distorted grid's voltage as current reference can be generated from internal pure sinusoidal signal.

Nevertheless, the implementation of CSC method has also some challenges that could be addressed in the future researches:

- dependency on precise voltage measurements and nominals of all parasitic elements;

- temperature drift of component nominals and non-linearity of circuit components are difficult to implement in converter's mathematical model. However, partially it could be solved by means of observing of the capacitor voltage pulsation during converter operation and adjustment of nominals of schematic components used for calculations;

- requirement for high computational resources as duty ratio should be calculated before each switching cycle. It means that all ADC values should be acquired and processed within previous switching cycle that involves multiple division operations and calculation of square root;

- CSC features accumulation of current error during CCM operation that has negative effect on current shape;

The authors also think of hybrid implementation of sensored and sensorless current control techniques, taking the best from both, that is a matter of another research.

### ACKNOWLEDGEMENTS

This work has been supported by the European Regional Development Fund within the Activity 1.1.1.2 "Post-doctoral Research Aid" of the Specific Aid Objective 1.1.1 "To increase the research and innovative capacity of scientific institutions of Latvia and the ability to attract external financing, investing in human resources and infrastructure" of the Operational Programme "Growth and Employment" (No.1.1.1.2/VIAA/2/18/328). This research is cofounded also by the Ministry of Economics of the Republic of Latvia, project RTUAER, project No. VPP-EM-AER-2018/3-0004.

П

#### REFERENCES

- [1] G. Masson and I. Kaizuka, Global Energy & CO2 Status Report 2019. Paris: EIA, 2019.

- [2] J. M. Carrasco *et al.*, "Power-Electronic Systems for the Grid Integration of Renewable Energy Sources: A Survey," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1002–1016, Jun. 2006.

- [3] K. Kroics, O. Husev, K. Tytelmaier, J. Zakis, and O. Veligorskyi, "An Overview of Bidirectional AC-DC Grid Connected Converter Topologies for Low Voltage Battery Integration," *Int. J. Power Electron. Drive Syst.*, vol. 9, no. 3, p. 1223, Sep. 2018.

- [4] S. Acharya, O. Ray, and S. K. Mishra, "Powering Milliwatts to Megawatts," *IEEE Consum. Electron. Mag.*, vol. 9, no. 2, pp. 70–75, Mar. 2020.

- [5] Y. Wang, J. Yong, Y. Sun, W. Xu, and D. Wong, "Characteristics of Harmonic Distortions in Residential Distribution Systems," *IEEE Trans. Power Deliv.*, vol. 32, no. 3, pp. 1495–1504, Jun. 2017.

- [6] C. K. Tse, "Circuit theory of power factor correction in switching converters," Int. J. Circuit Theory Appl., vol. 31, no. 2, pp. 157–198, 2003.

- [7] O. Garcia, J. A. Cobos, R. Prieto, P. Alou, and J. Uceda, "Single phase power factor correction: a survey," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 749–755, May 2003.

- [8] G. Moschopoulos and P. Jain, "Single-Phase Single-Stage Power-Factor-Corrected Converter Topologies," *IEEE Trans. Ind. Electron.*, vol. 52, no. 1, pp. 23–35, Feb. 2005.

- [9] M. Alam, W. Eberle, D. S. Gautam, and C. Botting, "A Soft-Switching Bridgeless AC–DC Power Factor Correction Converter," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7716–7726, Oct. 2017.

- [10] S. M. Antony and G. Immanuel, "A Novel Single Phase bridgeless AC/DC PFC converter for Low Total Harmonics Distortion and High Power Factor," *Int. J. Power Electron. Drive Syst.*, vol. 9, no. 1, p. 17, Mar. 2018.

- [11] R. Sasikala and R. Seyezhai, "Review of AC-DC power electronic converter topologies for power factor correction," *Int. J. Power Electron. Drive Syst.*, vol. 10, no. 3, pp. 1510–1519, 2019.

- [12] M. Chen, S. Chakraborty, and D. J. Perreault, "Multitrack Power Factor Correction Architecture," *IEEE Trans. Power Electron.*, vol. 34, no. 3, pp. 2454–2466, Mar. 2019.

- [13] H. Valipour, M. Mahdavi, and M. Ordonez, "Resonant Bridgeless AC/DC Rectifier With High Switching Frequency and Inherent PFC Capability," *IEEE Trans. Power Electron.*, vol. 35, no. 1, pp. 232–246, Jan. 2020.

- [14] Z. Chen, P. Davari, and H. Wang, "Single-Phase Bridgeless PFC Topology Derivation and Performance Benchmarking," *IEEE Trans. Power Electron.*, vol. 35, no. 9, pp. 9238–9250, Sep. 2020.

- [15] V. M. Lopez-Martin, F. J. Azcondo, and A. Pigazo, "Power Quality Enhancement in Residential Smart Grids Through Power Factor Correction Stages," *IEEE Trans. Ind. Electron.*, vol. 65, no. 11, pp. 8553–8564, Nov. 2018.

- [16] A. Bindra, "Wide-Bandgap-Based Power Devices: Reshaping the power electronics landscape," *IEEE Power Electron. Mag.*, vol. 2, no. 1, pp. 42–47, Mar. 2015.

- [17] J. Rabkowski, D. Peftitsis, and H. Nee, "Silicon Carbide Power Transistors: A New Era in Power Electronics Is Initiated," *IEEE Ind. Electron. Mag.*, vol. 6, no. 2, pp. 17–26, Jun. 2012.

- [18] M. Johnson, P. R. Wilson, L. Empringham, and L. De Lillo, "IEEE ITRW Working Group Position Paper-Packaging and Integration: Unlocking the Full Potential of Wide-Bandgap Devices," *IEEE Power Electron. Mag.*, vol. 5, no. 2, pp. 26–33, Jun. 2018.

- [19] V. Veliadis, R. Kaplar, J. Zhang, M. Bakowski, S. Khalil, and P. Moens, "IEEE ITRW Working Group Position Paper-Materials and Devices: WBG and UWBG Materials and Devices Are Examined in a New Working Group," *IEEE Power Electron. Mag.*, vol. 5, no. 2, pp. 45–48, Jun. 2018.

- [20] P. R. Wilson, B. Ferreira, J. Zhang, and C. DiMarino, "IEEE ITRW: International Technology Roadmap for Wide-Bandgap Power Semiconductors: An Overview," *IEEE Power Electron. Mag.*, vol. 5, no. 2, pp. 22–25, Jun. 2018.

[21] P. Shamsi, M. McDonough, and B. Fahimi, "Wide-Bandgap Semiconductor Technology: Its impact on the

- [21] P. Shamsi, M. McDonough, and B. Fahimi, "Wide-Bandgap Semiconductor Technology: Its impact on the electrification of the transportation industry.," *IEEE Electrif. Mag.*, vol. 1, no. 2, pp. 59–63, Dec. 2013.

- [22] F.-Z. Chen and D. Maksimovic, "Digital Control for Improved Efficiency and Reduced Harmonic Distortion over Wide Load Range in Boost PFC Rectifiers," in 2009 Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition, 2009, no. 1, pp. 760–766.

- [23] K. De Gusseme, D. M. Van de Sype, A. P. Van den Bossche, and J. A. Melkebeek, "Digital control of boost PFC converters operating in both continuous and discontinuous conduction mode," in 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), 2004, vol. 3, pp. 2346–2352.

- [24] Zhonghui Bing, Xiong Du, and Jian Sun, "Generalization of a nonlinear average current control method for CCM and DCM operation," in 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, 2008, pp. 51–57.

- [25] K. Pretorius and J. Biela, "Predictive Average Current Control for Power Factor Correction (PFC) Across Both Continuous (CCM) and Discontinuous (DCM) Conduction Modes," in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, p. P.1-P.10.

- [26] C. Clark, W. Eberle, and F. Musavi, "An adaptive digital controller for the mixed conduction mode boost power factor correction converter," in 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2013, no. Mcm, pp. 2712–2719.

- [27] Jingquan Chen, A. Prodic, R. W. Erickson, and D. Maksimovic, "Predictive digital current programmed control," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 411–419, Jan. 2003.

- [28] A. Suzdalenko, J. Zakis, and K. Kroics, "Transitional Average Current Sensorless Control during Peak-to-Peak Value Changes," in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, p. P.1-P.7.

- [29] S. Bhowmik, A. Van Zyl, R. Spée, and J. H. R. Enslin, "Sensorless current control for active rectifiers," IEEE

- Trans. Ind. Appl., vol. 33, no. 3, pp. 765–773, 1997.

- [30] S. L. Capecce, C. Cecati, and N. Rotondale, "A sensorless control technique for low cost AC/DC converters," in 38th IAS Annual Meeting on Conference Record of the Industry Applications Conference, 2003., 2003, vol. 3, pp. 1546–1551.

- [31] F. Javier Azcondo, A. de Castro, V. M. Lopez, and O. Garcia, "Power Factor Correction Without Current Sensor Based on Digital Current Rebuilding," *IEEE Trans. Power Electron.*, vol. 25, no. 6, pp. 1527–1536, Jun. 2010.

- [32] R. Channappanavar, S. K. Mishra, and R. K. Singh, "An Inductor Current Estimator for Digitally Controlled Synchronous Buck Converter," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4883–4894, 2019.

- [33] Woo-Cheol Lee, Taeck-Kie Lee, and Dong-Seok Hyun, "Comparison of single-sensor current control in the DC link for three-phase voltage-source PWM converters," *IEEE Trans. Ind. Electron.*, vol. 48, no. 3, pp. 491–505, Jun. 2001

- [34] Dong-Choon Lee and Dae-Sik Lim, "AC voltage and current sensorless control of three-phase PWM rectifiers," IEEE Trans. Power Electron., vol. 17, no. 6, pp. 883–890, Nov. 2002.

- [35] Y. Jie and Yu-peng Tang, "AC current sensorless control of three-phase three-wire PWM rectifiers," in 2008 7th World Congress on Intelligent Control and Automation, 2008, pp. 6516–6520.

- [36] A. Mallik and A. Khaligh, "Control of a Three-Phase Boost PFC Converter Using a Single DC-Link Voltage Sensor," *IEEE Trans. Power Electron.*, vol. 32, no. 8, pp. 6481–6492, Aug. 2017.

- [37] L. Yu-Kang, C. Huang-Jen, and O. Sheng-Yuan, "Constant-switching-frequency control of switch-mode rectifiers without current sensors," *IEEE Trans. Ind. Electron.*, vol. 47, no. 5, pp. 1172–1174, 2000.

- [38] H. Chen, "Single-Loop Current Sensorless Control for Single-Phase Boost-Type SMR," *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 163–171, Jan. 2009.

- [39] H.-C. C. Chen, C.-C. C. Lin, and J.-Y. Y. Liao, "Modified single-loop current sensorless control for single-phase boost-type SMR with distorted input voltage," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1322–1328, May 2011.

- [40] H.-C. Chen, "Interleaved Current Sensorless Control for Multiphase Boost-Type Switch-Mode Rectifier With Phase-Shedding Operation," *IEEE Trans. Ind. Electron.*, vol. 61, no. 2, pp. 766–775, Feb. 2014.

- [41] H.-C. Chen and J.-Y. Liao, "Modified Interleaved Current Sensorless Control for Three-Level Boost PFC Converter With Considering Voltage Imbalance and Zero-Crossing Current Distortion," *IEEE Trans. Ind. Electron.*, vol. 62, no. 11, pp. 6896–6904, Nov. 2015.

- [42] H.-C. Chen, C.-C. Chung, J.-Y. Liao, and S.-Y. Yu, "Input current control for bridgeless PFC converter without sensing current," 2014 IEEE Appl. Power Electron. Conf. Expo. APEC 2014, no. d, pp. 1821–1826, 2014.

- [43] P. Lamo, F. Lopez, A. Pigazo, and F. J. Azcondo, "Stability and Performance Assessment of Single-Phase T/4 PLLs With Secondary Control Path in Current Sensorless Bridgeless PFCs," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 6, no. 2, pp. 674–685, Jun. 2018.

- [44] A. Suzdalenko and J. Zakis, "Single-Loop Current Sensorless Control for Half-Bridge Based AC/DC Converter," *IETE Tech. Rev.*, vol. 33, no. 6, pp. 662–673, Nov. 2016.

- [45] A. Suzdalenko and A. Chub, "Current sensorless control for half-bridge based AC/DC PFC converter with consideration of conduction losses," *Int. J. Circuit Theory Appl.*, vol. 44, no. 12, pp. 2072–2084, Dec. 2016.

- [46] H.-C. Chen, C.-Y. Lu, G.-T. Li, and W.-C. Chen, "Digital Current Sensorless Control for Dual-Boost Half-Bridge PFC Converter With Natural Capacitor Voltage Balancing," *IEEE Trans. Power Electron.*, vol. 32, no. 5, pp. 4074–4083, May 2017.

- [47] H.-C. Chen and J.-Y. Liao, "Bidirectional Current Sensorless Control for the Full-Bridge AC/DC Converter With Considering Both Inductor Resistance and Conduction Voltages," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 2071–2082, Apr. 2014.

- [48] J. R. Rodriguez-Rodriguez, E. L. Moreno-Goytia, V. Venegas-Rebollar, D. Campos-Gaona, R. A. Felix, and L. E. Ugalde-Caballero, "Current-sensorless control of an SPWM H-Bridge-based PFC rectifier designed considering voltage sag condition," *Electr. Power Syst. Res.*, vol. 130, no. April 2017, pp. 181–191, Jan. 2016.

- [49] A. Suzdalenko, J. Zakis, and I. Steiks, "Current Sensorless Control Algorithm for Single-Phase Three-Level NPC Inverter," *Electr. Control Commun. Eng.*, vol. 7, no. 1, pp. 28–33, 2014.

- [50] A. Suzdalenko, J. Zakis, I. Steiks, and Y. Chaiko, "Verification of current sensorless control for single-phase NPC multilevel inverter," in 2015 9th International Conference on Compatibility and Power Electronics (CPE), 2015, pp. 462–466.

- [51] M. A. Santoyo-Anaya, J. R. Rodriguez-Rodriguez, E. L. Moreno-Goytia, V. Venegas-Rebollar, and N. M. Salgado-Herrera, "Current-Sensorless VSC-PFC Rectifier Control With Enhance Response to Dynamic and Sag Conditions Using a Single PI Loop," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 6403–6415, Jul. 2018.

- [52] H.-C. Chen, C.-Y. Lu, and G.-T. Li, "Design and Implementation of Three-Phase Current Sensorless Control for PFC Bridge Converter With Considering Voltage Drops of Power Semiconductors," *IEEE Trans. Ind. Electron.*, vol. 65, no. 12, pp. 9234–9242, Dec. 2018.

- [53] C.-Y. Li, N.-C. Chao, and H.-C. Chen, "Design and Implementation of Four-Switch Current Sensorless Control for Three-Phase PFC Converter," *IEEE Trans. Ind. Electron.*, vol. 67, no. 4, pp. 3307–3312, Apr. 2020.

- [54] V. M. Lopez-Martin, F. J. Azcondo, and A. de Castro, "Current error compensation for current-sensorless power factor corrector stage in continuous conduction mode," in 2012 IEEE 13th Workshop on Control and Modeling for Power Electronics (COMPEL), 2012, vol. 23612, pp. 1–8.

- [55] A. Engel, S. Nandi, and I. Panfilov, "Current sensorless control of a boost-type switch mode rectifier using an adaptive inductor model," in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015, pp. 5872–

5879

- [56] F. Lopez, V. M. Lopez-Martin, F. J. Azcondo, L. Corradini, and A. Pigazo, "Current-Sensorless Power Factor Correction With Predictive Controllers," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 7, no. 2, pp. 891–900, Jun. 2019.

- [57] A. Suzdalenko, J. Zakis, and O. Krievs, "Single-loop Current Sensorless Control with Self-detection of Conduction Losses Applied to Neutral Point Clamped Multilevel Converter," in 2019 11th International Conference on Electrical and Electronics Engineering (ELECO), 2019, no. 1, pp. 250–254.

- [58] A. Suzdalenko, "Current Sensorless Control of Front-end Bidirectional AC/DC Converter Based on Half-bridge Topology," *Electr. Control Commun. Eng.*, vol. 4, no. 1, pp. 19–25, Jan. 2013.

- [59] M. Pahlevaninezhad, P. Das, G. Moschopoulos, and P. Jain, "Sensorless control of a boost PFC AC/DC converter with a very fast transient response," in 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2013, pp. 356–360.

- [60] C. Y. Lu, Y. W. Hsu, and H. C. Chen, "Design of Current Sensorless Control for Totem-Pole Boost PFC Converter," ICPE 2019 - ECCE Asia - 10th Int. Conf. Power Electron. - ECCE Asia, vol. 3, pp. 986–991, 2019.

#### BIOGRAPHIES OF AUTHORS

Alexander Suzdalenko received B.Sc (2007), M.Sc. (2009) and Dr.sc.ing. (2013) grades in Riga Technical University in the field of electrical engineering. Currently he has post-doctoral research project working as a senior researcher with the Institute of Industrial Electronics and Electrical Engineering, Riga Technical University. He has coauthored of more than 30 scientific research paper published in international scientific journals and conference records. His research interests are related to design and control of power electronics converters. He contributed to intelligent household energy systems, studying the power balancing approaches, non-intrusive load monitoring algorithms and driving methods of LED-based lighting systems. He has practical experience working for 5 years as electronic device engineer. He is IEEE member since 2010 and joins PELS and IES societies.

E-mail: Aleksandrs.Suzdalenko@RTU.lv

Janis Zakis (M'10 – SM'14) received B. Sc., M. Sc. and Dr. Sc. ing. degrees in Electrical Engineering from Riga Technical University, Riga, Latvia, in 2002, 2004 and 2008, respectively. He is currently a Senior Researcher with the Institute of Industrial Electronics and Electrical Engineering, Riga Technical University. He is the co-author of more than 70 papers published in international journals and conference records as well as holder of several patents and utility model. His current research interests include modelling and simulation of power electronics for distributed power generation systems, energy storage applications as well as wireless power transfer systems for battery charging. E-mail: janis.zakis@ieee.org

Pavels Suskis has presented his Bachelor Science degree and Master degree in Riga Technical University, Faculty of Electrical Technologies in 2008 and 2010, respectively. His bachelor thesis was focused in "Frequency converter applying to crane drive" while master thesis and engineering project was devoted to to research and development of control system for voltage source inverter. Research interests of Pavels Suskis are in the field of photovoltaics, power electronics and control theory. He has many years of experience in industry and automation, lighting and smart control device development. Remarked as an active participator in a number of conferences. He is the co-author of more than 13 papers published in international journals and conference records as well as holder of 1 patent

E-mail: pavels.suskis@rtu.lv

Leonids Ribickis received Dr. habil. sc. ing. degree in 1994 from Riga Technical University. He has been an Academician since 2003, a full Member of the Latvian Academy of Sciences since 2007, Rector of Riga Technical University, Head of the Institute of Industrial Electronics and Electrical Drives of the Faculty of Power and Electrical Engineering at Riga Technical University, 1999. His fields of interest include power electronics, electrical drives, electrical machines, process control systems. He was leading various national and international projects. He is the author of many patents, books and publications