ISSN: 2088-8694, DOI: 10.11591/ijpeds.v14.i4.pp2195-2203

# CHB multilevel inverter with sliding mode controller for DSTATCOM applications

## Kalagotla Chenchireddy, Varghese Jegathesan

Department of Electrical and Electronics Engineering, Karunya Institute of Technology and Sciences, Tamil Nadu, India

#### **Article Info**

## Article history:

Received Mar 7, 2023 Revised Apr 20, 2023 Accepted May 11, 2023

#### Keywords:

CHB DSTATCOM Harmonics Power quality SMC

#### **ABSTRACT**

In this article, the robust nonlinear controller for cascaded H-bridge-based distributed static compensator (DSTATCOM) with input-output linearization and sliding mode control scheme using an improved voltage balancing scheme is presented. The feedback linearization method and sliding mode control scheme are used to cancel nonlinearities and deal with invariant stability due to mathematical modeling uncertainties due to DSTATCOM parameter and external load disturbance. The improved voltage balancing is used to balance the voltages of the DC side capacitor of DSTATCOM. The complete simulation studies are out to validate the control scheme based on the improved voltage balance integrated with sliding mode control under disturbances caused by the load changes and DSTATCOM parametric changes. The performance characteristics of the DSTATCOM with sliding mode controller are tested using the MATLAB/Simulink platform.

This is an open access article under the <u>CC BY-SA</u> license.

2195

#### Corresponding Author:

Kalagotla Chenchireddy

Department of Electrical and Electronics Engineering, Karunya Institute of Technology and Sciences Karunya Nagar, Coimbatore, Tamil Nadu 641114, India

Email: chenchireddy.kalagotla@gmail.com

## 1. INTRODUCTION

Currently, most of the electrical energy is processed through the power electronics-based converter system. The endless usage of power electronics converters creates reactive current and harmonics problems in the utility. The harmonics current caused by the power electronics converter creates a disturbance to the sophisticated electronics equipment [1]. Especially, the rectifier based on the diode and thyristor is used to decrease the power factor and dislocation factor of the source current. The nonlinear loads are main causes of harmonics in distribution system, these harmonics are main cause of low power factor and increases of prize electricity. In addition to this, the harmonics current leads to the overheating of the transformer, failure of the cable, torque pulsation, and derating of the adjustable speed drives. Traditionally, the harmonics current caused by the nonlinear load is eliminated with a passive filter based on the inductor and capacitor. However, the passive filter-based method is suffered from series/parallel resonance, aging problems and fixed VAR generations [2]. The harmonics current caused by the non-linear load damage the power factor correction capacitors used in an electrical line of the power system.

The harmonics current caused by the non-linear load is varying dynamically. However, the passive filter is not able to eliminate dynamically varying harmonics current [3]. In most cases, the two-level active power filters (APF) were used for reactive current demand and harmonic current elimination of the non-linear load. However, a two-level inverter-based APF is employed for low power rating and a medium power rating filter with two-level active power filters is realized with the passive filter or through a transformer [4]. Then the system of the distributed static compensator (DSTATCOM) becomes bulky and complex.

2196 □ ISSN: 2088-8694

Moreover, the two-level voltage source inverter-based DSTATCOM is not appropriate for medium and high-power function, due to the limitation of device rating.

The concept of the multilevel inverter is the addition of a few switching devices and a capacitor to achieve higher power and voltage rating of the inverter [5]. The MLI-based DSTATCOM is used for better recompense characteristics in low and high-power applications. The neutral point clamped inverter seems to be a better suitable topology for the DSTATCOM because of the availability of a common DC bus. Initially, the neutral point clamped (NPC) converter based on the diode clamped inverter is most widely used, because of the requirement of two diodes and four switching devices in the leg for the three-level inverter [6]. However, the NPC based on the diode clamped converter suffers from a high number of blocking diodes, unequal ratings of the switching devices, unequal capacitor voltages and unequal distribution of switching losses. The NPC based diode clamped inverter acts as active neutral point clamped ANPC converter. It presents the increased number of freedoms as compared to the diode clamped converter. In addition to this, the three-level active NPC inverter has better loss distribution and equal voltage stress across the switching devices of the inverter [7]. The APF based on the NPC inverter is adopted in this article. The active filter is a shunt-connected device used for compensation of harmonics caused by the non-linear load. The active filter is also known as a distributed static compensator. The DSTATCOM is the family of custom power devices used for the compensation of voltage and current harmonics caused by the nonlinear load [8]. The realization of the DSTATCOM becomes easier due to the development of the semi-conductor and digital electronics controllers.

Many control schemes had in the literature for the control of DSTATCOM. Among all control schemes such as power balance, synchronous reference frame, instantaneous reactive power (IRP) theory, symmetrical component (SC) theory and synchronous reference frame (SRF) and IRP theory are most widely reported for DSTATCOM control [9]. The soft based on type-1, type-2 fuzzy logic controller and neural network-based approach are also used for DSTATCOM control [10]. The reference current computation with the SRF scheme is the most efficient control technique for DSTATCOM. In IRP theory, all the three-phase instantaneous quantities are transformed into the bi-phase quantities for the computation of the active and reactive power of the control scheme. Subsequently, these calculated active and reactive powers are used for further computation of the reference currents for the DSTATCOM [11]. The calculated reference current is fed to the pulse width modulator to generate the switching pulses for the semi-conductor devices to track the desired source currents [12], [13]. The current harmonics eliminated by using IRP theory in distribution system. However, the computation of the harmonics active power demands the low pass filter in the control unit of the DSTATCOM [14]. The low pass filter-based techniques require a rigorous tuning process for its parameter tuning and adjustment of the same. There is no systematic method is available for parameter adjustment of the PI controller used in the SRF. In this article, the SMC is integrated with a SRF for the computation of the harmonics' active power of the control unit. The reference current after computation is fed to the pulse generating system to trace the required current with the DSTATCOM. The complete simulation study of the DSTATCOM is carried out with MATLAB/Simulink simulation with Sim power system using power electronics block sets. The different control based on conventional voltage balance scheme with PI-SRF and an improved voltage balance scheme with SMC based SRF modeled using the control system of Simulink library. The simulated response shows the effectiveness of compensation characteristics of the DSTATCOM for the elimination of harmonics cause by the load.

## 2. CONFIGURATION OF DSTATCOM TOPOLOGY

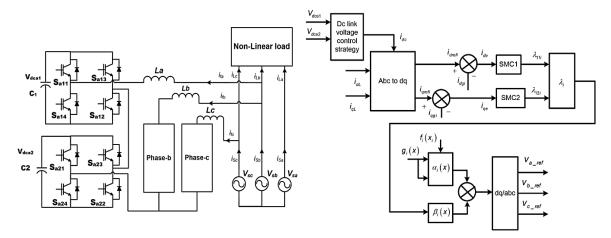

The complete electrical power system network with DSTATCOM is shown in Figure 1. The DSTATCOM system consists of electrical sources, the power circuit of DSTATCOM and load. Three phase sources having phase displacement 120°. The power circuit of DSTATCOM is realized with eleven IGBTs in each leg, three interfacing inductors and three DC link capacitors. The non-linear load is realized with three commutation inductors, and six diode bridges with a resistive-inductive load on its DC side. Generally, the nonlinear load is made up of three phase diode rectifier bridge with R-L load or R-C load.

## 2.1. Control scheme

The function of the CHB-DSTATCOM is used to compensate for the harmonics and reactive requirement of the load. The compensation currents of DSTATCOMs are estimated with a synchronous reference frame. The PI controller is used for controlling DSTATCOM and compensating harmonics. The error voltage signals directly processed by the PI controller are modulated with carrier signals. Nevertheless, due to the absence of the loop of inner current control, the direct power control method results in an overshoot of current. The current overshoot mechanism activates the protection circuit of the DSTATCOM.

The high current caused by the inappropriate control can damage the power and driver circuits of DSTATCOM. Thus, control scheme based on two loops is used in this manuscript. However, the control

scheme based on SRF has two loops; the outer loop is used for the control of voltage and the inner loop for current control. The estimated reference currents errors of the control scheme are computed based on the direct and quadrature component of the current. These current references compute based on direct and quadrature components are compared with the measured actual current to obtain the errors in current. The errors obtained from the current loop are processed through the proportional and integral controller to derive the desired direct and quadrature component of currents. The multilevel inverter-based DSTATCOM is highly nonlinear with different voltages and multiple switching to achieve multiple outputs within a single cycle of the source. The tuning of the proportional and integral controller for the highly nonlinear multilevel inverter-based DSTATCOM is a complex task. The tuning of PI controllers for two sets of the inner control loops is a more complex and tedious process. Hence, to reduce the parameter tuning of the proportional and integral controller, a control scheme with DC link voltages is controlled with an improved voltage balancing scheme using proportional and integral controllers, and the inner current controller is regulated with SMC control [9] and as shown in Figure 2.

Figure 1. DSTATCOM topology

Figure 2. Real and reactive power control with SMCbased control scheme

The improved two-loop PI control-based control scheme decreases the difficulty [15]–[20]. The multilevel inverter-based DSTATCOM is highly coupled with nonlinearity and multivariable structure. Additionally, the PI controller-based control scheme is sensitive to system limitation variations and requires a complete mathematical model of the structure. Hence, the feedback linearization technique can be used to transform the coupled nonlinear structure into the decoupled linear system. The feedback linearization is as follows. The DSTATCOM power system is presented in Figure 1. The dynamic mathematical model as given (1) and (2).

$$v_{dinv_i} - R_{f_i} i_{dg_i} - L_{f_i} \frac{di_{dg_i}}{dt} + \omega_i L_{f_i} i_{qg_i} - v_{dg_i} = 0$$

(1)

$$v_{qinv_i} - R_{f_i} i_{qg_i} - L_{f_i} \frac{di_{qg_i}}{dt} + \omega L_{f_i} i_{dg_i} - v_{qg_i} = 0$$

(2)

Consider the dynamic state-space model representation given as (3).

$$\frac{dx_i}{dt} = f_i(x_i) + g_i(x_i)u_i \tag{3}$$

By rearranging (1) and (2) into (3) with and as state variables, the coupled and nonlinear dynamic equations can be converted into the decoupled linear system.

$$f_i(x) = \begin{bmatrix} -\frac{R_{f_i}}{L_{f_i}}i_{dg} + \frac{X_{f_i}}{L_{f_i}}i_{qg_i} - \frac{1}{L_{f_i}}v_{dg_i} \\ -\frac{R_{f_i}}{L_{f_i}}i_{qg_i} + \frac{X_{f_i}}{L_{f_i}}i_{dg_i} - \frac{1}{L_{f_i}}v_{qg_i} \end{bmatrix}$$

2198 □ ISSN: 2088-8694

$$g_i(x) = \begin{bmatrix} \frac{1}{L_{f_i}} & 0\\ 0 & \frac{1}{L_{f_i}} \end{bmatrix} x_i = \begin{bmatrix} i_{d_i}\\ i_{q_i} \end{bmatrix} u_i = \begin{bmatrix} v_{dinv_i}\\ v_{qinv_i} \end{bmatrix}$$

$$\tag{4}$$

From (4), it can be concluded that there is a hypothetical decoupling existing between the currents and after linearization of the data the system as a whole can also be expressed as (5).

$$\lambda_i = A_i(x_i) + B_i(x_i)U_i \tag{5}$$

In (5)'s control input for the DSTATCOM switching operation can be expressed as (6).

$$U_{i} = \left(-B_{i}^{-1}(x_{i}) * A_{i}(x_{i})\right) + \left(B_{i}^{-1}(x_{i}) * \lambda_{i}\right) or U_{i} = \alpha_{i}(x_{i}) + \beta_{i}(x_{i})\lambda_{i}$$

(6)

Were

$$\alpha_{i}(x) = \left(-B_{i}^{-1}(x_{i}) * A_{i}(x_{i})\right) and \beta_{i}(x_{i}) = B_{i}^{-1}(x_{i})$$

$$B_{i}(x_{i}) = \begin{bmatrix} g_{i_{11}}(x_{i}) & 0 \\ 0 & g_{i_{22}}(x_{i}) \end{bmatrix} A_{i}(x_{i}) = \begin{bmatrix} f_{i_{11}}(x_{i}) \\ f_{i_{21}}(x_{i}) \end{bmatrix}$$

$$\lambda_{i} = \left[\lambda_{i_{11}}\lambda_{i_{12}}\right]^{T} = \left[\frac{d_{i_{11}}d_{i_{11}}}{dt}\frac{d_{i_{11}}d_{i_{11}}}{dt}\right]^{T}$$

(7)

In this work, the DSTATCOM is working in active and reactive power regulation mode, and the output states are taken as (8).

$$Y_i = \left[i_{dg_i} i_{qg_i}\right]^T \tag{8}$$

# 3. ADOPTION OF SLIDING MODE CONTROL

To apply the feedback linearization technique effectively, if the precise mathematical model of the system is identified. On the other hand, the parameter variation makes the system more complex and difficult. Moreover, the DSTATCOM based on a multilevel inverter has many switching, different voltage sources and parameter variations in a single cycle [21]–[25]. The accurate mathematical model and prevailing nonlinearity make the system more complex. Further, the system parameter and operating point are subjected to variation in the given course of time. However, the developed mathematical system cannot represent an accurate model of the system. To alleviate this, a sliding mode controller is combined with a control scheme. In the sliding mode controller, the equilibrium points and sliding surface are computed in every instant and the controller is operated around the sliding surface and equilibrium operating point.

# 3.1. Constitution of stability criterion and sliding surface

Once SMC is integrated into the controller, the state vector is transformed into a new state vector via the linearization process, producing a new control input. The corresponding control and switching control components of the SMC are denoted in (9). Switching control is used to minimize the error brought on by operating changes and parameter variation while the linearization procedure is utilized to compute the equivalent control.

$$U_i(t) = U_{i_{eq}}(t) + U_{i_{sw}} = U_{ieq}(t) + \rho_i \cdot \tanh(\sigma_i)$$

(9)

Where  $\rho$  is used to representing a positive constant and  $\sigma$  is used to represent the sliding surface. The sliding surface is defined to obtain the satisfactory operation of the controller. The sliding surfaces, namely  $\sigma_{i1}$  and  $\sigma_{i2}$  are to be defined, since (9) has two output states  $i_{dg_i}$  and  $i_{qg_i}$ . The state variable for the second-order system and the sliding surface  $\sigma_i(t)$  can be given as (10).

$$\sigma_i(t) = \frac{der_i(t)}{dt} + K_i er_i(t) \tag{10}$$

Where  $K_i$  is used to represent the positive constant and  $er_i(t)$  is used to represent the error in the output. In this paper, the relative degree of  $i_{dg_i}$  and  $i_{qg_i}$  is considered as 1 and the error in the utility current is taken as

a sliding surface. Hereafter,  $\sigma_{i_1} = er_{i_1} = i_{dg_i} - i_{dref_i}$  and  $\sigma_{i_2} = er_{i_2} = i_{qgi} - i_{qref_i}$ . The  $\sigma_1$  and  $\sigma_2$  are the elements of sliding surface matrix  $\sigma$  and can be given as (11).

$$\sigma_i = \begin{bmatrix} \sigma_{i1} & \sigma_{i2} \end{bmatrix} \tag{11}$$

The Lyapunov function with the sliding surface matrix can be represented as (12).

$$G_i = \frac{1}{2}\sigma_i^2 \tag{12}$$

As per the Lyapunov stability criterion, "if the function  $G_i$  is a positive definite function and its derivative function, i.e.,  $\frac{dG_i}{dt}$  is a negative definite function, then the system is said to be asymptotically stable".

$$i.e., \frac{dG_i}{dt} = \sigma_i \dot{\sigma_i}^T < 0, \tag{13}$$

To fulfill the condition  $\sigma_i \dot{\sigma_i}^T < 0 \dot{\sigma_i}$  can be represented as  $\rho \tanh(\sigma)$ .

$$\dot{\sigma}_{i1} = -\rho_{i1} \tanh(\sigma_{i1}) \operatorname{and} \dot{\sigma}_{i2} = -\rho_{i1} \tanh(\sigma_{i2}) \tag{14}$$

Substituting (11) into (14).

$$\dot{\sigma}_{i1} = -\rho_{i1} \tanh(i_{darefi} - i_{dgi}) \operatorname{and} \dot{\sigma}_{i2} = -\rho_{i1} \tanh(i_{qarefi} - i_{qgi})$$

$$\tag{15}$$

With the attained new dynamics using SMC, the state vector can be given as (16).

$$\lambda_{i1} = \begin{bmatrix} \lambda_{i11} \\ \lambda_{i12} \end{bmatrix} = \begin{bmatrix} \rho_{i1} \tanh(i_{dgrefi} - i_{dgi}) \\ -\rho_{i1} \tanh(i_{ggrefi} - i_{ggi}) \end{bmatrix}$$

$$(16)$$

$i_{dgrefi}$  and  $i_{qgrefi}$  can be found from (3). If the variations of the parameter of the Satcom, then the corresponding change in the system matrix is  $\Delta A_i$ , and the system can be represented as (17).

$$\dot{X}_i = (A_i + \Delta A_i)X_i + B_i(U_{ieg} + U_{isw}) \tag{17}$$

$$\dot{X}_i = A_i X_i + B_i U_{ieq} + \Delta A_i X_i + B_i \rho_i \tanh(\sigma_i) \tag{18}$$

The system parameter dependence part  $\Delta A_i X_i$  is compensated with the switching part  $B_i \rho_i \tanh(\sigma_i)$ . Therefore, the boundary condition for the selection of  $\rho$  is:

$$B_i \rho_i > \Delta A_i X_i or p_i > \left[ B_i^{-1} \Delta A_i X_i \right] \tag{19}$$

Where  $\rho$  represents a positive constant and is used to cancel out the error caused by the parameter deviations, operating point variations and disturbances caused by the load. The value of  $\rho$  should be large, which results in smooth transition action  $tanh(\sigma)$  into a hard switching function. The hard switching results in chattering in the output. However, the very small value  $\rho$  is not able to cancel the variation caused by the parameter and operating point dependencies. Additionally, the small value  $\rho$  will cause slow response.

#### 4. DC VOLTAGE BALANCING

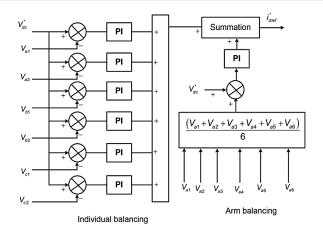

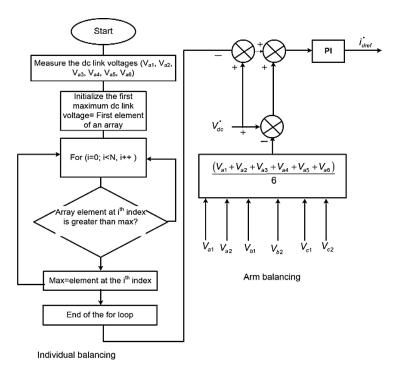

The voltage balancing scheme of the CHB-based DSTATCOM is shown in Figure 3 and Figure 4 respectively. The conventional scheme of voltage balancing consists of individual balancing and average balancing. Individual balancing is used for regulating each capacitor voltage. The average balancing is used for balancing and regulating each leg's voltages of the CHB DSTATCOM. The proposed scheme of voltage regulation of CHB-based DSTATCOM is shown in Figure 4. The scheme consists of individual balancing and average balancing. The individual balancing is used to estimate the maximum value of the capacitor voltage and compare it with a reference voltage. Each time maximum value capacitor voltage changes and this is repeated until the voltage of the capacitor is balanced. Similarly, average balancing is used for each leg voltage balancing of CHB-based DSTATCOM.

2200 □ ISSN: 2088-8694

Figure 3. Conventional voltage balancing

Figure 4. Improved voltage balancing scheme

# 5. SIMULATION RESULTS

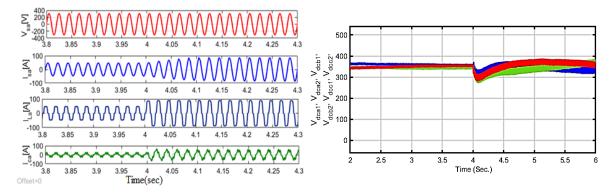

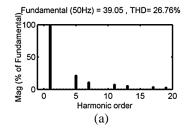

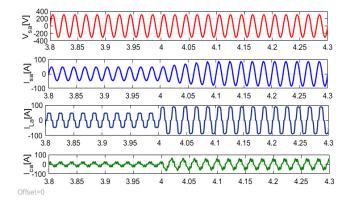

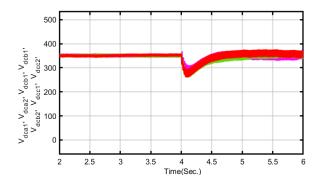

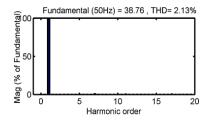

The complete electrical power system with DSTATCOM is shown in Figure 1. The DSTATCOM three-phase electrical sources are realized with electrical sources block set of Sim power system library. The nonlinear is realized with power electronics and elements library of the Sim power system. The DSTATCOM is also realized with the power electronics and elements of the Sim power system library of Simulink. The two different control schemes of the DSTATCOM are created with the control blocks of Simulink library. The simulated response of DSTATCOM with conventional SRF is shown in Figure 5. Initially, before t = 4 sec, the source current follows the load current. The load current wave form is stepped in shape and highly distorted. The triple harmonic components are presented in load. At t = 4 sec, DSTATCOM is switched-on, and the source current waveform tends to be nearly sinusoidal waveform and follows the source voltage waveform. The power factor of the voltage and current waveform is almost unity. The time required for the source current to reach steady is almost 3-4 cycles. The corresponding DC side voltage of the DSTATCOM capacitor is shown in Figure 5. The time required for the DC voltage of DSTATCOM to reach steady is almost 0.05 sec. the THD of the source current before harmonics elimination is shown in Figure 6. Figure 7(a) shows the value of THD of source current before harmonics elimination DSTATCOM is 26.76%. After

compensation with DSTATCOM, Figure 7(b) shows the THD of source current is reduced to 2.13% as depicted Figure 7.

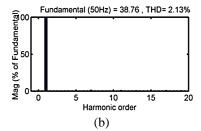

The current waveforms of DSTATCOM with SMC-based SRF are shown in Figure 8. Initially, before t=0.15 sec, the source current follows the load current. The waveform of the load current is stepped in shape and highly distorted. This characteristic is caused by the presence of triple harmonics components in the load current. At t=0.15 sec, DSTATCOM is switched-on, and the source current waveform tends to be nearly sinusoidal waveform and follows the source voltage waveform. The power factor of the voltage waveform and current waveform is unity. The time required for the source current to reach steady is almost 2-3 cycles. The corresponding DC side voltage of the DSTATCOM capacitor is shown in Figure 9. The time required for the DC voltage of DSTATCOM to reach steady is almost 0.05 sec. The total harmonics distortion of the source current before harmonics elimination is shown in Figure 7. The value THD of source current before harmonics elimination DSTATCOM is 26.76%. After compensation with DSTATCOM, the THD of source current is reduced to 2.13% as depicted in Figure 10. From the characteristics of DSTATCOM, the simulated results obtained with the SMC-based control scheme outperform that of the conventional SRF schemes.

Figure 5. Simulated waveform

Figure 6. DC link voltage

Figure 7. Source current THD (a) THD value without DSTATCOM and (b) THD value with DSTATCOM

Figure 8. Simulated waveform

2202 ISSN: 2088-8694

Figure 9. DC link voltage

Figure 10. Source current with compensation

## 6. CONCLUSION

In this paper, the DSTATCOM based on a reduced switch count converter based is adopted for current harmonics elimination in the source current of the electrical system. The simulation study is carried out to study the comparative show of the DSTATCOM with two different voltage balancing schemes with SMC controller-based control schemes. The comparative results show that the improved voltage balancing control with an SMC-based SRF control scheme outperforms that of conventional voltage balancing with SMC controller-based SRF in dynamic conditions. The CHB-MLI-based DSTATCOM with improved voltage balancing with the SMC-SRF control scheme has a better steady-state response than that of the conventional control scheme. The firing pulse of CHB-MLI-based DSTATCOM is generated with sinusoidal pulse width modulation.

## REFERENCES

- M. Rawa et al., "Dual input switched-capacitor-based singlephase hybrid boost multilevel inverter topology with reduced number of components," *IET Power Electronics*, vol. 13, no. 4, pp. 881–891, 2020, doi: 10.1049/iet-pel.2019.0826.

- [2] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel DC voltage sources," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2643–2650, 2010, doi: 10.1109/TIE.2009.2030204.

- [3] M. D. Siddique, S. Mekhilef, N. M. Shah, and M. A. Memon, "Optimal Design of a New Cascaded Multilevel Inverter Topology With Reduced Switch Count," *IEEE Access*, vol. 7, pp. 24498–24510, 2019, doi: 10.1109/ACCESS.2019.2890872.

- [4] M. D. Siddique et al., "Low Switching Frequency Based Asymmetrical Multilevel Inverter Topology with Reduced Switch Count," IEEE Access, vol. 7, pp. 86374–86383, 2019, doi: 10.1109/ACCESS.2019.2925277.

- [5] C. Dhanamjayulu, G. Arunkumar, B. Jaganatha Pandian, and S. Padmanaban, "Design and implementation of a novel asymmetrical multilevel inverter optimal hardware components," *International Transactions on Electrical Energy Systems*, vol. 30, no. 2, 2020, doi: 10.1002/2050-7038.12201.

- [6] M. Saeedian, J. Adabi, and S. M. Hosseini, "Cascaded multilevel inverter based on symmetric-asymmetric DC sources with reduced number of components," *IET Power Electronics*, vol. 10, no. 12, pp. 1468–1478, 2017, doi: 10.1049/iet-pel.2017.0039.

- [7] M. Jayabalan, B. Jeevarathinam, and T. Sandirasegarane, "Reduced switch count pulse width modulated multilevel inverter," *IET Power Electronics*, vol. 10, no. 1, pp. 10–17, 2017, doi: 10.1049/iet-pel.2015.0720.

- [8] M. F. Kangarlu and E. Babaei, "Cross-switched multilevel inverter: An innovative topology," *IET Power Electronics*, vol. 6, no. 4, pp. 642–651, 2013, doi: 10.1049/iet-pel.2012.0265.

- [9] A. Moharana and P. K. Dash, "Input-output linearization and robust sliding-mode controller for the VSC-HVDC transmission link," *IEEE Transactions on Power Delivery*, vol. 25, no. 3, pp. 1952–1961, 2010, doi: 10.1109/TPWRD.2010.2042469.

- [10] B. Xiao, L. Hang, J. Mei, C. Riley, L. M. Tolbert, and B. Ozpineci, "Modular Cascaded H-Bridge Multilevel PV Inverter with Distributed MPPT for Grid-Connected Applications," *IEEE Transactions on Industry Applications*, vol. 51, no. 2, pp. 1722–1731, 2015, doi: 10.1109/TIA.2014.2354396.

- [11] L. Ben-Brahim, A. Gastli, M. Trabelsi, K. A. Ghazi, M. Houchati, and H. Abu-Rub, "Modular Multilevel Converter Circulating Current Reduction Using Model Predictive Control," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 6, pp. 3857–3866, Jun. 2016, doi: 10.1109/TIE.2016.2519320.

- [12] A. Inoue, M. Deng, K. Matsuda, and B. Bandyopadhyay, "Design of a Robust Sliding Mode Controller using Multirate Output Feedback," pp. 200–203, 2007, doi: 10.1109/isic.2007.4359734.

- [13] D. Suresh and S. P. Singh, "Type-2 Fuzzy Logic Controlled Three-level Shunt Active Power Filter for Power Quality Improvement," *Electric Power Components and Systems*, vol. 44, no. 8, pp. 873–882, 2016, doi: 10.1080/15325008.2016.1138158.

- [14] K. Santhosh, K. Chenchireddy, P. Vaishnavi, A. Greeshmanth, V. M. Kumar, and P. N. Reddy, "Time-Domain Control Algorithms of DSTATCOM in a 3-Phase, 3-Wire Distribution System," IDCIoT 2023 - International Conference on Intelligent Data Communication Technologies and Internet of Things, Proceedings, pp. 781–785, 2023, doi: 10.1109/IDCIoT56793.2023.10053535.

- [15] K. Chenchireddy, V. Kumar, K. R. Sreejyothi, and P. Tejaswi, "A Review on D-STATCOM Control Techniques for Power Quality Improvement in Distribution," *Proceedings of the 5th International Conference on Electronics, Communication and Aerospace Technology, ICECA 2021*, pp. 201–208, 2021, doi: 10.1109/ICECA52323.2021.9676019.

- [16] V. Quan Nguyen, T. Lam Le, and M. Tam Nguyen, "Sliding Mode Control for Cascaded Multilevel Inverters," Proceedings of 2019 International Conference on System Science and Engineering, ICSSE 2019, pp. 495–500, 2019, doi: 10.1109/ICSSE.2019.8823138.

- [17] M. O. Saad et al., "Design and Control of Novel Grid Tied Multilevel Filter-Less Inverter Using Current Based Sliding Mode Control," IEEE Access, vol. 10, pp. 115555–115570, 2022, doi: 10.1109/ACCESS.2022.3218338.

- [18] K. Y. Lo and J. Y. Lin, "Five-Level Step-Up Switched-Capacitor Grid-Connected Inverter," IEEE Journal of Emerging and Selected Topics in Power Electronics, 2023, doi: 10.1109/JESTPE.2023.3242600.

- [19] K. Chenchireddy and V. Jegathesan, "ANFIS Based Reduce Device Count DSTATCOM," Journal of Applied Science and Engineering (Taiwan), vol. 26, no. 11, pp. 1657–1666, 2023, doi: 10.6180/jase.202311\_26(11).0014.

- [20] V. Kumar, K. Chenchireddy, M. R. Reddy, B. Prasad, B. Preethi, and D. S. Raj, "Power Quality Enhancement In 3-Phase 4-Wire Distribution System Using Custom Power Devices," 8th International Conference on Advanced Computing and Communication Systems, ICACCS 2022, pp. 1225–1228, 2022, doi: 10.1109/ICACCS54159.2022.9785339.

- [21] M. B. Lakshmi, K. Deepak, M. Sindhuja, K. Mounika, D. Parthyusha, and O. Sowjanya, "Enhancement of Power Quality in Distribution System using DSTATCOM," in 2023 International Conference on Sustainable Computing and Data Communication Systems (ICSCDS), Mar. 2023, pp. 1679–1684. doi: 10.1109/ICSCDS56580.2023.10104968.

- [22] X. Xu, M. Bishop, J. Sember, M. J. S. Edmonds, and C. Hao, "Dynamic modeling and simulation of distributed static compensators in system impact studies," *Asia-Pacific Power and Energy Engineering Conference*, APPEEC, 2013, doi: 10.1109/APPEEC.2013.6837111.

- [23] J. Srikakolapu, S. R. Arya, and R. Maurya, "DSTATCOM with Gradient Compared p-norm Least Mean Square Algorithm and Estimated PI Gains," 2022 IEEE Global Conference on Computing, Power and Communication Technologies, GlobConPT 2022, 2022, doi: 10.1109/GlobConPT57482.2022.9938316.

- [24] K. D. Young, V. I. Utkin, and Ü. Özgüner, "A control engineer's guide to sliding mode control," *IEEE Transactions on Control Systems Technology*, vol. 7, no. 3, pp. 328–342, 1999, doi: 10.1109/87.761053.

- [25] V. Kumar, K. Chenchireddy, K. R. Sreejyothi, T. Usha, A. Venkatasaireddy, and B. Rakesh, "Distribution System Power Quality Improvement using IRP Theory," *Proceedings - 7th International Conference on Computing Methodologies and Communication*, ICCMC 2023, pp. 1450–1454, 2023, doi: 10.1109/ICCMC56507.2023.10084162.

#### **BIOGRAPHIES OF AUTHORS**

Kalagotla Chenchireddy is received the. B-Tech and M-tech from JNTU Hyderabad, Hyderabad, india, in 2011 and 2013 respectively and pursuing Ph.D. in Karunya Institute of Technology and Sciences, Karunya nagar, Coimbatore, TN, India. He is working presently as Assistant Professor in Teegala Krishna Reddy Engineering College, Hyderabad, India. He has presented technical papers in various National and International Journals and Conferences. His area of interest includes power electronics, power quality; multilevel inverters. He is regular reviewer ISA Transactions, Cybernetics and Systems SCIE and IJPEDS journals. He can be contacted at email: chenchireddy.kalagotla@gmail.com.