# Performance analysis for induction motor fed by reduced switch symmetrical multilevel inverter topology

# Ujwala Gajula<sup>1</sup>, Kalpanadevi Manivannan<sup>1</sup>, N. Malla Reddy<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, Faculty of Engineering and Technology, Annamalai University, Annamalainagar, India <sup>2</sup>Department of Electrical and Electronics Engineering, G. Narayanamma Institute of Technology and Science, Hyderabad, India

# Article Info ABSTRACT Article history: Due to its capacity to supply more voltage levels than conventional 2-level

Received Aug 3, 2023 Revised Sep 29, 2023 Accepted Oct 5, 2023

# Keywords:

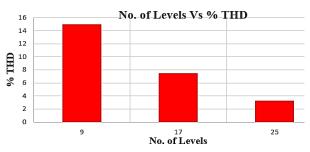

Grid Multilevel inverters Power quality Reduced switch MLI Renewable energy systems Due to its capacity to supply more voltage levels than conventional 2-level inverters, multilevel inverters have attracted a lot of attention in recent years. Multilevel inverters may produce output waveforms that nearly approximate sinusoidal waveforms because to this characteristic, which also significantly lowers harmonic distortion. In many different power conversion systems, the introduction of reduced switch symmetrical multilevel inverter topologies has drawn significant interest. Numerous benefits, such as higher output voltage quality, reduced harmonic distortions, and increased power conversion efficiency, are provided by these novel topologies. The inclusion of these inverters in the feeding of induction motors is one of their many prominent uses. In this paper, a generalized topology is presented that generates nine levels using nine switching devices. To reduce complexity, switching pulses are generated using a low frequency pulse width modulation technique. MATLAB/Simulink is used to analyze the performance assessment of a unique three-phase symmetric cascaded multilevel inverter-based reduced switch symmetrical inverter fed induction motor drive, brushless DC (BLDC) motor and grid has been verified. According to the findings the total harmonic distortion (THD) is found to be 15% for a three-phase system and as the number of levels increases to 17 level the THD is 7.10%.

This is an open access article under the <u>CC BY-SA</u> license.

# Corresponding Author:

Ujwala Gajula

Department of Electrical Engineering, Faculty of Engineering and Technology, Annamalai University Annamalainagar, Tamil Nadu, India Email: gjujwala@gmail.com

# 1. INTRODUCTION

Multilevel inverters (MLIs) have attracted a lot of attention in recent years for their potential use in electrical and industrial systems, as well as their high efficiency, simplicity of operation, and lack of electromagnetic interference (EMI). Additionally, MLIs may be quickly connected to renewable energy sources, including photovoltaic solar panels and wind turbines [1]–[3]. Numerous MLI topologies have been suggested by scholars since the 1970s. The 2-level inverter, which is the prevalent kind of inverter, has some disadvantages, including high total harmonic distortion (THD), the need for bulky filters, high voltage ratings for switches, high switchingfrequencies, and electromagnetic interference. In addition, because of the high voltage specification and stresson switches, the 2-level inverter will only be utilized for low and medium voltage applications. MLI is created to enable DC/AC conversion with much better efficiency and less THD [4]–[6] in order to get beyond these restrictions.

Reduced switch MLIs (RSMLI) are a class of MLIs that aim to reduce number of switch count required togenerate the multilevel waveform, thereby reducing complexity and cost of the circuit [7]–[10]. Reduced switch MLIs achieve this by using different techniques to synthesize the multilevel waveform with

fewer switches. This is done by utilizing various techniques such as capacitor voltage balancing, the flying capacitortechnique, or the diode-clamped technique. Reduced switch MLIs are used in high power applications such as motor drives, renewable energy sources (RES), and power grid applications [11]–[13]. These applications require high power efficiency, low harmonic distortion, and improved power quality, which are all benefits of MLIs.

In general, reduced switch MLIs outperform traditional 2-level inverters and are increasingly used in contemporary power electronics applications [14]–[16]. New topologies and control schemes are being developed and put into practice, and they remain a focus of ongoing research and development in the field of power electronics [17]–[19]. In this approach, a number of topologies with symmetric and asymmetric configurations were suggested. While in the latter, the magnitudes are diverse, in the former, all DC sources have the same magnitude. Various three phase multilevel inverter topologies were as presented in [20], [21]. Symmetric and asymmetric cascaded H-bridge topology was proposed in Khosroshahi [22].

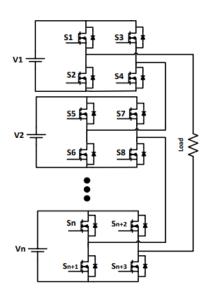

Another form of MLI that has two separate components is a hybrid multilevel inverter. The level generation, or first phase, creates a staircase voltage with unidirectional polarity. To do this, a certain combination of DC source switches is used to generate a range of voltage levels. Second component changes the polarity, producing both positive and negative voltage across the load. Typically, an H-bridge inverter is employed for this. Traditional cascaded H-bridge MLI structure is seen in Figure 1. The (1) provides the number of switches needed for a certain output voltage level. There are a total of switches in each leg:

$$NSW = 2(N-1) \tag{1}$$

where N = Number of levels.

Figure 1. Conventional cascaded H-Bridge MLI

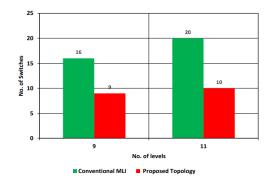

An enhanced topology based on cascaded H-bridge shown in Figure 2 was as introduced in previous researches [23]–[25]. The number of switches and sources used can be determined using the equations provided which is given in (2) and (3) and the output voltage levels is dependent on the number of cells. Table 1 gives the comparison of the proposed system's switch requirements with those for the standard H-bridge at various levels. This topology significantly reduces the number of switches that are required when associated to the classical cascade H-bridge MLI. Comparing the switch count utilized in various MLI's with suggested MLI topologies is shown in Table 2.

$$N=2n+3$$

(2)

$K=N-2$  (3)

Where N = number of switches and n = number of sources.

Figure 2. Hybrid cascaded H-bridge MLI

Table 1. Comparison of proposed system's switch requirements with those for the standard H-bridge at

|               | various levels        |                   |  |  |

|---------------|-----------------------|-------------------|--|--|

| No. of levels | System                | Switches required |  |  |

| 7             | Conventional H-Bridge | 12                |  |  |

|               | Proposed MLI [12]     | 9                 |  |  |

|               | Proposed MLI          | 8                 |  |  |

| 9             | Conventional H-Bridge | 16                |  |  |

|               | Proposed MLI [12]     | 11                |  |  |

|               | Proposed MLI          | 9                 |  |  |

# 2. PROPOSED REDUCED SWITCH COUNT MLI TOPOLOGY

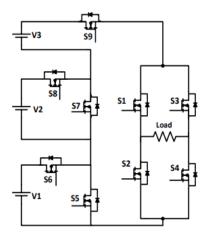

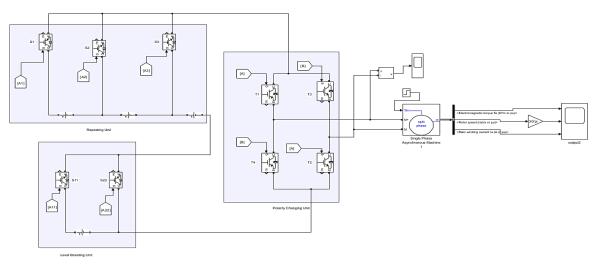

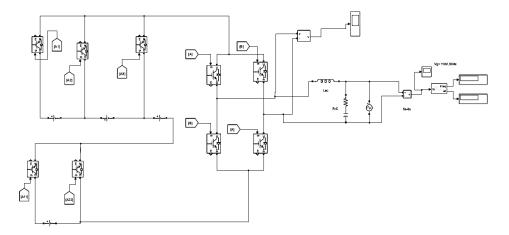

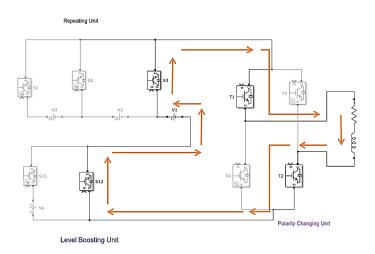

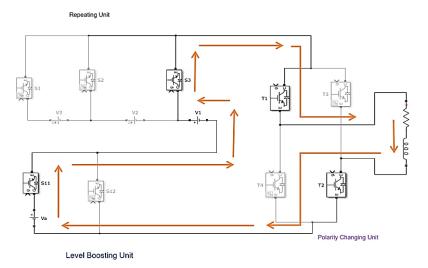

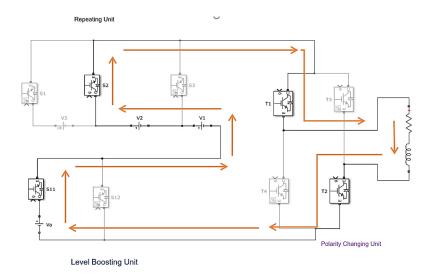

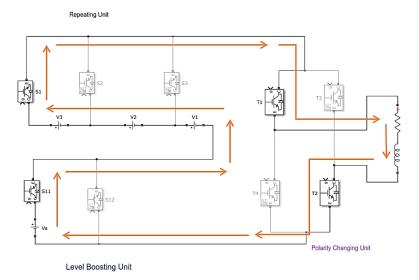

The projected RSMLI fed induction motor drive strategy is depicted in Figure 3 and brushless DC (BLDC) motor load is shown in Figure 4 and grid connected shown in Figure 5. The Proposed RSMLI topology consists a typical H-bridge which is used as a polarity changing unit (PCU) to provide both +ve and -ve output voltage levels. The PCU is also in charge of producing a zero-voltage level at the output. This is done by turning on T2 and T4 at the same time for a certain amount of time. The switching states of the switches are listed in Table 2.

Figure 3. Single phase reduced switch MLI fed induction motor

For symmetrical arrangement, the suggested MLI is taken into consideration. The magnitude of the DC voltage sources determines the number of output voltage levels. The magnitude of each DC source, is chosen as  $V_{dc}$ . The current conduction path is shown in Figures 6-9. When switch S22 and S3 are turned ON voltage V1 appears. When switch S22 turned OFF and switch S11 turned ON along with switch S3 voltages

Va and V1 are connected in series and voltage 2 V<sub>dc</sub> appears across the load. Now the switch S3 turned OFF and switch S2 ON along with switch S11 the voltages Va, V1 and V2 are in series and a total voltage of 3 V<sub>dc</sub> appears across load. Switch S2 is turned OFF and switch S1 is turned ON along with switch S11 voltages Va, V1, V2 and V3 are in seriesso a total voltage of 4 V<sub>dc</sub> appears across the load.

Figure 4. Three phase RSMLI fed BLDC motor

Figure 5. Grid connected single phase RSMLI

Figure 6. Current conduction path when Va Voltage is acting

Figure 7. Current conduction path when V1 and Va Voltages are acting

Figure 8. Current conduction path when V1, V2 and Va voltages are acting

Figure 9. Current conduction path when V1, V2, V3 and Va voltages are acting

Performance analysis for induction motor fed by reduced switch symmetrical ... (Ujwala Gajula)

| ~~ |            |    |            | o   |     |    |    |    | - • p | cating .           |

|----|------------|----|------------|-----|-----|----|----|----|-------|--------------------|

|    | <b>S</b> 1 | S2 | <b>S</b> 3 | S11 | S12 | T1 | T2 | T3 | T4    | V <sub>0</sub>     |

|    | 0          | 0  | 1          | 0   | 1   | 1  | 1  | 0  | 0     | $+ V_{dc}$         |

|    | 0          | 0  | 1          | 1   | 0   | 1  | 1  | 0  | 0     | $+2 V_{dc}$        |

|    | 0          | 1  | 0          | 1   | 0   | 1  | 1  | 0  | 0     | $+3 V_{dc}$        |

|    | 1          | 0  | 0          | 1   | 0   | 1  | 1  | 0  | 0     | $+4 V_{dc}$        |

|    | 0          | 0  | 0          | 0   | 0   | 1  | 0  | 1  | 0     | 0                  |

|    | 0          | 0  | 1          | 0   | 1   | 0  | 0  | 1  | 1     | - V <sub>dc</sub>  |

|    | 0          | 0  | 1          | 1   | 0   | 0  | 0  | 1  | 1     | $-2 V_{dc}$        |

|    | 0          | 1  | 0          | 1   | 0   | 0  | 0  | 1  | 1     | $-3 V_{dc}$        |

| _  | 1          | 0  | 0          | 1   | 0   | 0  | 0  | 1  | 1     | -4 V <sub>dc</sub> |

Table 2. Switching table with three repeating units

### 3. SIMULATION RESULTS

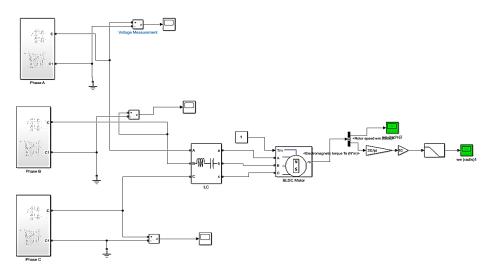

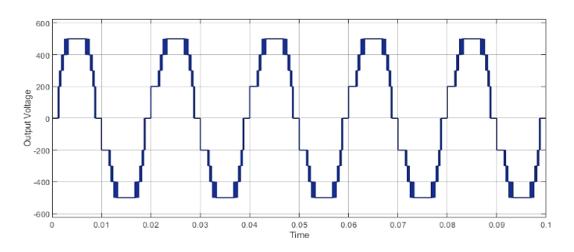

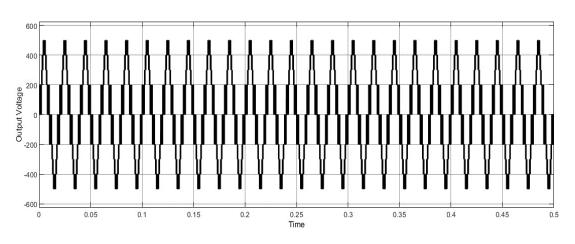

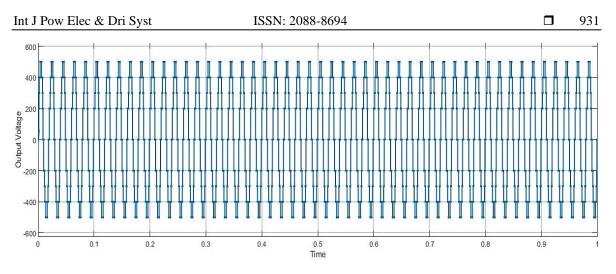

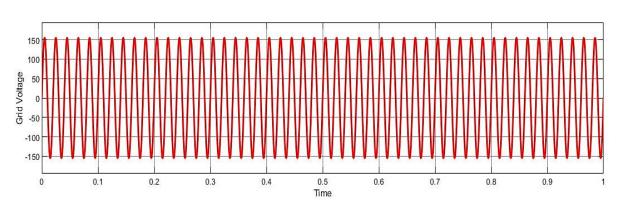

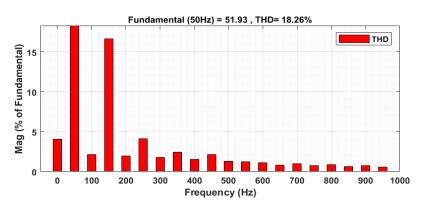

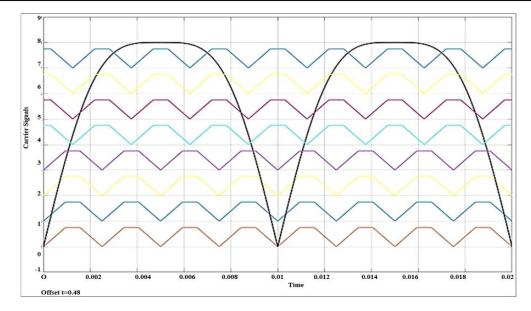

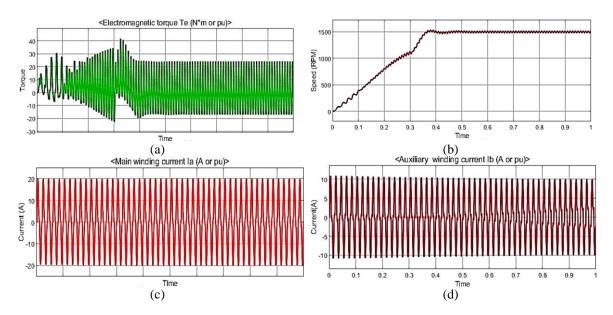

With a 10 ohm and 100 mH RL load, simulation is used to evaluate the performance of the proposed topology. The recommended topology is designed to work as 9-level single-phase and three-phase inverters. Figure 10 displays the simulation results for the proposed decreased switch count MLI architecture phase voltage for induction motor load, Figure 11 shows the output voltage for BLDC motor Load and Figure 12 depicts output voltage when RSMLI is grid connected and Figure 13 shows grid voltage. In the suggested design, pulse width modulation (PWM) pulses are produced using the multicarrier pulse width modulation technique (MCPWM) switching method with a carrier frequency of 1 kHz in order to achieve a 9-level output voltage. Figure 14 shows the %THD of the suggested decreased switch count MLI architecture for 9 levels. The% THD for various amplitude modulation indices isshown in Table 3.

Figure 10. Output phase voltage waveform of the proposed topology with IM load

Figure 11. Output phase voltage waveform of RSMLI with BLDC motor load

Figure 12. Output phase voltage waveform of RSMLI when grid connected

Figure 13. Grid voltage

Figure 14. % THD for nine level RSMLI

The PWM generating strategy employed in the simulation investigation is shown in Figure 15. The PWM generating strategy is detailed for a single 9-level inverter that uses a single modulating waveform to produce positive and negative cycle pulses together with a 4-triangle carrier. To create the basic PWM pulses, the sine wave and every triangle component are evaluated and logically XORed. The switches in the suggested architecture are then given these base PWM pulses, which are used to synthesize each level of the output voltage. Figure 16. gives the simulation results of induction motor main winding current, auxiliary winding current, torque, and rotor speed. The graphs in Figures 17 and 18 compare the switch count to the number of levels for conventional and proposed topologies, respectively, and the number of levels to the percentage of THD.

Performance analysis for induction motor fed by reduced switch symmetrical ... (Ujwala Gajula)

Figure 15. Phase disposition PWM with modified carrier

Figure 16. Simulation results of RSMLI fed induction motor drive (a) torque, (b) rotor speed, (c) main winding current, and (d) auxiliary winding current

proposed topology

## 4. CONCLUSION

To support high-power applications at medium voltage, a unique architecture has been developed. The reduction of the overall power components required for greater voltage levels for various loads is the major goal of this work. The multi-level inverter (MLI)'s revolutionary design makes use of four sources of direct current (dc). The present route of this design is intended to have fewer switches. In comparison to conventional topologies, the suggested architecture seeks to provide more voltage levels with fewer components. Along with the flow path, the operational modes necessary to produce nine tiers are thoroughly detailed. A single voltage source may beadded using just one switching device in the proposed topology, which reduces power loss by having fewer switches in the current conduction route.

#### REFERENCES

- M. Samy, M. Mokhtar, N. H. Saad, and A. A. El-Sattar, "Modified hybrid PWM technique for cascaded MLI and cascaded MLI application for DTC drive," *International Journal of Power Electronics and Drive Systems*, vol. 13, no. 1, pp. 47–57, 2022, doi: 10.11591/ijpeds.v13.i1.pp47-57.

- [2] A. Prayag and S. Bodkhe, "A comparative analysis of classical three phase multilevel (five level) inverter topologies," 2017, doi: 10.1109/ICPEICES.2016.7853567.

- [3] R. K. Antar, T. A. Hussein, and A. M. Abdullah, "Design and implementation of reduced number of switches for new multilevel inverter topology without zero-level state," *International Journal of Power Electronics and Drive Systems*, vol. 13, no. 1, pp. 401– 410, 2022, doi: 10.11591/ijpeds.v13.i1.pp401-410.

- [4] S. Maurya, D. Mishra, K. Singh, A. K. Mishra, and Y. Pandey, "An Efficient Technique to reduce Total Harmonics Distortion in Cascaded H- Bridge Multilevel Inverter," *Proceedings of 2019 3rd IEEE International Conference on Electrical, Computer and Communication Technologies, ICECCT 2019*, 2019, doi: 10.1109/ICECCT.2019.8869424.

- [5] A. Kahwa, H. Obara, and Y. Fujimoto, "Design of 5-level reduced switches count H-bridge multilevel inverter," in *Proceedings 2018 IEEE 15th International Workshop on Advanced Motion Control, AMC 2018*, 2018, pp. 41–46, doi: 10.1109/AMC.2019.8371060.

- [6] A. K. Koshti and M. N. Rao, "A brief review on multilevel inverter topologies," in 2017 International Conference on Data Management, Analytics and Innovation, ICDMAI 2017, 2017, pp. 187–193, doi: 10.1109/ICDMAI.2017.8073508.

- [7] G. D. Prasad, V. Jegathesan, and P. V. V. Rama Rao, "Hybrid multilevel DC link inverter with reduced power electronic switches," *Energy Procedia*, vol. 117, pp. 626–634, 2017, doi: 10.1016/j.egypro.2017.05.162.

- [8] S. S. A. Dangeti, C. K. P. Sekharamantry, V. K. Bayanti, B. A. Raju Ch, K. V. S. R. Murthy, and A. Tirupathi, "A cascaded converter using hybrid cells and h-bridge structure," *Bulletin of Electrical Engineering and Informatics*, vol. 10, no. 6, pp. 2972–2979, 2021, doi: 10.11591/eei.v10i6.2783.

- [9] K. M. Abdulhassan and O. Y. K. Al-Atbee, "Improved modified a multi-level inverter with a minimum total harmonic distortion," *Bulletin of Electrical Engineering and Informatics*, vol. 11, no. 2, pp. 672–680, 2022, doi: 10.11591/eei.v11i2.3466.

- [10] M. A. Hutabarat, S. Hasan, and A. H. Rambe, "Design and simulation hybrid filter for 17 level multilevel inverter," no. June, 2020, doi: 10.11591/eei.v9i3.890.

- [11] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7, pp. 2197–2206, 2010, doi: 10.1109/TIE.2009.2030767.

- [12] S. Umashankar, T. S. Sreedevi, V. G. Nithya, and D. Vijayakumar, "A New 7-Level Symmetric Multilevel Inverter with Minimum Number of Switches," ISRN Electronics, vol. 2013, pp. 1–8, 2013, doi: 10.1155/2013/476876.

- [13] M. H. Mandol, S. P. Biswas, T. K. Roy, M. K. Hosain, and M. F. Kibria, "A Novel Modulation Scheme to Improve the Injected Power Quality for Modular Multilevel Medium Voltage Grid-Tied Power Converters," 2019, doi: 10.1109/ECACE.2019.8679198.

- [14] S. D. Ravanan, E. Arivukannu, S. P. Thankappan, and R. Muthiah, "Harmonic performance analysis of a wind driven micro grid inverter," *International Journal of Ambient Energy*, vol. 43, no. 1, pp. 3497–3506, 2022, doi: 10.1080/01430750.2020.1839547.

- [15] H. P. Vemuganti, D. Sreenivasarao, S. K. Ganjikunta, H. M. Suryawanshi, and H. Abu-Rub, "A survey on reduced switch count multilevel inverters," *IEEE Open Journal of the Industrial Electronics Society*, vol. 2, pp. 80–111, 2021, doi: 10.1109/OJIES.2021.3050214.

- [16] M. M. Hasan, A. Abu-Siada, and M. S. A. Dahidah, "A Three-Phase Symmetrical DC-Link Multilevel Inverter With Reduced Number of DC Sources," *IEEE Transactions on Power Electronics*, vol. 33, no. 10, pp. 8331–8340, Oct. 2018, doi: 10.1109/TPEL.2017.2780849.

- [17] A. Hota, S. Jain, and V. Agarwal, "An Improved Three-Phase Five-Level Inverter Topology with Reduced Number of Switching Power Devices," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 4, pp. 3296–3305, 2018, doi: 10.1109/TIE.2017.2758722.

- [18] T. Qanbari and B. Tousi, "Single-Source Three-Phase Multilevel Inverter Assembled by Three-Phase Two-Level Inverter and Two Single-Phase Cascaded H-Bridge Inverters," *IEEE Transactions on Power Electronics*, vol. 36, no. 5, pp. 5204–5212, 2021, doi: 10.1109/TPEL.2020.3029870.

- [19] C. Dhanamjayulu, P. Kaliannan, S. Padmanaban, P. K. Maroti, and J. B. Holm-Nielsen, "A New Three-Phase Multi-Level Asymmetrical Inverter with Optimum Hardware Components," *IEEE Access*, vol. 8, pp. 212515–212528, 2020, doi: 10.1109/ACCESS.2020.3039831.

- [20] G. Chitrakala, N. Stalin, and V. Mohan, "A Segmented Ladder-Structured Multilevel Inverter for Switch Count Remission and Dual-Mode Savvy," *Journal of Circuits, Systems and Computers*, vol. 27, no. 14, p. 1850223, Dec. 2018, doi: 10.1142/S0218126618502237.

- [21] K. K. Gupta and S. Jain, "A novel multilevel inverter based on switched dc sources," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 7, pp. 3269–3278, 2014, doi: 10.1109/TIE.2013.2282606.

- [22] M. Toupchi Khosroshahi, "Crisscross cascade multilevel inverter with reduction in number of components," *IET Power Electronics*, vol. 7, no. 12, pp. 2914–2924, 2014, doi: 10.1049/iet-pel.2013.0541.

- [23] A. Mokhberdoran and A. Ajami, "Symmetric and asymmetric design and implementation of new cascaded multilevel inverter topology," *IEEE Transactions on Power Electronics*, vol. 29, no. 12, pp. 6712–6724, 2014, doi: 10.1109/TPEL.2014.2302873.

- [24] E. Babaei, S. Laali, and S. Alilu, "Cascaded multilevel inverter with series connection of novel H-bridge basic units," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 12, pp. 6664–6671, 2014, doi: 10.1109/TIE.2014.2316264.

- [25] D. A. Ruiz-Caballero, R. M. Ramos-Astudillo, S. A. Mussa, and M. L. Heldwein, "Symmetrical hybrid multilevel DCAC converters with reduced number of insulated DC supplies," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7, pp. 2307–2314, 2010, doi: 10.1109/TIE.2009.2036636.

# **BIOGRAPHIES OF AUTHORS**

**Ujwala Gajula (b) (S) (s)** obtained her bachelor's degree in Electrical and Electronics Engineering from JNTUH in 2008, followed by a Master's degree in Power Electronics and Electric Drives from JNTUH in 2010. Currently, she is pursuing a part-time Ph.D. at Annamalai University, Chidambaram. She holds memberships in IEEE, IEI, and ISTE. Her primary research interests encompass Power Quality and Renewable Energy Sources. She can be contacted at email: gjujwala@gmail.com.

Kalpanadevi Manivannan D K S Serves as an Assistant Professor at Annamalai University, Chidambaram, Tamil Nadu. She attained her B.E in Electrical & Electronics Engineering from Annamalai University in 2001. In November 2002, she successfully acquired her M.E degree in Power System from the same institution. Furthermore, her academic journey led her to earn a Ph.D. in Electrical Engineering from Annamalai University in 2016. Her research pursuits revolve around several domains including Power System State Estimation, Power Quality analysis, Renewable Energy Sources, and Embedded Systems. She can be contacted at email: sharikka09@yahoo.com.

**N. Malla Reddy b S s** holds the position of Professor and Dean Admissions and Hostel at G. Narayanamma Institute of Technology and Science (for women) located in Shaikpet, Hyderabad. He accomplished his B. Tech degree from SV University, Tirupati in 1998. His educational journey continued with an M. Tech degree from JNTU-Hyderabad in 2005 and Ph.D., specializing in Power system operation and control, from JNTU-Hyderabad in 2015. With more than 21 years of teaching experience, he has garnered extensive expertise. His contributions extend beyond teaching, as he has authored technical papers featured in both national and international conference proceedings/journals. An active member of IEEE and ISTE, he was honored with the Best Teacher Award for the year 2008 at GNITS. His diverse areas of expertise encompass Power Electronics, Power systems, AC and DC Drives, Power Quality, Renewable Energy Sources, and Electric Vehicles. He can be contacted at email: nomula.nomula@gmail.com.