Vol. 15, No. 4, December 2024, pp. 2243~2252

ISSN: 2088-8694, DOI: 10.11591/ijpeds.v15.i4.pp2243-2252

# Performance analysis of fifteen level reduced device count asymmetrical multilevel inverter

Murugesan Manivel<sup>1</sup>, Lakshmanan Palani<sup>2</sup>, Sivaranjani Subramani<sup>3</sup>, Bharani Prakash Thiagarajan<sup>4</sup>, Divya Kannusamy<sup>1</sup>, Jebakumar Immanuel Devasahayam<sup>5</sup>, V. J. Vijayalakshmi<sup>6</sup>

Department of Electrical and Electronics Engineering, Karpagam Institute of Technology, Coimbatore, Tamil Nadu, India

Department of Electrical and Electronics Engineering, Rajagiri School of Engineering & Technology, Kakkanad, India

Department of Electrical and Electronics Engineering, Sri Krishna College of Engineering and Technology, Coimbatore, India

Department of Electrical and Electronics Engineering, Sri Krishna College of Technology, Coimbatore, India

Department of Artificial Intelligence and Data Science, Karpagam Institute of Technology, Tamil Nadu, India

Department of Electrical and Electronics Engineering, Karpagam Academy of Higher Education, Coimbatore, India

### **Article Info**

#### Article history:

Received Dec 20, 2023 Revised May 27, 2024 Accepted Jun 2, 2024

### Keywords:

Alternating current

Direct current

Multilevel inverter

Nearest level control

Total harmonic distortion

### **ABSTRACT**

In this article, a fifteen-level reduced device count asymmetrical multilevel inverter is introduced for electric vehicle applications. This novel multilevel inverter topology minimizes the power switches required. Control of the proposed inverter is accomplished via the nearest-level control method. In a typical multilevel inverter, ten to twelve switches are used to create the fifteen levels. A high number of switches are used in traditional multilevel inverters, which increases the distortion from all harmonics, switching losses, cost, and cost per switch. Only nine switches are needed for the suggested architecture. It significantly minimizes the total harmonic distortion by 5% and lowers the switching losses, low-order harmonics, and complexity. The efficiency of the suggested multilevel inverter (MLI) is 98.35%.

This is an open access article under the <u>CC BY-SA</u> license.

2243

## Corresponding Author:

Murugesan Manivel

Department of Electrical and Electronics Engineering, Karpagam Institute of Technology

Coimbatore 641105, India

Email: murugesan.kec@mail.com

### 1. INTRODUCTION

Multilevel inverters have been a major technological advancement during the past decades and offer the output current and voltage waveforms at three or more levels. It synthesizes a desired alternating current (AC) output voltage waveform from a single direct current (DC) source or several DC voltage sources which may be symmetrical or asymmetrical. The multilevel inverter (MLI) uses a variety of sources, including capacitors, solar cells, and batteries. The advantages of the MLI are reduced switching loss, improved electromagnetic compatibility, higher voltage capacity, and lower harmonic [1]-[4]. The conventional multilevel inverter topologies; the most often used being the cascading H bridge, flying capacitor (FC), and diode-clamped (DC) structures [5], [6]. The majority of MLI's are hybrid structures, which are combinations of two or more fundamental multilevel structures, however alternative MLI frameworks have also been suggested [7], [8].

The diode clamped MLI construction still has a significant limitation that limits its usage in high power applications. The series H-bridge design, from which numerous variations have been derived, is the first configuration to be introduced. The most significant drawback of this arrangement is the increased need for separate voltage sources to feed every cell [9]-[11]. A MLI inverter consists of eleven switches, three capacitors, three diodes, one source, and seven levels of switched capacitors. This circuit can sustain reactive power as the capacitors in this arrangement are self-balancing. However, additional switches, diodes, and capacitors mean a

2244 □ ISSN: 2088-8694

more complicated circuit overall [12]. A contemporary MLI structure that uses very few gate driver circuits and switching components has been presented. It is configured to operate in both symmetrical and asymmetrical configurations for single- and three-phase options [13]. A nine-level MLI has been presented with a reduced maximum standing voltage across the power switches. It contains one DC source, two capacitors, and eleven power semiconductor switching devices [14]. One DC supply, twenty switches, and four capacitors have been used to create a 17-level inverter. The capacitor balancing problem is easily solved by using a parallel and series strategy [15]. Ten power switches, one power diode, and two capacitors are tested in a unique nine-level of switched-capacitor two-output multilevel inverter (SCMLI) [16]. One DC source, ten transistors, four capacitors, and two diodes are needed to generate seventeen different levels [17].

In the recently developed topologies consist of more devices to develop more levels and most of the recent topologies contain capacitors. Voltage balancing problems arise when the capacitors are used to reduce DC sources and raise levels to smooth the output waveform without the need for a filter. The difficulty of sharing voltage among devices connected in series becomes evident as the output levels rise. As the number of levels and components rises, the circuit gets more intricate and costly. To address the aforementioned problems, a circuit configuration with fewer devices and no DC bus capacitors is probably the best option.

In this paper, section 2 deals with the structure of traditional MLIs, describes the operation of the proposed MLI, outlines the calculation of losses and efficiency, and describes the nearest level control technique used to control the operation of the proposed MLI, sections 3 illustrate the results and discussions of proposed MLI and section 4 concludes the proposed work. The recommended MLI structure produces fifteen levels with only nine power switches. Furthermore, for generating every level at the output voltage, a method for determining the necessary DC voltage source is suggested. The switching pulses to the implied MLI in this structure are created using the nearest-level control approach. It significantly reduces the overall harmonic distortion by fifteen levels. It reduces prices, weight, and complexity, and it produces a good quality output voltage with less total harmonic distortion (THD) which is suitable for electric vehicles.

#### 2. METHOD

In this section,, the operations of traditional and proposed MLIs are explained along with their various operating modes. The calculations of switching losses, conduction losses, and efficiency of the recommended MLI were also elaborated. The nearest level control techniques are explained for the suggested 15-level MLIs.

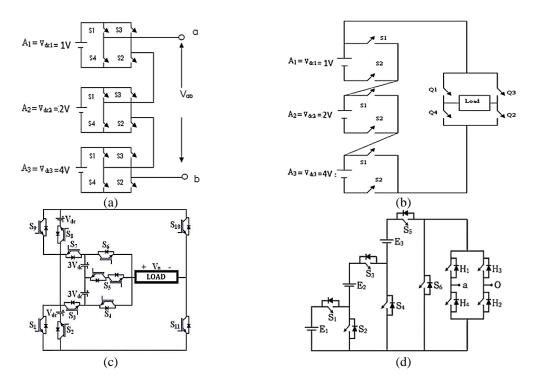

### 2.1. Conventional multilevel inverters

The structure of the conventional MLI is shown in Figure 1(a). Each cell needs separate asymmetrical voltage sources  $(A_1, A_2, A_3)$  linked in series to produce more levels. This configuration involves twelve switches and produces a fifteen-level output voltage. In this structure, three H-bridges are involved. The second topology shown in Figure 1(b) needs ten switches to create the same 15 level output, and in this structure, there are 3 cells, each cell with one DC source and two power switching devices, this give a multilevel DC output. To produce AC waveform in the output before connecting to the load via a H-bridge circuit [18]-[20].

Figure 1(c) is the reduced switch count MLI for producing a fifteen-level output voltage or current waveform. This structure involves twelve power devices and four DC sources [21]. Figure 1(d) shows the reduced switch count MLI with ten switches and three asymmetrical DC sources [22].

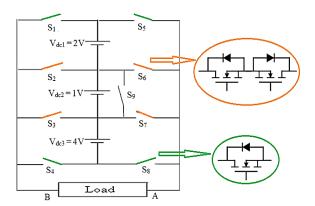

## 2.2. Proposed multilevel inverter

The organization of the recommended MLI is in Figure 2. Three voltage sources are  $(V_{dc1}, V_{dc2}, V_{dc3})$  connected to nine devices  $(S_1, S_4, S_5, S_8)$  are unidirectional switches and  $S_2, S_3, S_6, S_7, S_9$  are bi-directional switches). Four are on one side of the source and the remaining five are in the right side of the three series of connected sources. Figure 3 depicts the operating modes of implied MLI for producing both positive and negative half cycles.

## 2.2.1. Modes of operation during a positive half-cycle

Switches  $S_4$  and  $S_8$  conduct, and it produce zero output voltage. Switches  $S_2$  and  $S_6$  conduct and produces  $1V_{dc}=30$  V, it supplies to the load. Switches  $S_2$  and  $S_5$  conduct and produce  $2V_{dc}=60$  V. Switches  $S_3$  and  $S_5$  conduct and produce  $1V_{dc}+2V_{dc}=3V_{dc}=90$  V. Switches  $S_4$  and  $S_7$  conduct and produce  $4V_{dc}=120$  V, which it supplies to the load. Switches  $S_4$  and  $S_6$  conduct and produce  $1V_{dc}+4V_{dc}=5V_{dc}=150$  V. Switches  $S_4$ ,  $S_5$ , and  $S_9$  conduct and the output voltage is  $2V_{dc}+4V_{dc}=6V_{dc}=180$  V. Switches  $S_4$  and  $S_5$  conduct, and the output voltage across the load is  $1V_{dc}+2V_{dc}+4V_{dc}=7V_{dc}=210$  V. The same steps will be repeated from 210 V to zero.

## 2.2.2. Modes of operation during a negative half-cycle

Switches  $S_4$  and  $S_8$  conduct, and it produces zero output voltage. Switches  $S_2$  and  $S_7$  conduct and produce 1  $V_{dc}$ =-30 V, across the load. Switches  $S_1$  and  $S_6$  conduct and produce 2  $V_{dc}$ =-60 V. Switches  $S_1$  and

$S_7$  conduct and produce 1  $V_{dc}$ +2  $V_{dc}$ =-3  $V_{dc}$ =-90 V. Switches  $S_3$  and  $S_8$  conduct and produce 4  $V_{dc}$ =-120 V, which supplies to the load. Switches  $S_2$  and  $S_8$  conduct and produce 1  $V_{dc}$ +4  $V_{dc}$ =-5  $V_{dc}$ =-150 V. Switches  $S_1$ ,  $S_8$ , and  $S_9$  conduct and the output voltage is 2  $V_{dc}$ +4  $V_{dc}$ =-6  $V_{dc}$ =-180 V. Switches  $S_1$  and  $S_8$  conduct, and the output voltage across the load is 1  $V_{dc}$ +2  $V_{dc}$ +4  $V_{dc}$ =-7  $V_{dc}$ =-210 V. The same steps will be repeated from 210 V to zero.

The main advantages of this structure are that it has 15 levels with nine switches and three asymmetrical DC sources. The proposed MLI produces fifteen levels in the output voltage or current. The structure of the stated system is also compact and produces a lower value of THD. Electrical stresses across each switch are also less and easily controllable and expandable further to produce more levels.

Figure 1. Conventional MLIs: (a) cascaded hybrid H-bridge [18], [19], (b) new cascaded hybrid [20], (c) MLI with twelve switches [21], and (d) MLI with ten switches [22]

Figure 2. Proposed multilevel inverter

## 2.3. Estimation of loss and efficiency

This section describes the theoretical calculation of loss used to determine efficiency of recommended inverter. The most significant losses are conduction and switching losses, and its calculation is based on the assumption that load is totally resistive and that voltage available at output is staircase waveform. Conduction loss happens when MOSFET power switches are actuated and conducts electricity in a multilevel inverter. In the proposed inverter design, losses are computed individually to determine total loss during conduction. In this case, loss due to switch conduction period during the basic cycle quarter is calculated, as in (1).

$$P_{CON} = \frac{4}{\pi} \int_0^{\frac{\pi}{2}} I_R^2(t) R_{ON} T dt$$

(1)

The MOSFET's on-state resistance and load current are denoted as  $R_{on}T$  and  $I_{R}(t)$ , respectively. By employing nine power switches, the proposed system provides 15 levels voltage, and the current in the load side is sinusoidal. As a result, the load current is expressed as (2).

$$I_R = I_P sinwt (2)$$

Using (1) and (2), the average loss of single-phase system during conduction is derived as (3).

$$P_{CON} = \frac{4}{\pi} \int_0^{\frac{\pi}{2}} I_{P,}^2 \sin^2 w t R_{ON,} T dt$$

(3)

During the changeover from ON to OFF or vice versa, the overlapping of voltage and current produces switching loss in MOSFET power switches. The energy loss of MOSFET power switches is computed as follows throughout them on and off periods, as in (4).

$$E_{ON} = \frac{V_{ON} \times I}{6} T_{ON} \tag{4}$$

Figure 3. Operation of proposed multilevel inverter

Where  $V_{ON}$ , I,  $T_{ON}$  are the MOSFET on-state voltage, the MOSFET current after switching on and turn on time respectively, as in (5).

$$E_{OFF} = \frac{V_{OFF} \times I}{6} T_{OFF} \tag{5}$$

$V_{OFF}$ ,  $I_{OFF}$ , and  $T_{OFF}$  are the MOSFET off-state voltage, current passing through the MOSFET before it turns off, and turn-off time, respectively. The typical switching power loss in the projected configuration is find individually for each power switch by using (4) and (5), and the switching loss is determined as (6).

$$P_{SW} = 2 \times f \times (E_{ON} + E_{OFF}) = \frac{1}{3} \times f \times I \times (V_{ON} T_{ON} + V_{OFF} T_{OFF})$$

(6)

The efficiency and total power loss of projected inverter are determined by using (7) and (8).

$$P_{LOSS,TOTAL} = P_{CON} + P_{SW} \tag{7}$$

The efficiency has been calculated using (8).

$$Efficiency = \frac{P_{OUT}}{P_{OUT} + P_{LOSST}} \times 100\%$$

(8)

From the calculations, the conduction losses of MLI is 12.11 W, switching losses of the MLI is 0.39, input power of the MLI is 759.2 W, output power of the MLI is 746.7 W and the efficiency of the MLI is 98.35% for the resistive load of  $100 \Omega$ .

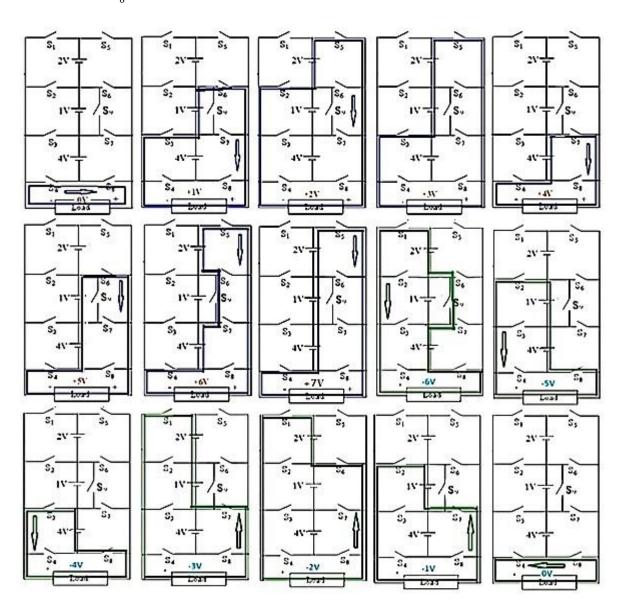

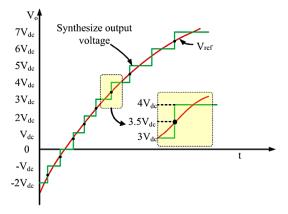

#### 2.4. Nearest level control technique

It is possible to regulate multilevel inverters using both low-frequency and high-frequency switching techniques. A fundamental frequency switching process is employed to control the recommended topology [23]. For basic frequency switching, one can employ the selective harmonic elimination (SHE) or space vector modulation (SVM) schemes. The less appealing aspect of SVM is its control complexity. In terms of the SHE strategy, solving the equations to exactly predict the switching angles would get more difficult as the levels grow [24]. The closest level modulation approach is employed in this research [25], [26]. Figure 4 illustrates the control approach. To achieve each switching state in this manner, the fundamental frequency of the reference sine wave is compared with constants. It is necessary to compare "n" constants with the sine wave at six per unit. if the voltage waveform has "n" levels in the positive half cycle. The closest level constant must have a value between 0 and 1. Next, in order to obtain the constant that will be compared with the reference to create the subsequent level, the same constant will be added. The MOSFETs are then activated in accordance with the switching function using the pulses produced by comparing the same constants with the reference. For instance, the selected nearest level constant must be added to zero in order to create the pulses required for the switches conducting at level 1. Many researchers have concluded after study that the optimal nearest level constant will be 0.4 for low THD and lower order harmonics. One may estimate the switching for each level using (9). The nearest level constant is subtracted from 1 in the calculation to get the result of 0.6.

$$M_a = \frac{V_{ref}}{V_o} \tag{9}$$

Figure 4. Nearest level control modulation technique

2248 □ ISSN: 2088-8694

### 3. RESULTS AND DISCUSSION

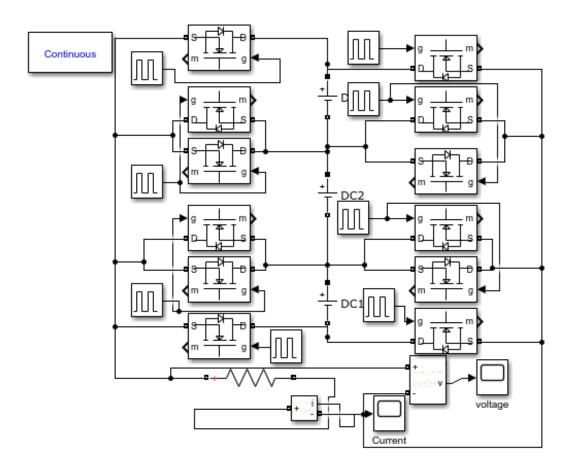

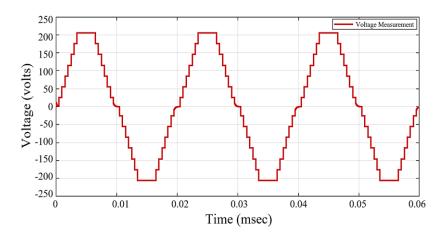

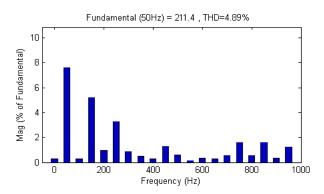

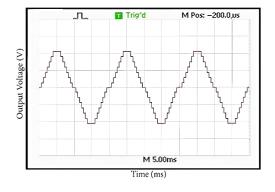

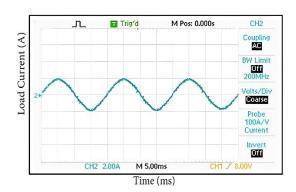

The effectiveness of the recommended MLI for R-load is verified through MATLAB simulation. The Simulink model of the suggested MLI is shown in Figure 5. Three separate DC voltage sources  $30\,\mathrm{V}$ ,  $60\,\mathrm{V}$ , and  $120\,\mathrm{V}$  are utilized in this configuration. The 15-level output voltage waveform is achieved by using the nearest-level control method. The rms value of 15 level output voltage is  $210\,\mathrm{V}$  for  $10\,\mathrm{kW}$  which is shown in Figure 6. It indicates that the output voltage waveform is almost sinusoidal. Figure 7 shows the output voltage and current waveforms for an RL load of  $10\,\mathrm{kW}$  and  $750\,\mathrm{VAR}$ . It indicates that the output current waveform is almost sinusoidal and has a magnitude of  $50\,\mathrm{A}$ . Figure 8 shows THD, its value is 4.89%, and THD is also within the limit of the IEEE standard of 5%.

Figure 5. Simulation diagram of proposed 15 level MLI

Figure 6. Output voltage waveform for 15-level

Figure 7. Output voltage and current waveform for RL load

Time (msec)

Figure 8. FFT analysis for 15-level MLI

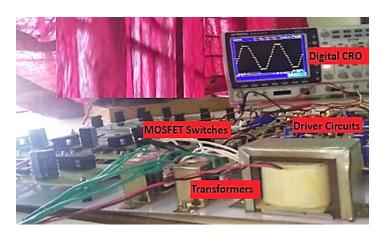

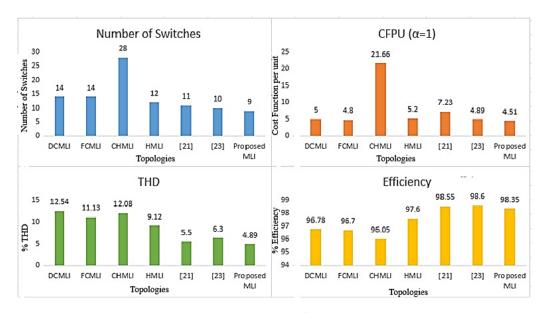

Simulation results are verified through the hardware setup as shown in Figure 9 which consists of nine MOSFETs. There are IRF840 MOSFETs used in the hardware layout. The Arduino microcontroller generates the gate signal for inverter switches. There are three asymmetric DC sources (30 V, 60 V, and 120 V) positioned on the input side of the 15-level inverter. The suggested inverter output powers a resistive load (30 K-0.5 kw). Figure 10 shows the hardware output voltage for resistive load and Figure 11 illustrates the current waveform for the same load. The experimental THD is 4.94 % which is under the THD standard of the IEEE (5%). There are substantially fewer switches employed and a lower overall harmonic distortion when compared to the other four typical inverters shown in Table 1. Figure 12 depicts the comparison of various traditional MLIs. From these comparisons, the proposed MLI is better in terms of device utilization, gate driver circuits needed, total standing voltage per unit, cost function per level, THD, and efficiency.

Figure 9. Experiment setup

2250 ISSN: 2088-8694

| Table 1. Comparison of traditional and proposed multilevel inverters |       |    |          |                  |         |           |           |            |            |                     |       |   |

|----------------------------------------------------------------------|-------|----|----------|------------------|---------|-----------|-----------|------------|------------|---------------------|-------|---|

| ies                                                                  | Level | Ns | $N_{gd}$ | $N_{\mathrm{D}}$ | $N_{C}$ | $N_{DCS}$ | MBV       | TSV        | $TSV_{PU}$ | $CF_{PU(\alpha=1)}$ | THD   | E |

|                                                                      | 15    | 14 | 14       | 12               | 7       | 1         | $1V_{dc}$ | $28V_{dc}$ | 28         | 5.00                | 12.54 |   |

| ruble 1. Comparison of traditional and proposed matrice of inverters |              |       |         |          |       |             |           |           |            |            |                     |       |            |

|----------------------------------------------------------------------|--------------|-------|---------|----------|-------|-------------|-----------|-----------|------------|------------|---------------------|-------|------------|

| S.No.                                                                | Topologies   | Level | $N_{S}$ | $N_{gd}$ | $N_D$ | $N_{\rm C}$ | $N_{DCS}$ | MBV       | TSV        | $TSV_{PU}$ | $CF_{PU(\alpha=1)}$ | THD   | Efficiency |

| 1                                                                    | DCMLI        | 15    | 14      | 14       | 12    | 7           | 1         | $1V_{dc}$ | $28V_{dc}$ | 28         | 5.00                | 12.54 | 96.78      |

| 2                                                                    | FCMLI        | 15    | 14      | 14       | 0     | 16          | 1         | $1V_{dc}$ | $28V_{dc}$ | 28         | 4.80                | 11.13 | 96.70      |

| 3                                                                    | CHMLI        | 15    | 28      | 14       | 0     | 0           | 1         | $7V_{dc}$ | $28V_{dc}$ | 4          | 21.66               | 12.08 | 96.05      |

| 4                                                                    | HMLI         | 15    | 12      | 10       | 0     | 0           | 3         | $7V_{dc}$ | $52V_{dc}$ | 7.43       | 5.20                | 9.12  | 97.60      |

| 6                                                                    | [21]         | 15    | 11      | 11       | 0     | 0           | 4         | $7V_{dc}$ | $36V_{dc}$ | 5.14       | 7.23                | 5.50  | 98.55      |

| 7                                                                    | [23]         | 15    | 10      | 7        | 0     | 0           | 3         | $7V_{dc}$ | $50V_{dc}$ | 7.43       | 4.89                | 6.3   | 98.60      |

| 8                                                                    | Proposed MLI | 15    | 9       | 7        | 0     | 0           | 3         | $7V_{dc}$ | $46V_{dc}$ | 6.57       | 4.51                | 4.89  | 98.35      |

Figure 10. Hardware output voltage waveform

Figure 11. Hardware output current waveform

Figure 12. Comparison of various MLIs

# **CONCLUSION**

This article has shown how the suggested MLI configuration works with nine switches. This MLI structure and its basic functions have been discussed. A method for calculating the switches required in relation to the necessary output level was also covered. In the traditional system, the number of switches needed rose along with the levels. Because there are a lot of power semiconductor switches involved, there is an increase in harmonics, switch losses, cost, and distortion of all harmonics. For 15 levels, the suggested configuration drastically lowers the power consumption of semiconductor switches, efficiency is 98.35%. The MLI's overall complexity is less, and cost function per level is 4.89 and THD is 4.51% which comes under the standard of IEEE 5%. Hence, this proposed structure is most suitable for EV applications.

# REFERENCES

A. Poorfakhraei, M. Narimani, and A. Emadi, "A review of multilevel inverter topologies in electric vehicles: current status and future trends," IEEE Open Journal of Power Electronics, vol. 2, pp. 155-170, 2021, doi: 10.1109/OJPEL.2021.3063550.

П

- [2] F. Z. Peng, J. W. McKeever, and D. J. Adams, "A power line conditioner using cascade multilevel inverters for distribution systems," *IEEE Transactions on Industry Applications*, vol. 34, no. 6, pp. 1293–1298, 1998, doi: 10.1109/28.739012.

- [3] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel inverters for electric vehicle applications," in *Power Electronics in Transportation (Cat. No.98TH8349)*, IEEE, 1998, pp. 79–84. doi: 10.1109/PET.1998.731062.

- [4] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," *IEEE Transactions on Industry Applications*, vol. 35, no. 1, pp. 36–44, 1999, doi: 10.1109/28.740843.

- [5] K. A. Corzine, M. W. Wielebski, F. Z. Peng, and J. Wang, "Control of cascaded multilevel inverters," *IEEE Transactions on Power Electronics*, vol. 19, no. 3, pp. 732–738, May 2004, doi: 10.1109/TPEL.2004.826495.

- [6] M. Fracchia, T. Ghiara, M. Marchesoni, and M. Mazzucchelli, "Optimized modulation techniques for the generalized N-level converter," in PESC '92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, IEEE, 1992, pp. 1205–1213. doi: 10.1109/PESC.1992.254737.

- [7] K. A. Corzine and J. R. Baker, "Reduced-parts-count multilevel rectifiers," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 766–774, Aug. 2002, doi: 10.1109/TIE.2002.801077.

- [8] D. Chittathuru, S. Padmanaban, and R. Prasad, "Design and implementation of asymmetric cascaded multilevel inverter with optimal components," *Electric Power Components and Systems*, vol. 49, no. 4–5, pp. 361–374, Mar. 2021, doi: 10.1080/15325008.2021.1970290.

- [9] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 724–738, Aug. 2002, doi: 10.1109/TIE.2002.801052.

- [10] P. R. Bana, K. P. Panda, S. Padmanaban, and G. Panda, "Extendable switched-capacitor multilevel inverter with reduced number of components and self-balancing capacitors," *IEEE Transactions on Industry Applications*, vol. 57, no. 3, pp. 3154–3163, May 2021, doi: 10.1109/TIA.2020.3018422.

- [11] N. P. Gopinath, K. Vijayakumar, J. S. Mohd Ali, K. Raghupathi, and S. Selvam, "A triple boost seven-level common ground transformerless inverter topology for grid-connected photovoltaic applications," *Energies*, vol. 16, no. 8, p. 3428, Apr. 2023, doi: 10.3390/en16083428.

- [12] S. Sivamani and V. Mohan, "A three-phase reduced switch count multilevel inverter topology," *International Transactions on Electrical Energy Systems*, vol. 2022, no. 1, pp. 1–16, Dec. 2022, doi: 10.1155/2022/6193731.

- [13] A. Maurya and A. Mishra, "A single source based multilevel boost inverter with reduced peak standing voltage for renewable energy and EV applications," *Renewable Energy Focus*, vol. 42, pp. 33–47, Sep. 2022, doi: 10.1016/j.ref.2022.05.002.

- [14] D. K. Patel, V. P. Pal, K. Baitha, and D. Kumar, "A Novel 17-level switched-capacitor multilevel inverter with reduced device count," in 2022 2nd International Conference on Emerging Frontiers in Electrical and Electronic Technologies (ICEFEET), IEEE, Jun. 2022, pp. 1–6. doi: 10.1109/ICEFEET51821.2022.9847689.

- [15] P. Prem et al., "A novel cross-connected multilevel inverter topology for higher number of voltage levels with reduced switch count," *International Transactions on Electrical Energy Systems*, vol. 30, no. 6, p. e12381, Jun. 2020, doi: 10.1002/2050-7038.12381.

- [16] R. Anand and R. K. Mandal, "An efficient and high gain switched-capacitor based multi-level inverter," Engineering Research Express, vol. 4, no. 3, p. 035019, Sep. 2022, doi: 10.1088/2631-8695/ac84c6.

- [17] R. Sun, X. Wang, and Y. Ye, "Seventeen-level inverter based on switched-capacitor and flying-capacitor-fed T-type unit," *IEEE Access*, vol. 10, pp. 33561–33570, 2022, doi: 10.1109/ACCESS.2022.3161949.

- [18] H. S. Patel and R. G. Hoft, "Generalized techniques of harmonic elimination and voltage control in thyristor inverters: Part I--harmonic elimination," *IEEE Transactions on Industry Applications*, vol. IA-9, no. 3, pp. 310–317, May 1973, doi: 10.1109/TIA.1973.349908.

- [19] R. Murugesan, M., R. S. Pari, and S. Sivaranjani, "Different types of multilevel inverter topologies-A technical review," *International Journal of Advanced Engineering Technology*, vol. 7, no. 1, pp. 149–155, 2016.

- [20] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," *IEEE Transactions on Industry Applications*, vol. 37, no. 2, pp. 611–618, 2001, doi: 10.1109/28.913728.

- [21] M. Fahad, M. D. Siddique, A. Iqbal, A. Sarwar, and S. Mekhilef, "Implementation and analysis of a 15-level inverter topology with reduced switch count," *IEEE Access*, vol. 9, pp. 40623–40634, 2021, doi: 10.1109/ACCESS.2021.3064982.

- [22] V. N. V. Kumar and G. T. Manohar, "A comprehensive survey on reduced switch count multilevel inverter topologies and modulation techniques," *Journal of Electrical Systems and Information Technology*, vol. 10, no. 1, Jan. 2023, doi: 10.1186/s43067-023-00071-8.

- [23] M. Rawa et al., "A new multilevel inverter topology with reduced DC sources," Energies, vol. 14, no. 15, p. 4709, Aug. 2021, doi: 10.3390/en14154709.

- [24] M. D. Siddique, S. Mekhilef, S. Padmanaban, M. A. Memon, and C. Kumar, "Single-phase step-up switched-capacitor-based multilevel inverter topology with SHEPWM," *IEEE Transactions on Industry Applications*, vol. 57, no. 3, pp. 3107–3119, May 2021, doi: 10.1109/TIA.2020.3002182.

- [25] S. K and M. Das B, "A low switching frequency based 17 level inverter with nearest level control," in 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), IEEE, Dec. 2020, pp. 1–5. doi: 10.1109/PEDES49360.2020.9379461.

- [26] M. Manivel and L. Kaliappan, "Analysis and implementation of switched capacitor-based multi-level inverter for electric vehicles applications," *Elektronika ir Elektrotechnika*, vol. 29, no. 1, pp. 21–32, Feb. 2023, doi: 10.5755/j02.eie.33053.

### **BIOGRAPHIES OF AUTHORS**

Murugesan Manivel is an Assistant Professor in Electrical and Electronics Engineering Department at Karpagam Institute of Technology, Coimbatore, Tamil Nadu, India. He has completed his Ph.D. from Anna University, Chennai, India. He received his B.E. and M.E. degrees in Electrical and Electronics Engineering from Kongu Engineering College, Tamil Nadu, India and K.S. Rangasamy College of Technology, Tamil Nadu, India, in 2009 and 2011, respectively. He is having 13 years of teaching experience. He is a life member of Indian Society for Technical Education (ISTE). He has published more than 25 papers in various international journals and conferences. His research interests include the field of power electronics, motor drives, and renewable energy systems. He can be contacted at email: murugesan.kec@gmail.com.

Sivaranjani Subramani si currently working as an associate professor. She received doctoral degree from Anna University Chennai, during the year 2020. She completed M.E. in power electronics and drives during the year 2006 and B.E in Electrical and Electronics Engineering during the year 2001 in Anna University, Chennai. She is having 18 years of teaching experience. She published her research work in 25 SCI/Scopus/UGC journals and the publication includes 10 patents and 6 books/book chapters. Her current research interests include simulation and digital control techniques of AC drives, inverters topologies, and harmonic suppression. She can be contacted at email: shivaranjani\_s@rediffmail.com.

Bharani Prakash Thiagarajan (D) (S) received his bachelor's degree in Electrical and Electronics Engineering in 2008 from Anna University. He also receives a master of technology (M.Tech.) from the Same University. He is a life member of Indian Society of Technical Education (ISTE) and a full—time assistant professor in Sri Krishna College of Technology. His research interest are power electronics, semiconductor devices, renewable energy sources, high-voltage engineering, digital circuits, and electrical machines. He can be contacted at email: bharani.ffb@gmail.com.

V. J. Vijayalakshmi signification, Coimbatore, Tamilnadu, India. She received her Ph.D. degree in Faculty of Electrical Engineering, M.E. degree in Power Systems Engineering and B.E. degree in Electrical and Electronics Engineering. She has more than 15 years of experience in Teaching and Research. Her research areas include smart grid, electricity deregulation, and outcome based education. She is the member of IEEE, ISTE. She is also a certified Energy Manager by the Bureau of Energy Efficiency Government of India. She can be contacted at email: vijik810@gmail.com.