ISSN: 2088-8694, DOI: 10.11591/ijpeds.v15.i4.pp2287-2295

# Single-phase five level modified neutral point clamped grid connected inverter topology with front-end chopper control of DC-link capacitor voltages

# Y. Sravan Kumar<sup>1</sup>, T. Murali Krishna<sup>2</sup>, Yesuratnam Guduri<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, University College of Engineering, Osmania University, Hyderabad, India <sup>2</sup>Department of Electrical and Electronics Engineering, Chaitanya Bharathi Institute of Technology, Hyderabad, India

# **Article Info**

#### Article history:

Received Feb 2, 2024 Revised Jun 8, 2024 Accepted Jun 13, 2024

#### Keywords:

Active power control Grid-connected inverter Low harmonic distortion Pulse width modulation Reactive power control

# **ABSTRACT**

Conventionally, only the standalone operation of a single-phase fault tolerantbased 5-level neutral point clamped (SPFT-5L-NPC) inverter with two stiff DC sources has been explained with consideration of phase disposition pulse width modulation (PD-PWM) technique. In this topology, the bidirectional switch arrangement consists of four diodes and one IGBT switch. This arrangement inherently increases conduction losses of topology. Generally, any NPC inverter topology suffers from a DC-link capacitor voltage (DCL-CV) balancing issue. In the conventional contribution of work, authors have not discussed the front-end voltage balancing issue. This study describes the extension work of a single-phase grid connection with a modified 5L-NPC (M5L-NPC) inverter topology, taking into account the aforementioned concerns. In this topology, the simple front-end chopper circuit has been utilized to balance the DCL-CVs and to reduce conduction losses, another arrangement of bidirectional switch has been utilized. In this paper, both standalone and grid connections of M5L-NPC topology have been explained along with control of DCL-CVs. The grid-connected important objectives of active power control (APC), reactive power control (RPC), and injecting sinusoidal current with low harmonic distortion have been discussed thoroughly considering a simple control strategy.

This is an open access article under the **CC BY-SA** license.

2287

## Corresponding Author:

Y. Sravan Kumar

Department of Electrical Engineering, University College of Engineering, Osmania University Hyderabad, Telangana, India

Email: y.sravan16@gmail.com

# 1. INTRODUCTION

In multilevel inverters (MLIs), the lower dv/dt minimizes electromagnetic interference, while the increased number of components may lower reliability. To obtain higher reliability, the fault tolerance of multilevel structures serves as a compensating factor [1]. As the number of levels rises, the traditional NPC inverter design results in uneven losses in the semiconductor components increases cost, and decreases the reliability [2]. The traditional flying capacitor (FC) based MLIs need a large number of FCs, and additional voltage sensors are needed to balance these capacitors. Then it leads to lower reliability as going to higher levels [3].

The cascaded H-Bridge (CHB) MLI topologies offer higher modularity and dependability. Nonetheless, a greater quantity of separate DC sources is required [4]. In comparison to the FC and NPC-MLI topologies, the nested neutral point clamped (NNPC) topology features fewer clamping diodes and fewer FCs, but it is less reliable due to uneven voltage distribution on switches [5]. A five-level F-type inverter topology

Journal homepage: http://ijpeds.iaescore.com

2288 □ ISSN: 2088-8694

is suggested in [6], however the meaning of dependability is not clarified. The carrier-overlapped PWM solution is proposed to address the neutral point voltage disparity issue in the traditional 5L-NPC inverter design [7], however, the reliability concept has not been addressed.

The idea of reliability is not described in [8], which discusses only a capacitor voltage balancing with the utilization of redundant states for the traditional 5L-FC-based inverter topology. A hybrid MLI topology is suggested in [9], however, to provide 5L-output voltage, more components are required. A 5L-H-Bridge type NPC inverter topology without fault tolerance concept using an improved PWM approach is described in [10], however, this design also requires a higher component count.

A SPFT-5L-NPC topology with redundant states is described in [11]. However, this just explains the standalone operation and the authors have not described the DCL-CV balance problem also. Several topologies with common DC links have been laid out in the literature [12]. A summary of various fault-tolerant MLI topologies can potentially provided in [13]. The result [14]-[16], various DCL-CV balancing control strategies have been explained but these are complex. Hence, it is necessary to develop a simple control strategy to apply all common DC-link-based inverter topologies to ensure safe operation.

Aside from this, improving the quality of the output voltage for any MLI design also depends on the PWM implementation. Although space vector modulation strategies for NPC-MLI topology have been reviewed in [17], the intricacy of control becomes burdensome as one moves to higher levels. Several kinds of multi-carrier PWM schemes have been discussed in [18]. In these, the PD-PWM gives an excellent harmonic profile but implementation needs more triangular carrier signals. An absolute function unipolar PD-PWM (UPD-PWM) has been reported in [19], [20] to simplify the PD-PWM stage. The triangular carrier count can be cut in half with this UPD-PWM strategy.

The DCL-CV accounts for the complete grid connection while taking H-bridge topology into account [21]. It is balanced through the battery using a bidirectional converter. The sliding mode control approach for a 1-phase grid-connected H-Bridge inverter topology has been documented in [22]. The phase-locked loop (PLL), which has been explained in [23], is generally considered to be crucial when thinking about any grid operation. The grid control approach based on the orthogonal signal generator (OSG) and featuring two proportional-integral (PI) controllers was documented in [24]. A dq-frame control scheme for grid operation has been disclosed in [25]. For grid operation, the linear quadratic controller has been described in [26]. A simple control technique must be needed because all of the existing grid-connected control strategies are complicated.

In this paper, the DCL-CV balancing and single-phase grid connection with various dynamic investigations have been discussed by taking into account the modified SPFT-5L-NPC topology. The DCL-CVs are balanced by employing a straightforward chopper-based control method, which works with all popular DC-link MLI topologies. A straightforward current control approach has been used to explain single-phase grid operation, which reduces computation effort. The rest of the paperwork is organized as follows. In section 2, the circuit description of the proposed M5L-NPC grid-connected inverter (GCI) topology and control strategy for balancing DCL-CVs have been discussed. In section 3, the control strategy for grid connected operation (GCO) has been explained. In section 4, the simulation results of both standalone and GCO have been explained. In section 5, the comparative study between conventional and extension work of the proposed topology has been discussed. Finally, conclusions are reported.

# 2. CIRCUIT DESCRIPTION OF PROPOSED M5L-NPC GCI TOPOLOGY AND CONTROL STRATEGY FOR BALANCING DCL-CVS: CHOPPER CIRCUIT

# 2.1. Circuit description of proposed M5L-NPC GCI topology

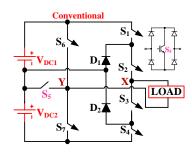

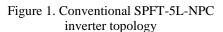

In the literature, only the stand-alone operation of an SPFT-5L-NPC inverter topology has been discussed [11]. The conventional SPFT-5L-NPC inverter topology is depicted in Figure 1. However, this topology needs two DC sources and the conventional bidirectional switch with four diodes increases conduction losses. The front-end voltage balancing problem has not been covered by authors in the traditional contribution of work. To explain the grid connection operation, a M5L-NPC inverter topology has been proposed and it is depicted in Figure 2 which is a modified version of SPFT-5L-NPC topology. It consists of one DC source along with a chopper control circuit and to reduce conduction losses, the conventional bidirectional switch has been replaced with two diodes and two IGBTs which are connected in anti-parallel. The new connected bidirectional switch is operating under a common emitter (CE) configuration thereby only one gate driver circuit is needed.

The front-end chopper circuit consists of two IGBT switches, one resistor, one inductor, and two DC-link capacitors. This independent chopper circuit easily provides an equal amount of balancing voltages at DC-link capacitors ( $C_1$  and  $C_2$ ) and the respective control action has been explained in this sub-section. At the end, an inductor filter and grid have been connected to the topology.

After balancing the DCL-CVs with chopper control, the switching operation of the inverter topology at each state is important and it is depicted in Table 1. To produce 0  $V_{dc}$ , the switches  $S_2$ - $S_3$ - $S_5$  should be turned ON, and the remaining are in the OFF state. By turning ON the one of redundant states of  $S_1$ - $S_2$ - $S_5$  switches, the inverter generates 0.5  $V_{dc}$  at the output. To produce 1Vdc, the switches  $S_1$ - $S_2$ - $S_7$  should be turned ON, and the remaining are in the OFF state.

By turning ON  $S_2$ - $S_3$ - $S_6$  switches, the inverter generates -0.5  $V_{dc}$  at the output. Similarly, to produce -1  $V_{dc}$ , the switches  $S_3$ - $S_4$ - $S_6$  should be turned ON, and the remaining are in the OFF state. Finally, the topology provides five levels at the output with peak values of  $\pm 1V_{dc}$ . At each stage, only three switches are conducting and else are in OFF mode. The drawback of this topology is, it provides only unity gain.

Figure 2. Proposed M5L-NPC GCI topologyextension of work

| Table 1. Switching operation |                |                                                |  |  |

|------------------------------|----------------|------------------------------------------------|--|--|

| S. No                        | $V_{XY}$       | ON State Switches                              |  |  |

| 1.                           | $0 V_{dc}$     | S <sub>2</sub> -S <sub>3</sub> -S <sub>5</sub> |  |  |

| 2.                           | $0.5 \ V_{dc}$ | $S_1-S_2-S_5$                                  |  |  |

| 3.                           | $1 V_{dc}$     | $S_1-S_2-S_7$                                  |  |  |

| 4.                           | $-0.5 V_{dc}$  | $S_2-S_3-S_6$                                  |  |  |

| 5.                           | $-1 V_{dc}$    | $S_3 - S_4 - S_6$                              |  |  |

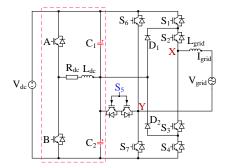

## 2.2. Control strategy for balancing DCL-CVs: Chopper circuit

In Figure 2, the dotted line portion represents the chopper circuit, and the respective proposed control strategy is depicted in Figure 3. In this control strategy, RO indicates the relational operator and PB indicates the product block. Firstly, sense each DCL-CV ( $V_{c1}$  and  $V_{c2}$ ) and compare with the reference half of DC-bus voltage. The obtained outputs have been multiplied and it gives respective switching pulses to A and B switches.

Finally, capacitors' corresponding charging and discharging operation through  $R_{dc}$  and  $L_{dc}$  leads to balancing the capacitor voltages at the desired reference voltage level. The implementation of the chopper control strategy is simple and it is effectively suitable for different types of front-end DC-link-based inverter topologies.

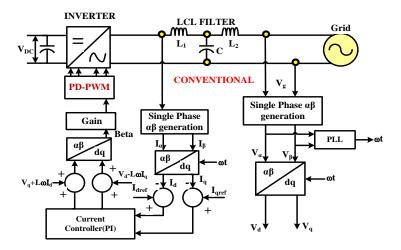

To attain the grid-connected objectives of APC, RPC, and injecting sinusoidal current with low harmonic distortion, a proper simple control strategy should be required to reduce the computational burden on the real-time processor units. Figure 4 represents a conventional dq-frame-based current control strategy for 1-phase grid-connected systems. In this, the implementation requires more transformation blocks, more PI controllers (tedious tuning), and more mathematical operations.

Figure 3. Proposed control strategy for chopper circuit

2290 □ ISSN: 2088-8694

Figure 4. Conventional dq-frame control strategy: grid operation

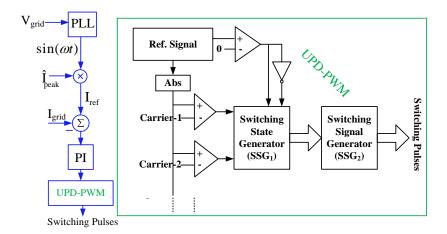

After generating a modulating signal from the control algorithm, at the end stage of implementation, the authors have generally used the conventional PD-PWM technique. In this PWM technique, to generate a five-level output, four triangular carriers are required and the rest of the implementation process also increases. To reduce the complexity of the grid operation control strategy along with the PWM stage, a simple control strategy has been implemented to attain all required objectives and it is applied to the proposed M5L-NPC topology. The proposed grid-connected current control strategy along with the UPD-PWM technique is depicted in Figure 5. The UPD-PWM technique has been adopted from [19], [20]. Its implementation needs only two carrier signals to generate a 5-level output voltage and the rest of the implementation is also simple as compared with the PD-PWM technique.

The operation of the proposed grid-connected current control strategy has been explained in the following steps. Its implementation is simple as compared with the traditional dq-frame control strategy along with the PWM stage.

- a. In GCO, firstly, sense the grid voltage ( $V_{grid}$ ) and grid current ( $I_{grid}$ ).

- b. The  $V_{\text{grid}}$  is fed to a PLL and it provides grid synchronization.

- c. The obtained output is fed to the sinusoidal term.

- d. This can be multiplied with a peak value of the grid current ( $I_{peak}$ ) and it gives the reference value of the injected grid current ( $I_{ref}$ ).

- e. The Iref is compared with Igrid and the error output is fed to the PI controller.

- f. The PI output gives a reference signal for the PWM stage.

- g. To generate the necessary switching pulses, the UPD-PWM has been employed.

- h. Finally, the complete control strategy provides all the objectives of a grid-connected system.

Figure 5. Control strategy for proposed M5L-NPC topology: GCO

П

#### 3. SIMULATION RESULTS: STANDALONE AND GCO-PLECS TOOL

#### 3.1. Standalone operation: R and RL-loads

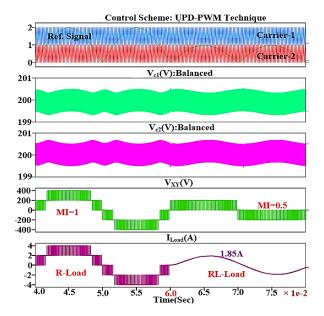

Before going to GCO, the proposed work has been tested in standalone mode with only consideration of the UPD-PWM technique. Here the standalone operation is nothing but resistive and inductive loads only. In standalone operation the value of the switching frequency considered is 5 kHz. By considering UPD-PWM technique the number of triangular carriers can be reduced to half as compared with level shifted PWM technique. Table 2 represents simulation parameters for the standalone mode.

By considering the step change of load (R to RL) and step change of modulation index (MI) =1 to 0.5 at t=0.06 sec, the following simulation results are obtained which are depicted in Figure 6. In this, the first result represents UPD-PWM technique with MI=1 to 0.5. The second and third results show DCL-CVs which are balanced at 200 V with less voltage ripple. The fourth result shows inverter output voltage (IOV:  $V_{XY}$ ) and it gives 5 levels with a peak value of  $\pm 400$  V at MI=1.0 and similarly, it generated 3 levels with a peak value of  $\pm 200$  V at MI=0.5.

The final result represents the corresponding step change of load current waveforms. In the resistive load operation with MI=1.0, the peak value of load current approximately at 4 A has been obtained. Similarly, in the RL-load operation with MI=0.5, the peak value of load current is approximately 1.85 A has been obtained. Even step change of load and step change of MI, the chopper control strategy effectively balances the DCL-CVs at the desired voltage level.

Table 2. Simulation parameters-standalone operation

| S. No | Parameter                | Value        |

|-------|--------------------------|--------------|

| 1.    | Resistor-load            | $100 \Omega$ |

| 2.    | Inductor-load            | 80 mH        |

| 3.    | Switching frequency      | 5 kHz        |

| 4.    | DC-link: V <sub>dc</sub> | 400 V        |

| 5.    | Chopper-C <sub>1</sub>   | 1000 μF      |

| 6.    | Chopper-C <sub>2</sub>   | 1000 μF      |

| 7.    | Chopper-R <sub>dc</sub>  | $0.1 \Omega$ |

| 8.    | Chopper-L <sub>dc</sub>  | 0.01 mH      |

Figure 6. Results for M5L-NPC topology: standalone operation

# 3.2. Grid-connected operation (GCO): results

By using the Figure 5 control strategy, the GCO has been explained in this section. The respective grid-connected simulation parameters are represented in Table 3. Generally, the minimum DC-link voltage in a single-phase grid-connected system can be selected 1.2 times of peak value of  $V_{grid}$ . To explain the GCO of the proposed M5L-NPC topology, there are different transient case studies have been explained in this section.

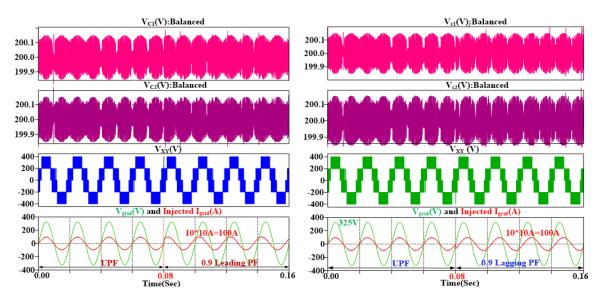

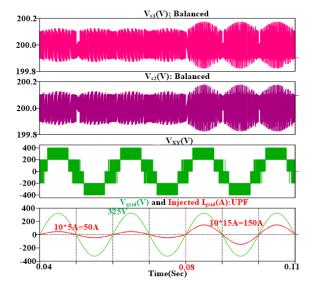

Figure 7 represents simulation results for GCO with a step change of unity power factor (UPF) to 0.9 leading PF at t=0.08 sec. Figure 8 represents simulation results for GCO with a step change of UPF to 0.9 leading PF at t=0.08 sec. In these two cases, the injected  $I_{peak}$ =10 A is considered and for visibility of the  $I_{grid}$

2292 ISSN: 2088-8694

in simulation results, the outer side of the gain value=10 is multiplied by the  $I_{grid}$  component. Figure 9 represents simulation results for GCO under UPF operation with a step change of  $I_{peak}$ =5 A to 15 A.

In all cases with the utilization of the chopper control strategy, both DCL-CVs are balanced at half DC-bus voltage = 200 V. Here, the proposed chopper control strategy is universally suitable to all split DC-link-based inverter topologies. The inverter generated 5-levels with a peak value of  $\pm 400$  V and of course, based on reference  $I_{peak}$ , the levels may vary. In these studies, the UPF and leading/lagging PF indicate injecting active and reactive power into the grid. All transient results with the utilization of a simple proposed current control strategy give better performance according to the reference value of  $I_{grid}$ .

Table 3. Simulation parameters-GCO

| S. No | Parameter                | Value         | S. No | Parameter               | Value        |

|-------|--------------------------|---------------|-------|-------------------------|--------------|

| 1.    | Resistor-filter          | $0.01~\Omega$ | 6.    | Grid frequency          | 50 Hz        |

| 2.    | Inductor-filter          | 3.5 mH        | 7.    | Chopper-C <sub>1</sub>  | 1000 μF      |

| 3.    | Switching frequency      | 10 kHz        | 8.    | Chopper-C <sub>2</sub>  | 1000 μF      |

| 4.    | DC-link: V <sub>dc</sub> | 400 V         | 9.    | Chopper-R <sub>dc</sub> | $0.1 \Omega$ |

| 5.    | V <sub>grid</sub> (Peak) | 325 V         | 10.   | Chopper-L <sub>dc</sub> | 0.01 mH      |

Figure 7. Results for M5L-NPC topology: GCO (UPF to 0.9 leading PF with  $I_{peak}$ =10 A)

Figure 8. Results for M5L-NPC topology: GCO (UPF to 0.9 lagging PF with  $I_{peak}$ =10 A)

Figure 9. Results for M5L-NPC topology: GCO (UPF with step change of Ipeak=5 A to 15 A)

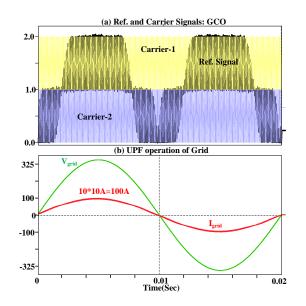

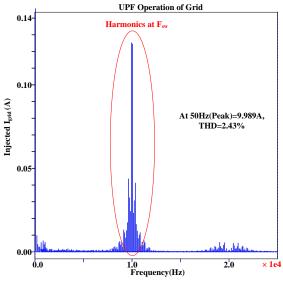

Figure 10 represents the zoomed view of reference and carrier signals in GCO at UPF mode. In this, the black color represents the unipolar reference signal in closed-loop operation. Figure 11 shows the harmonic spectrum of  $I_{grid}$  at UPF operation. In this, the first band of switching frequency harmonics is placed at 10 kHz. It gives the peak value of current=9.989 A at the fundamental frequency and provides total harmonic distortion (THD) = 2.43%. It follows IEEE-1547 standards and provides good power quality on the utility side. Finally, APC, RPC, and low harmonic  $I_{grid}$  distortion objectives have been achieved successfully along with balanced DCL-CVs.

Figure 10. Zoomed view results: GCO (UPF operation with I<sub>peak</sub>=10 A)

Figure 11. Harmonic spectrum of  $I_{grid}$ : GCO (UPF operation with  $I_{peak}$ =10 A)

# 4. COMPARATIVE STUDY

The comparative study between conventional topology and proposed modified topology is represented in Table 4. The conventional SPFT-5L-NPC Topology has 2 DC sources, while the proposed M5L-NPC topology utilizes 1 DC source. The conventional SPFT-5L-NPC operates only as a standalone system, whereas the proposed M5L-NPC supports both standalone and GCOs. The conventional SPFT-5L-NPC employs PD-PWM (N<sub>carriers</sub> = 4), while the proposed M5L-NPC utilizes UPD-PWM (N<sub>carriers</sub> = 2) for generating switching pulses.

The conventional SPFT-5L-NPC features a bidirectional switch with 4-diodes and 1-IGBT, whereas the proposed M5L-NPC uses 2-diodes and 2-IGBTs for bidirectional switching. The chopper control strategy is not explained in the conventional SPFT-5L-NPC, while the proposed M5L-NPC elaborates on its chopper control strategy, suitable for both standalone and GCOs.

Table 4. Comparative study

| S. No | Conventional SPFT-5L-NPC Topology         | Proposed M5L-NPC Topology                              |

|-------|-------------------------------------------|--------------------------------------------------------|

| 1.    | Number of DC sources $= 2$                | Number of DC sources = 1                               |

| 2.    | Operation: Only standalone                | Operation: Both standalone and GCO                     |

| 3.    | PWM: PD-PWM ( $N_{carriers} = 4$ )        | PWM: UPD-PWM ( $N_{carriers} = 2$ )                    |

| 4.    | Bidirectional switch: 4-Diodes and 1-IGBT | Bidirectional switch: 2-Diodes and 2-IGBT              |

| 5.    | Chopper control strategy: Not explained   | Chopper control strategy: Explained.                   |

|       |                                           | It is effectively suitable for both standalone and GCO |

## 5. CONCLUSION

In this paper, the comparative study between conventional and proposed topology has been discussed. This study explains the control of DCL-CVs as well as standalone and grid connections of the proposed M5L-NPC architecture. In both standalone and GCO, the DC-link capacitors are effectively balanced at half of the total DC-bus voltage. Of course, the suggested chopper control approach works with every split DC-link-based inverter topology. The APC, RPC, and injecting sinusoidal current with low harmonic distortion-three grid-connected key objectives have been comprehensively examined while taking a straightforward simple current

2294 ISSN: 2088-8694

control approach into account. The drawback of the proposed M5L-NPC topology is that it provides only unity gain along with the chopper circuit. To improve the gain value along with the balancing of DCL-CVs, a new study is necessary and it can be considered as a future scope of work.

#### REFERENCES

- A. Poorfakhraei, M. Narimani, and A. Emadi, "A review of multilevel inverter topologies in electric vehicles: Current status and future trends," *IEEE Open Journal of Power Electronics*, vol. 2, pp. 155–170, 2021, doi: 10.1109/OJPEL.2021.3063550.

A. Nabae, I. Takahashi, and H. Akagi, "A New Neutral-Point-Clamped PWM Inverter," *IEEE Transactions on Industry*

- Applications, vol. IA-17, no. 5, pp. 518-523, 1981, doi: 10.1109/TIA.1981.4503992.

- T. A. Meynard and H. Foch, "Multi-level conversion: High voltage choppers and voltage-source inverters," PESC Record IEEE Annual Power Electronics Specialists Conference, pp. 397-403, 1992, doi: 10.1109/PESC.1992.254717.

- K. Tammali, S. S. Vangala, S. Vattikonda, K. Palle, A. Bhanuchandar, and K. B. Kumar, "An Asymmetric Source Configuration Single-Phase CHB-MLI Topology with a Generalized Reduced-Carrier Modulation Technique," 10.1109/ICICCSP53532.2022.9862515.

- M. Narimani, B. Wu, Z. Cheng, and N. R. Zargari, "A new nested neutral point-clamped (NNPC) converter for medium-voltage [5] (MV) power conversion," IEEE Transactions on Power Electronics, vol. 29, no. 12, pp. 6375-6382, 2014, doi: 10.1109/TPEL.2014.2306191.

- N. Guler, H. Komurcugil, S. Biricik, and H. R. Karimi, "Model predictive control for single-phase three-level grid-connected Ftype inverters," Complex Engineering Systems, vol. 1, no. 1, 2021, doi: 10.20517/ces.2021.07.

- K. Wang, Z. Zheng, L. Xu, and Y. Li, "Neutral-Point Voltage Balancing Method for Five-Level NPC Inverters Based on Carrier-Overlapped PWM," IEEE Transactions on Power Electronics, vol. 36, no. 2, pp. 1428-1440, 2021, doi: 10.1109/TPEL.2020.3006960.

- J. Ebrahimi, S. Shahnooshi, S. Eren, H. Karshenas, and A. Bakhshai, "Optimized Switching Frequency Voltage Balancing Schemes for Flying Capacitor Based Multilevel Converters," IEEE Transactions on Industrial Electronics, vol. 70, no. 11, pp. 10775–10788, 2023, doi: 10.1109/TIE.2022.3227263.

- T. M. Krishna and C. B. Kumar, "A new hybrid Multi Level Inverter to improve the performance of induction motor," in 4th IEEE [9] Sponsored International Conference on Computation of Power, Energy, Information and Communication, ICCPEIC 2015, 2015, pp. 264-268, doi: 10.1109/ICCPEIC.2015.7259473.

- P. K. Chamarthi, M. S. El Moursi, A. Al Durra, K. H. Al Hosani, and A. Al Sumaiti, "Enhanced Pulse Width Modulation Methods for 1-φ Five-Level Neutral Point Clamped Inverter," 2022 IEEE Energy Conversion Congress and Exposition, ECCE 2022, 2022, doi: 10.1109/ECCE50734.2022.9947633.

- M. R. A and K. Sivakumar, "A Fault-Tolerant Single-Phase Five-Level Inverter for Grid-Independent PV Systems," IEEE Transactions on Industrial Electronics, vol. 62, no. 12, pp. 7569-7577, Dec. 2015, doi: 10.1109/TIE.2015.2455523.

- [12] I. Harbi et al., "Common DC-Link Multilevel Converters: Topologies, Control and Industrial Applications," IEEE Open Journal of Power Electronics, vol. 4, pp. 512-538, 2023, doi: 10.1109/OJPEL.2023.3291662.

- [13] S. P. Gautam, M. Jalhotra, L. K. Sahu, M. R. Kumar, and K. K. Gupta, "A Survey on Fault Tolerant and Diagnostic Techniques of Multilevel Inverter," IEEE Access, vol. 11, pp. 60866-60888, 2023, doi: 10.1109/ACCESS.2023.3285722.

- A. Ghosh, A. Shukla, and A. Joshi, "Control of dc capacitor voltages in diode-clamped multilevel inverter using bidirectional buckboost choppers," *IET Power Electronics*, vol. 5, no. 9, pp. 1723–1732, Nov. 2012, doi: 10.1049/iet-pel.2012.0237.

J. Ebrahimi, S. Shahnooshi, S. Eren, and A. Bakhshai, "A Modulation Scheme Based on Virtual Voltage Levels for Capacitor

- Voltage Balancing of the Four-Level Diode Clamped Converter," IEEE Transactions on Power Electronics, vol. 38, no. 4, pp. 4727-4744, Apr. 2023, doi: 10.1109/TPEL.2022.3228482.

- [16] S. Srikanthan and M. K. Mishra, "DC capacitor voltage equalization in neutral clamped inverters for DSTATCOM application," IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2768–2775, 2010, doi: 10.1109/TIE.2009.2022069.

- V. Jayakumar, B. Chokkalingam, and J. L. Munda, "A Comprehensive Review on Space Vector Modulation Techniques for Neutral Point Clamped Multi-Level Inverters," IEEE Access, vol. 9, pp. 112104-112144, 2021, doi: 10.1109/ACCESS.2021.3100346.

- [18] A. Poorfakhraei, M. Narimani, and A. Emadi, "A Review of Modulation and Control Techniques for Multilevel Inverters in Traction Applications," IEEE Access, vol. 9, pp. 24187–24204, 2021, doi: 10.1109/ACCESS.2021.3056612.

- N. Prabaharan, V. Arun, P. Sanjeevikumar, L. Mihet-Popa, and F. Blaabjerg, "Reconfiguration of a multilevel inverter with trapezoidal pulse width modulation," Energies, vol. 11, no. 8, 2018, doi: 10.3390/en11082148.

- K. B. Kumar, A. Bhanuchandar, B. Supriya, D. Vamshy, K. Palle, and R. Sakile, "A Unipolar Phase Disposition Pulse Width Modulation Technique for an Asymmetrical Multilevel Inverter Topology," in Proceedings - 2021 IEEE International Conference ICISSGT 2021, 2021, pp. Intelligent Systems, Smart and Green Technologies, 156–161, doi: 10.1109/ICISSGT52025.2021.00041.

- [21] S. Mishra, D. Pullaguram, S. Achary Buragappu, and D. Ramasubramanian, "Single-phase synchronverter for a grid-connected roof top photovoltaic system," IET Renewable Power Generation, vol. 10, no. 8, pp. 1187-1194, Sep. 2016, doi: 10.1049/ietrpg.2015.0224.

- M. A. G. de Brito, E. H. B. Dourado, L. P. Sampaio, S. A. O. da Silva, and R. C. Garcia, "Sliding Mode Control for Single-Phase Grid-Connected Voltage Source Inverter with L and LCL Filters," Eng, vol. 4, no. 1, pp. 301–316, 2023, doi: 10.3390/eng4010018.

- M. Karimi-Ghartemani, "A Unifying Approach to Single-Phase Synchronous Reference Frame PLLs," IEEE Transactions on

- Power Electronics, vol. 28, no. 10, pp. 4550–4556, Oct. 2013, doi: 10.1109/TPEL.2012.2235185.

M. Islam, N. Afrin, and S. Mekhilef, "Efficient Single Phase Transformerless Inverter for Grid-Tied PVG System With Reactive Power Control," IEEE Transactions on Sustainable Energy, vol. 7, no. 3, pp. 1205-1215, Jul. 2016, 10.1109/TSTE.2016.2537365.

- A. Bhanuchandar and B. K. Murthy, "Switched Capacitor Based 13-Level Boosting Grid Connected Inverter with LCL Filter," 2021, doi: 10.1109/NPEC52100.2021.9672544.

- N. Arab, H. Vahedi, and K. Al-Haddad, "LQR control of single-phase grid-tied PUC5 inverter with LCL filter," IEEE Transactions on Industrial Electronics, vol. 67, no. 1, pp. 297-307, 2020, doi: 10.1109/TIE.2019.2897544.

## **BIOGRAPHIES OF AUTHORS**

Y. Sravan Kumar ( is a research scholar at the Department of Electrical Engineering, Osmania University. He obtained his master's and bachelor's from Jawaharlal Nehru Technological University, Hyderabad, India in 2011 and 2008 respectively. He worked as an associate professor and assistant professor for over a decade. His research interests include control systems, power electronics, and electromagnetic fields. He can be contacted at email: y.sravan16@gmail.com.

Yesuratnam Guduri received B.Tech. degree in Electrical and Electronics Engineering from Jawaharlal Nehru Technological University, Hyderabad, India in 1995. He received an M.Tech. degree in 1998 from Regional Engineering College, Warangal in the field of power systems. He received a Ph.D. degree from the Department of Electrical Engineering, Indian Institute of Science, Bangalore in 2007. Currently, he is working as a senior professor in the Department of Electrical Engineering, University College of Engineering, Osmania University, Hyderabad. His research interests include computeraided power system analysis, reactive power optimization, voltage stability, and artificial intelligence applications in power systems. He can be contacted at email: ratnamgy2003@gmail.com.