Vol. 16, No. 1, March 2025, pp. 311~320

ISSN: 2088-8694, DOI: 10.11591/ijpeds.v16.i1.pp311-320

# Teaching learning optimization technique FOPID controlled Cuk and SEPIC converter-based PF rectification

Alok Kumar Mishra<sup>1</sup>, Soumya Ranjan Das<sup>2</sup>, Nimay Chandra Giri<sup>3</sup>, Sangram Kishore Routray<sup>4</sup>, Fathy Abdelaziz Syam<sup>5</sup>, Ehab S. Elwakil<sup>5</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Siksha O Anusandhan University, Bhubaneswar, India

<sup>2</sup>Department of Electrical Engineering, Parala Maharaja Engineering College, Berhampur, India

<sup>3</sup>Department of Electronics and Communication Engineering, Centurion University of Technology and Management, Odisha, India

<sup>4</sup>Faculty of Engineering and Technology, SRI SRI University, Cuttack, Odisha, India

<sup>5</sup>Department of Power Electronics and Energy Conversion, Electronics Research Institute, Cairo, Egypt

### **Article Info**

#### Article history:

Received Mar 15, 2024 Revised Sep 16, 2024 Accepted Oct 23, 2024

# Keywords:

Average current control Fractional order PIDC Power factor rectification Teaching learning-based optimization THD

### ABSTRACT

The foremost cause of harmonic contamination is the ample utilization of loads of non-linear type such as static power converters. Because of this load, the input power factor (PF) decreases heavily as they draw a current of non-sinusoidal in nature. This article gives a general presentation investigation of two PF rectification (PFR) converter (PFRC) geographies: Cuk type and single-ended primary-inductance converter or SEPIC type converter. The average current control (ACC) technique is utilized here. Notwithstanding, for control of output voltage, techniques like conventional proportional integral derivative controller (PIDC) or fractional order proportional integral derivative controller (FOPIDC) are used, and the gains of the controller are calculated using a novel teaching learning optimization technique (TLOT), considering integral time absolute error (ITAE). The analysis of both PFRC acted in Simulink/MATLAB and the estimated converters are studied under consistent and dynamic state conditions. The FOPIDC Cuk PFRC is providing 2.97% of THD compared to other converters.

This is an open access article under the **CC BY-SA** license.

311

### Corresponding Author:

Fathy Abdelaziz Syam

Department of Power Electronics and Energy Conversion, Electronics Research Institute

Cairo, 12622, Egypt Email: fathy@eri.sci.eg

### 1. INTRODUCTION

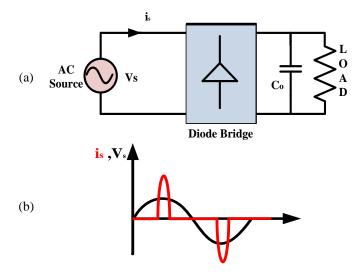

The impact of power quality is worsening daily due to the commercial and industrial loads with their non-linear characteristics [1]. Therefore, it is necessary to improve the power quality and power factor using different compensating devices and power factor correction devices. Power factor (PF) rectification (PFR) has arisen as a fundamental piece of the cutting-edge power system for its usage and power transfer. A diode bridge and capacitor in shunt [2] are utilized to get DC voltage output. PFR outline is portrayed in Figure 1(a), while in Figure 1(b), a comparison of supply voltage-current is portrayed. As Figure 1(b) tends to see, the input current is nonlinear amid extensive harmonics [3], and the input PF is exceedingly reduced. The current harmonics [4]-[6] are wisely adverse due to electromagnetic interference or EMI problems through communication or line voltage tainting paths. Be that as it may, if such sorts of most extreme burdens are related to the supply, there will be a difficult issue. A portion of the global norms, similar to the IEC & IEEE license the limitations of harmonic incidence in supply current akin to IEEE 519 [7]-[9].

The primary goal here is to look after an AC-DC PFR to cancel out the above PF issues [10], [11] and to achieve unity power factor (UPF) at supply and regulated voltage at output [12]. Again, in comparison to

previous work such as [11], [13], in this work the PF rectification (PFR) converter PFRC has been tested under transient conditions and the % output voltage ripple is calculated to ensure reduced filter capacitor burden. A one-switch DC converter is used for single-phase AC-DC and minute power utilizations. These types of converters may be directed at the wanted voltage output, in addition to UPF at the input side. In aperfect world, there are three essential kinds of converter geographies in non-segregated classification, for example, buckboost, buck, and boost configuration [14]-[16]. Every time a small voltage output is required, at that point buck PFRC is required; however, buck converter provides an input current of commuted type with elevated frequency. Be that as it may, given its driven nature, it gives an intruded-on current related to a quick recovery circuit. The significant fault with the Buck PFRC is: it requires a filter inductorat the input side.

The filter inductor creates a variable consistent current in the supply region. However, boost PFRC configurations create enormous result voltage and cause excess-voltage trouble on the switch [17]. The third converter, i.e. buck-boost, was found to be essential for PFRC. This converter includes ZETA, Cuk, and single-ended primary-inductance converter or SEPIC [18]. In this writing, two distinct configurations, for example, SEPIC and Cuk are utilized for PFR, amid minimum total harmonic distortions (THD) of input current alongside directed DC voltage and diminished voltage ripple [19]-[21]. The total plan and PFRC models are finished utilizing the MATLAB/Simulink tool.

The major contribution of the proposed study is as: i) To create a fractional order proportional integral derivative (FOPID)-controlled Cuk and SEPIC converter Simulink model to improve the system's power factor; ii) Optimised fractional order proportional integral derivative controller (FOPIDC) is used to extract the peak of current reference; iii) Teaching learning optimization technique (TLOT) is employed for optimization of controller parameters of FOPIDC; iv) Controller (FOPIDC) actions are tested in steady-state and transient conditions; and v) Relative study to declare the superior rejoinder of TLOT based FOPID-controlled Cuk converter. The supplementary sections of the manuscript are organized in the following way. Cuk and SEPIC converter design and analysis along with different PFRC methods and the proposed optimization technique, is discussed in detail in section 2. Section 3 discusses results and analysis. Sections 4 present the future scope and conclusions.

Figure 1. AC-DC converter along with voltage and current waveforms: (a) diode bridge and capacitor in shunt with load and (b) supply voltage-current

### 2. CONVERTER DESIGN AND ANALYSIS

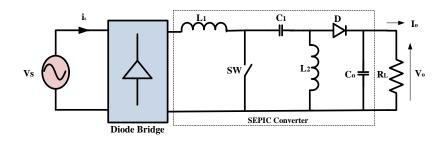

A converter (Cuk or SEPIC) of DC-DC type is interfaced close to the rectifier, to get a superior PF and desired voltage in system supply and load, respectively. The introduced AC-DC SEPIC and Cuk PFRC circuit configurations are shown separately in Figures 2 and 3. Input current wave can decrease by utilizing this arrangement with controlled output voltage. This issue is highly excellent in regular buck/boost converter. Both inductors (input and output) are kept in similar attractive centers in a converter like Cuk or SEPIC to accomplish the most extreme coupling coefficient. Whenever,  $L_1$  and  $L_2$  the inductors, store energy switched ON, increasing current in the inductor-capacitor provides power to output. Diode becomes RB for this situation. In switch OFF duration, the diode becomes forward bias (FB), storesenergy, and is put away to load. Table 1

portrays the demonstrated conditions of the expected PFRCs. Where  $V_o$  and  $P_o$  is, load voltage and power,  $\Delta v_o$  and  $\Delta v_c$  represents, voltage ripple of output and capacitor, Again the current ripple of an inductor, supply voltage, frequency of switching and duty cycle represents as:  $f_s$  and d.

Figure 2. Structure of SEPIC PFRC

Figure 3. Structure of Cuk PFRC

|            | Table 1.             | Design for           | mula of Cuk  | and SEFIC FFI          | NC .                   |

|------------|----------------------|----------------------|--------------|------------------------|------------------------|

| Parameters | SEPIC                | Cuk                  | Parameters   | SEPIC                  | Cuk                    |

| $L_1$      | $v_s * d$            | $v_s * d$            | $C_1$        | $iL_2 * d$             | $I_0 * (1 - d)$        |

|            | $\Delta i L_1 * f_s$ | $\Delta i L_1 * f_s$ |              | $\Delta v_{c_1} * f_s$ | $\Delta v_{c_1} * f_s$ |

| $L_2$      | $v_s*d$              | $v_s * d$            | $C_{\alpha}$ | $P_{o}$                | $v_s * d$              |

$4\pi * f_s * V_o * \Delta v_o$

Table 1 Design formula of Cuk and SEPIC PERC

# 2.1. Different PFRC methods

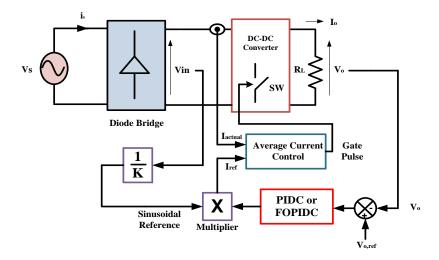

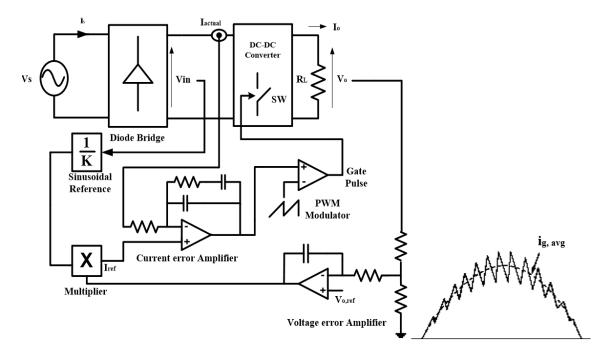

The fundamental objective of PFRC is to get the desired voltage at load, and secondly, the source current must be a sine wave. In this manner, a response from the load is utilized to get the desired voltage. Besides, to achieve the other goal, two techniques are generally utilized: the multiplier technique (MT) [22] and the voltage follower technique (VFT) [13], [23]-[25]. The VFT method of PFRC is generally used for very low power application and produce high devices current hassle. In the Multiplier Technique, a current response is utilized from the source to manage the PFRC alongside the voltage response, as represented in Figure 4. The MT method is further classified into four types such as: i) Peak current control (PCC); ii) Hysteresis current control (HCC); iii) Borderline current control (BCC); and iv) Average current control (ACC)

There are some demerits of the other three (PCC, HCC, BCC) MT method such as: PCC method needs an external compensation ramp, HCC method produces variable switching frequency pulse width modulation (PWM) pulses, BCC method is more sensitive to commutation noises and needs a zero current detector circuit. To overcome the above issues, in our proposed work ACC method is used which gives a constant switching frequency PWM pulses, does not need a compensation ramp and less sensitive to commutation noise. Hence, Figure 5 depicts the ACC method which gives a reduced %THD input current used here. Generally, a current error amplifier filters the input inductor current, which in turn drives the PWM modulator. Because of the current loop at the input, the error gets reduced between the reference and input current. Whereas, the PIDC or FOPIDC gives the current reference, an amplifier of voltage error type. Again, in ACC, a constant switching frequency PWM pulse is obtained, which in turn eliminates the commutation noises. No compensation ramp is required in ACC, but the actual inductor current needs to be sensed in ACC.

314 □ ISSN: 2088-8694

Figure 4. Multiplier technique

Figure 5. MT with ACC technique

# 2.2. PIDC and FOPIDC

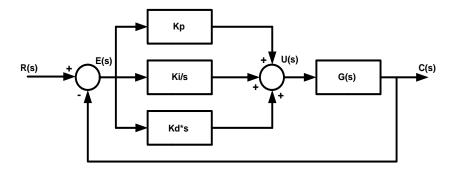

PIDC is outlined in Figure 6. PIDC is known numerically (1).

$$u(t) = K_p e(t) + K_i \int_0^t e(t) + K_d \frac{de(t)}{dt}$$

(1)

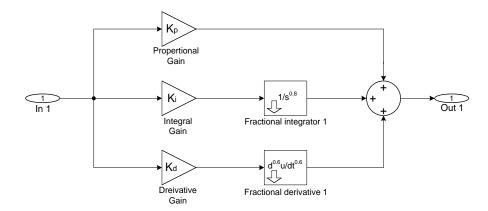

A fractional order  $PI^{\alpha}D^{\beta}$  controller-based PFC converter is presented in Figure 4 . In FOPID control, e(t) the error signal, produce u(t) the control signal. FOPIDC transfer function can be formulated as (2) [9].

$$TF = K_p + \frac{\kappa_i}{s^{\alpha}} + K_d s^{\beta} \tag{2}$$

In (2)  $K_p$ ,  $K_i$ , and  $K_d$  are the PID gains respectively and  $\alpha$ ,  $\beta$  are fraction of integrator and differentiator. Necessary steps for FOPIDC design are:

- Put in  $K_p$  to decline, rise time and error at steady-state.

- $K_d$  is added to lessen % OS and time to settle.

- Further include  $K_i$  eliminating error at steady-state.

- Polish up again  $K_p$ ,  $K_i$ ,  $K_d$ ,  $\alpha$ , and  $\beta$ , to get the wanted output.

- FOPIDC Simulink structure is depicted in Figure 7.

- In MATLAB/Simulink using the FOMCON toolbox and TLOT, FOPIDC parameters are designed as shown in Table 2.

Figure 6. PIDC

Figure 7. FOPIDC Simulink diagram

| Table 2. Values of FOPIDC |       |       |     |     |  |  |  |  |

|---------------------------|-------|-------|-----|-----|--|--|--|--|

| $K_p$                     | $K_d$ | $K_i$ | α   | β   |  |  |  |  |

| 15.11                     | 3.89  | 2.34  | 0.8 | 0.6 |  |  |  |  |

# 2.3. TLOT

TLOT is known to be a novel information-based approach, in which the best student of the past will become the teacher in the next iteration. Subsequently, the further students have to be trained as of thatnew teacher & distribute their information to transform the measured pupil's information. In this way, previous or unpredicted convergence can be avoided, and the multiplicity can be conserved. In the last few decades, a lot of researchers have found attention in the optimization area. Mutation and crossover are found to be the foremost steps in any evolutionary techniques, but not in TLOT. TLOT has lots of similarities with various other evolutionary techniques and is aggravated by teaching-learning activities. Based on self-learning and other's experience, each member possesses an adjustable explore method in TLOT. Once the global optimum is found, to attract the whole member to that position, this experience is communicated to them. From the literature, it is obvious that TLOT may be implemented effortlessly and works greatly superior compared to other techniques. TLOT may be trapped in any neighboring maxima or minima for an intricate and multi-modal problem, which can be avoided by extensive-range learning methods.

316 □ ISSN: 2088-8694

### 2.4. Objective function

Here the objective function (OF) is of ITAE type, and the DC link capacitor voltage error is the OF [9]-[12]. The foremost objective is to minimize the error e(t), which is the variation between actual and reference DC link capacitor voltage. An abrupt raise or reduction in load is considered here for this J, the OF, as given in (3).

$$J = \int_0^{t \sin t} t|e(t)| dt \tag{3}$$

### 3. RESULTS AND DISCUSSION

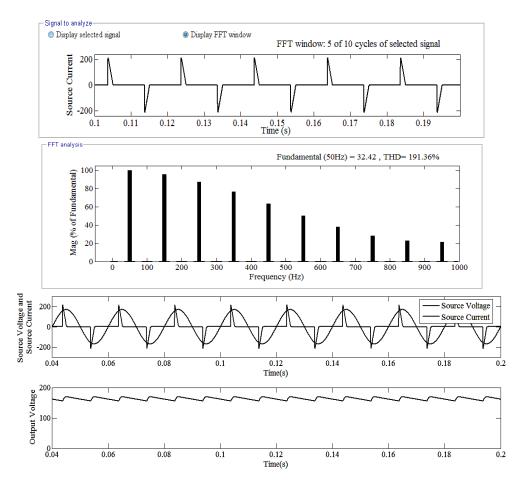

The Simulink structure is made in Simulink programming to analyze exhibitions of the anticipated Cuk and SEPIC PFRC. Table 3 depicts the framework model boundary of the two PFRC. First, the framework is broken down without associating any PFRC. %THD examination and different wave shapes are shown in Figure 8. Like Figure 1, the supply current is a pulse type comprising bunches of harmonics having 191.36% of %THD. Now Cuk, SEPIC PFRC is used to enhance system performances. First, the PFC converter is tested in an open loop (OL) and with PID controlled Cuk and SEPIC PFRC, results are given in Table 4.

Figure 8. Without converter results

Table 3. System considerations

| D .                | 37.1         | D (                               | X 7 1  |

|--------------------|--------------|-----------------------------------|--------|

| Parameters         | Values       | Parameters                        | Values |

| RMS supply voltage | 120 V        | Power output                      | 1000 W |

| Supply frequency   | 50 Hz        | Output voltage reference          | 100 V  |

| $L_1, L_2$         | 6 mH, 10 mH  | Switching frequency               | 40 KHz |

| $C_1, C_o$         | 10 mF, 10 mF | $\%\Delta v_o$ and $\%\Delta v_c$ | 5%     |

| d                  | 0.45         |                                   |        |

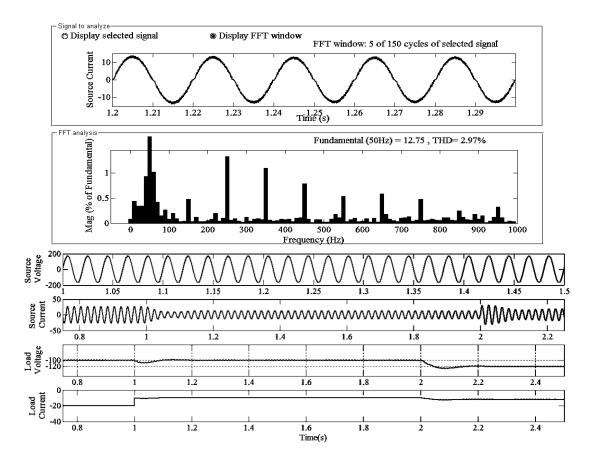

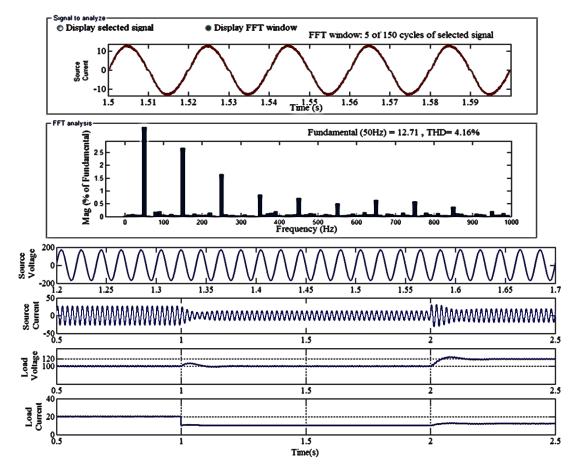

Different waveforms like supply current fast Fourier transform FFT examination, supply voltage, load voltage and supply current of FOPIDC based Cuk PFRC are portrayed separately in Figure 9. The primary contrast between Cuk and SEPIC PFRC is, Cuk produces a reverse voltage output the FOPIDC based SEPIC PFRC portrayed in Figure 10. To test regulator strength a variation of the load is used at 1sec. It tends to be seen that voltage is constant at -100 V. Supply PF, %THD source current is viewed as 0.9980, 3.73% and 0.9999, 2.97% separately for PIDC and FOPIDC Cuk PFRC. From THD values the FOPIDC Cuk PFRC produce improved outcome than PIDC Cuk PFRC.

Figure 9. Wave shapes of FOPIDC Cuk PFRC

Likewise, in the following phase, SEPIC PFRC is integrated into the framework, involving PIDC & FOPIDC regulators in the response path. Different wave shapes, for example, supply current FFT examination, supply voltage, and load voltage/current of FOPIDC based SEPIC PFRC are portrayed in Figure 10. For strength testing, alongside load variation a reference variation (100 V to 120 V for SEPIC PFRC and -100 V to -120 V for Cuk PFRC) is used at 2 sec. Again, it tends to be noticeable, as seen in Figure 10, that FOPIDC SEPIC PFRC produces preferable performance over PIDC SEPIC PFRC. Again, a comparative study is also done from the previous work [17] and [13] to ensure the superiority of the proposed work. A proportional integral controlled (PIC) and fuzzy logic controlled (FLC) Cuk PFRC is proposed, and the supply PF, %THD is found to be 0.9990, 3.13% and 0.9991, 2.87% separately for PIC and FLC based Cuk PFRC [17]. Samarth and Gemlawala [13] have proposed a PIC based boost PFRC and found the 0.9997, 6.81% as the supply PF, %THD. Contrasting all 10 contextual investigations FOPIDC Cuk PFRC produces superior execution

318 □ ISSN: 2088-8694

parameters, for example, the least %THD, decreased load voltage ripple and further developed supply PF. Different outcomes acquired in various contextual analyses are organized in Table 4.

Figure 10. Wave shapes of FOPIDC SEPIC PFRC

### 4. CONCLUSION

In this work for PFR, 2 PFRC converters, SEPIC and Cuk, using ACC method are utilized to be specific. The main advantages of the proposed control method are unvarying switching frequency, does not require any reparation ramp and because of current filtering, the method is fewer perceptive to commutation noise. The output voltage of the converter has the same polarity as that of the input voltage. Similarly, the SEPIC has unique features, such as non-inverted output, continuous input and output currents, and better performance. The projected PFRC is performed employing the Simulink tool. The simulated results show the enhancement in supply current %THD with nearly UPF at the supply and diminished ripple load voltage. When contrasted with PIDC, FOPDIC gives further developed results, for example, supply current %THD and PF. Besides, FOPDIC-based Cuk conveys a well-desired voltage, the least %THD (2.97%) during the unsettling influences of load and deviation of reference. The estimated PFRC SEPIC and Cuk are to be investigated in real-time, for better insight into the same and will be our future work.

# **ACKNOWLEDGEMENTS**

This work was upheld by Siksha 'O' Anusandhan University, Odisha, India, and PMEC, Berhampur, India. This work was contributed by the Electronics Research Institute, Cairo, Egypt.

### REFERENCES

[1] D. P. Mishra, B. S. Panda, N. S. Mallik, S. Kar, N. C. Giri, and S. R. Salkuti, "Demand side management in a microgrid to reduce the peak consumption cost," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 14, no. 2, pp. 819-826, Jun. 2023, doi: 10.11591/ijpeds.v14.i2.pp819-826.

- [2] V. K. Yadav, "A high PFC integrated AC–DC circuit with inherent lossless LCD Snubber," *IEEE Journal of Emerging and Selected Topics in Industrial Electronics*, vol. 5, no. 1, pp. 62–71, Jan. 2024, doi: 10.1109/JESTIE.2023.3310399.

- [3] S. R. Das, D. P. Mishra, P. K. Ray, S. R. Salkuti, and A. K. Sahoo, "Power quality improvement using fuzzy logic-based compensation in a hybrid power system," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 12, no. 1, pp. 576-584, Mar. 2021, doi: 10.11591/ijpeds.v12.i1.pp576-584.

- [4] S. R. Das, J. Paramguru, and T. K. Panigrahi, "Harmonics minimization using non-linear feedback control based hybrid filter," in 2022 IEEE 2nd International Symposium on Sustainable Energy, Signal Processing and Cyber Security (iSSSC), IEEE, Dec. 2022, pp. 1–6. doi: 10.1109/iSSSC56467.2022.10051443.

- [5] A. Moradi, J. Yaghoobi, A. Alduraibi, F. Zare, D. Kumar, and R. Sharma, "Modelling and prediction of current harmonics generated by power converters in distribution networks," *IET Generation, Transmission & Distribution*, vol. 15, no. 15, pp. 2191–2202, Aug. 2021, doi: 10.1049/gtd2.12166.

- [6] H. B. Assia and M. Fatima, "Analysis of harmonics currents in the case of grid connected photovoltaic generator," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 14, no. 4, p. 2379, Dec. 2023, doi: 10.11591/ijpeds.v14.i4.pp2379-2387.

- [7] A. K. Mishra et al., "Power factor corrected SEPIC and Cuk converter-a comparison," in Lecture Notes in Networks and Systems, vol. 109, 2020, pp. 299–312. doi: 10.1007/978-981-15-2774-6\_37.

- [8] N. Mishra, B. Singh, S. K. Yadav, and M. Tariq, "Power quality improvement in fifteen level PUC converter for solar PV grid-tied applications," *IEEE Trans Ind Appl*, vol. 59, no. 4, pp. 4264–4273, Jul. 2023, doi: 10.1109/TIA.2023.3260067.

- [9] P. Kumar and I. Srikanth, "Power quality performance enhancement by PV-based distribution static compensator under incremental conductance maximum power point tracking algorithm," *Cleaner Energy Systems*, vol. 4, 2023, doi: 10.1016/j.cles.2023.100062.

- [10] U. D. Dwivedi, D. Shakya, and S. N. Singh, "power quality monitoring and analysis: an overview and key issues," *International Journal of Signal System Control and Engineering Application*, vol. 1, no. 1, no. 1, pp. 74–88, 2008.

- [11] M. K. Shehata, H. E. M. Attia, B. E. Elnaghi, and N. F. Ibrahim, "Power factor correction AC-DC boost converter using PI-hysteresis current control," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 14, no. 3, pp. 1597-1603, Sep. 2023, doi: 10.11591/ijpeds.v14.i3.pp1597-1603.

- [12] I. Jagadeesh and V. Indragandhi, "Solar photo voltaic based hybrid CUK, SEPIC, ZETA converters for microgrid applications," e-Prime-Advances in Electrical Engineering, Electronics and Energy, vol. 6, 2023, doi: 10.1016/j.prime.2023.100364.

- [13] P. Samarth and D. B. Gemlawala, "PFC boost topology using average current control method," *International Journal of Innovative and Emerging Research in Engineering*, vol. 3, no. 5, pp. 39–44, 2016.

- [14] A. K. Mishra, P. K. Nanda, P. K. Ray, S. R. Das, and A. K. Patra, "IFGO optimized self-adaptive fuzzy-PID controlled HSAPF for PQ enhancement," *International Journal of Fuzzy Systems*, vol. 25, no. 2, pp. 468–484, 2023, doi: 10.1007/s40815-022-01382-0.

- [15] D. Yoon, Y. Cho, S. Bae, and J. Lee, "An input-series output-series noninverting buck-boost converter for 1500 V DC bus with wide input and output voltage ranges," *IEEE Transactions on Industrial Electronics*, vol. 70, no. 11, pp. 11231–11241, Nov. 2023, doi: 10.1109/TIE.2022.3231265.

- [16] A. D. Kumar, J. Gupta, and B. Singh, "A single-stage charger for LEV based on quadratic buck-boost AC-DC converter topology," IEEE Trans Ind Appl, vol. 59, no. 4, pp. 4252–4263, Jul. 2023, doi: 10.1109/TIA.2023.3259944.

- [17] A. K. Mishra et al., "Power factor corrected Cuk converter with PI and fuzzy logic controller," in Lecture Notes in Electrical Engineering, vol. 665, 2020, pp. 1035–1047. doi: 10.1007/978-981-15-5262-5\_80.

- [18] A. K. Mishra et al., "Output voltage regulated Cuk and SEPIC converter with high input power factor," in Lecture Notes in Electrical Engineering, vol. 665, 2020, pp. 785–799. doi: 10.1007/978-981-15-5262-5\_59.

- [19] A. Ruderman, "About voltage total harmonic distortion for single- and three-phase multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 3, pp. 1548–1551, Mar. 2015, doi: 10.1109/TIE.2014.2341557.

- [20] W. Xu, W. Zhu, and Z. Shu, "Suppression of DC voltage ripple impact on non-isolated single-phase half-bridge unified power quality conditioner," *IEEE Transactions on Industrial Electronics*, vol. 71, no. 9, pp. 10523–10532, Sep. 2024, doi: 10.1109/TIE.2023.3337497.

- [21] B. A. Kumar, B. Jyothi, R. S. Rathore, A. R. Singh, B. H. Kumar, and M. Bajaj, "A novel framework for enhancing the power quality of electrical vehicle battery charging based on a modified Ferdowsi converter," *Energy Reports*, vol. 10, pp. 2394–2416, Nov. 2023, doi: 10.1016/j.egyr.2023.09.070.

- [22] A. T. S. Subramanian, P. Sabarish, and A. N. Ali, "A power factor correction based canonical switching cell converter for VSI fed BLDC motor by using voltage follower technique," in 2017 IEEE International Conference on Electrical, Instrumentation and Communication Engineering (ICEICE), IEEE, Apr. 2017, pp. 1–8. doi: 10.1109/ICEICE.2017.8191932.

- [23] K. V. Gopan and J. D. Shree, "Analysis of bridge type and bridgeless Cuk converter fed motor drives for improved power quality," International Journal of Electronics, vol. 110, no. 7, pp. 1179–1212, Jul. 2023, doi: 10.1080/00207217.2022.2121427.

- [24] M. A. Nezhad and A. Mahani, "Design of low-power approximate logarithmic multipliers with improved accuracy," *Journal of Applied Research in Electrical Engineering*, vol. 2, no. 1, 2023.

- [25] M. S. Abishek et al., "Exergy-energy, sustainability, and emissions assessment of Guizotia abyssinica (L.) fuel blends with metallic nano additives," Scientific Reports, vol. 14, no. 1, p. 3537, Feb. 2024, doi: 10.1038/s41598-024-53963-8.

### **BIOGRAPHIES OF AUTHORS**

320 ☐ ISSN: 2088-8694

Soumya Ranjan Das [6] [5] sompleted his Ph.D. in the area of Power Quality and Alcontrolled techniques in 2021 from the Department of Electrical Engineering, International Institute of Information and Technology Bhubaneswar. He works with the Department of Electrical Engineering, PMEC, Berhampur. His research interests include power quality, power converters, robust, and adaptive control techniques in grid-interactive renewable systems. He can be contacted at email: soumyaranjan.ee@pmec.ac.in.

Sangram Kishore Routray 🕞 🖾 🖒 received a B.E. in Electronics and Instrumentation (EIE) at Berhampur University, Odisha, India, in 2002 and an M.Tech. in Communication Systems Engineering from KIIT University, Odisha, India in 2008. He is Pursuing a Ph.D. in Cybersecurity (CSE). He is currently serving as an assistant professor (Cybersecurity) SRI SRI University, Cuttack, Odisha, India. He has 18 years of teaching experience. He can be contacted at email: sangram.kist@gmail.com.

Fathy Abdelaziz Syam (D) SS (S) is assistant professor at Electronics Research Institute, Power Electronics and Energy Conversion Department, Egypt. He Holds a Ph.D. degree in Electrical Power and Machines with specialization in Renewable Energy Systems from Cairo University in 2004. His research areas are solar energy, wind energy, microgrid, electrical machines, and power system. He can be contacted at email: fathy@eri.sci.eg.

Ehab S. Elwakil is a researcher at Electronics Research Institute, Power Electronics and Energy Conversion Department, Egypt. He received B.S., from Zagazig University, M.Sc. from Cairo University and Ph.D. in Electrical and Computer School of Engineering from Brunel University, West London, UK in 1992, 2001 and 2009 respectively. He works as full-time lecturer between 2012 and 2022. His research interests include electric drives, power electronics and digital control. He can be contacted at email: elwakil@eri.sci.eg.