# System-on-chip design for improved switching angle driven 35-level LUO progression-based multi-level inverter

Joseph Anthony Prathap, J. Kanti Prasad, Vivekananda Reddy, Chinthapalli Suheil

Department of Electronics and Communication Engineering, School of Engineering, Presidency University, Bengaluru, India

### **Article Info**

### Article history:

Received Apr 9, 2024 Revised Jan 28, 2025 Accepted Mar 1, 2025

#### Keywords:

Improved switching angle LUO progression Performance analysis Switched ladder inverter Switching pattern System-on-chip

#### **ABSTRACT**

This article concentrates on the development of the IC layout for the driving switches of the inverter with improved switching control. This work uses the improved non-carrier switching pattern algorithms to have precise control of inverter switches with twin objectives of i) reducing the total harmonic distortion (THD)% and ii) developing a dedicated system on chip for the improved switching control of the 35-level switched ladder multi-level inverter. The DC voltage of the inputs to the inverter is designated based on the LUO progression, which consists of an improved mathematical formula for deriving its values. Conventionally, the multi-level inverter circuits are driven by the pulse width modulation signals by overlapping the modulating sine wave with different levels of triangle waves, such as phase disposition, phase opposite disposition, and alternate phase opposite disposition, utilized to drive various voltage source inverter topologies. Although the MLI design concentrates on minimal THD%, factors like accuracy, minimum number of switches, and cost demands for advanced switching strategy algorithms. This paper compares the improved switching angle method to the existing algorithm by considering VPEAK, VRMS, and %THD for the 35-level LUO progression-based switched ladder inverter. The IC layout for the improved switching control is developed using the hardware description language code in the Cadence tool and validated by cross-compiling in Simulink MATLAB.

This is an open access article under the <u>CC BY-SA</u> license.

974

### Corresponding Author:

Joseph Anthony Prathap

Department of Electronics and Communication Engineering, School of Engineering, Presidency University Itgalpur, Rajanakunte, Yelahanka, Bengaluru, India

Email: joseph.anthony@presidencyuniversity.in

## 1. INTRODUCTION

Inverters contribute to the generation of AC output by making use of power electronic circuits. The circuit topology of the inverter consists of DC sources and switches that are controlled by the drive. The multi-level inverter (MLI) circuit performance is dependent on the number of switches used in the topology, with less total harmonic distortion (THD)% [1]-[3]. The multi-level inverter topology with symmetric and asymmetric DC values has minimum cost [4]. The increased cost can be eradicated by an asymmetrical structure that gives large voltage levels with minimum switches [5]. The minimization in the switch count triggers the decrease of switching losses and the cost of the topology [6].

Conventionally, the drive for the switches involves pulse width modulation (PWM) signals for the generation of AC output. The PWM signals are generated with a low frequency to compensate for the complexity of the switching patterns [7]. The parameters of the inverter switches are manipulated mathematically to compare with the different topologies of the MLI [8].

The THD% evaluation is pivotal for the validation of any MLI topology. The reduction in the THD% of the inverter is compared with the LS and PS-based SPWM generation to implement the MLI using the lesser

П

switches AC output for the MLI levels is possible for both symmetrical and asymmetrical DC sources by using the double source double diode double switch [9]. The asymmetrical MLI topology can achieve high levels in the output, however, the complexity in the circuit topology demands separate voltage sources with the increase in cost [10]. Although there is a tiny reduction in the THD% with the CHB compared to the TCHB topology, the CHB topology goes under twice the stress in switching as the TCHB [11]. The selection of switches with its count and the optimized calculation of the switching angles for the MLI exhibits lower THD% [12].

Recently, there have been several inclusions and modifications in the MLI topology seeking a specified parameter. By making use of a level shifter in the fusion of cross cross-connecting switch inverter (CCSI) and a modified multilevel inverter (MMLI), higher levels of AC output were achieved [13]. The MLI with only one voltage source and a capacitor attains high voltage levels with low distortion in the harmonics [14]. The positional modification of the DC inputs will reduce the current harmonics in the MLI output [15]. The peak input energy can be harvested with a multi-input dual-output MLI topology [16]. The addition of a switch capacitor has been advantageous in the of lower ripples, lower switch count, and improved voltage gain for the hybrid-based MLI [17]. The ability to reduce the amplitude of the harmonics is achieved by the spectrum distribution in the MLI circuit and finds applications in communication and defense equipment, and heavy vehicles [18], [19].

The inclusion of the integrated boost flyback converter enhances the 31-level MLI to be efficient [20]. The fault tolerance in the MLI circuit is enhanced by the addition of redundant switches. The merit of this addition is the ability to identify multiple faults without affecting the performance of the power inverter. [21]. The use of switches with high frequency in positive levels and voltage reversed in negative levels of the MLI observed that the loss of 50% in THD% is the same as the specified output voltage [22]. The modulation-based PWM is involved in the generation of the AC output to emphasize the fluctuations and flicker in the MLI [23]. The advent of FPGA with the switching control of the MLI circuit is essential to generate the AC output with low cost and lower THD%. The accuracy and speed of switching in the MLI circuits are improved when implemented using the FPGA device [24]. The FPGA device usage in the control of cascaded MLI reduces the THD% and eliminates 3<sup>rd</sup> and 5<sup>th</sup> harmonics. This paper proposes an improved switching angle algorithm with the state of charge (SOC) layout for the 35-level LUO-based progression switched ladder inverter.

# 2. PROPOSED METHOD: IC LAYOUT FOR THE PROPOSED 35-LEVEL LUO PROGRESSION-BASED MULTI-LEVEL INVERTER

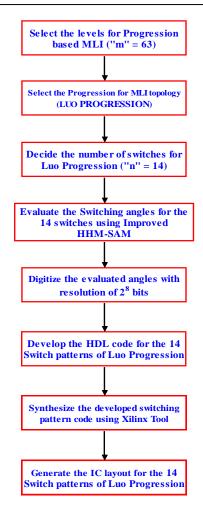

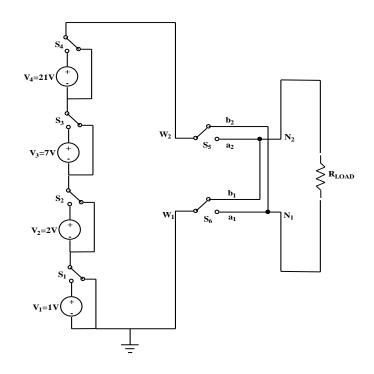

The proposed method concentrates on the generation of the IC layout plan for the switching patterns of the multi-level inverter (MLI) generated by the use of an improved non-carrier switching angle method. in this work, the switch patterns are produced for the MLI that has its input DC values based on the LUO progression. The LUO progression-based MLI topology consists of 14 switches to be driven to generate the AC output. The challenge lies in the precise patterning of these switches as required for the AC generation. The design flow for the proposed method is depicted in Figure 1. The proposed method could generate any level of MLI from 3 to 81. In this work, the 35-level LUO progression-based MLI is used to generate the AC output. The LUO progression-based MLI uses the power circuitry topology as given in Figure 2. The LUO progression-based multi-level inverter uses the formula as given in (1) and (2).

$$V_i = i, \quad \text{if} \quad i \le 2;$$

(1)

$$= 7 \times 3^{i-2}$$

, if  $i \ge 3$  (2)

Where Vi is the input voltages of the LUO progression inverter.

For the 35-level LUO progression-based MLI circuit, the voltage sources of 1 V, 2 V, 7 V, and 21 V are used to give 17 positive levels, 17 negative levels, and 1 zero level for the AC output. The level voltages combined for the generation of AC output are given in Table 1. The algorithm utilizes an improved non-carrier angle evaluation method to derive the levels of the multi-level inverter. In this work, the angles are produced based on the improved Half Height Event manipulation method which can present the angles in sequence till the half and in alternate sequence after the half of the positive and negative cycles with an addition of Integer value '1'. The equation for the HHM algorithm is given in (3).

$$\alpha_i = \sin^{-1}\left[\left(\left(i - \frac{1}{2}\right)\frac{2}{m-1}\right) + 1\right]$$

(3)

Where  $i = 1, 2, \dots, \frac{m-1}{2}$ .

976 □ ISSN: 2088-8694

Figure 1. Design flow for the proposed 35-level LUO progression-based SLI

Figure 2. Circuit diagram for the LUO progression-based switched ladder multi-level inverter

The (3) presented formula is manipulated in the floating point for the angles. These angles are translated into digital values with 2<sup>8</sup> resolutions. The x-axis angles from 0° to 360° of a cycle are converted as 0 to 255 bits in digital format. The LUO progression-based inverter consists of two parts of the voltage switches namely DC voltage ladder switches and polarity switches as shown in Figure 2. The DC voltage ladder switches combine the DC voltages through the switches as required for the level in the inverter design.

As shown in Figure 1, the code for the proposed method is developed using the HDL language. The behavioral style of the HDL code is used to generate the switch patterns of the MLI. The synthesis of the developed code is validated using the EDA tools namely Xilinx and cadence. The IC layout is obtained by making use of the genus and innovus tools in the cadence.

| Table 1 | Voltage le | evel combinat | tion for the | : 35-level LUO | progression-based MLI |

|---------|------------|---------------|--------------|----------------|-----------------------|

|         |            |               |              |                |                       |

| Positive levels | Voltages              | Negative levels | Voltages                    |

|-----------------|-----------------------|-----------------|-----------------------------|

| 0               | 0                     | 0               | 0                           |

| 1               | 1 V                   | -1              | -1 V                        |

| 2               | 2 V                   | -2              | -2 V                        |

| 3               | 1 V +2 V              | -3              | -1 V -2 V                   |

| 4               | 7 V -2 V -1 V         | -4              | -7 V + 2 V + 1 V            |

| 5               | 7 V -2 V              | -5              | -7 V + 2 V                  |

| 6               | 7 V -1 V              | -6              | -7 V +1 V                   |

| 7               | 7 V                   | -7              | -7 V                        |

| 8               | 7 V + 1 V             | -8              | -7 V -1 V                   |

| 9               | 7 V + 2 V             | -9              | -7 V -2 V                   |

| 10              | 7 V + 2 V + 1 V       | -10             | -7 V -2 V -1 V              |

| 11              | 21 V -7 V -2 V -1 V   | -11             | -21  V + 7  V + 2  V + 1  V |

| 12              | 21 V -7 V -2 V        | -12             | -21 V + 7 V + 2 V           |

| 13              | 21 V -7 V -1 V        | -13             | -21  V + 7  V + 1  V        |

| 14              | 21V -7 V              | -14             | -21 V + 7 V                 |

| 15              | 21 V -7 V + 1 V       | -15             | -21 V + 7 V -1 V            |

| 16              | 21 V -7 V + 2 V       | -16             | -21 V + 7 V -2 V            |

| 17              | 21 V -7 V + 2 V + 1 V | -17             | -21 V + 7 V -2 V -1 V       |

# 3. RESULTS AND DISCUSSION

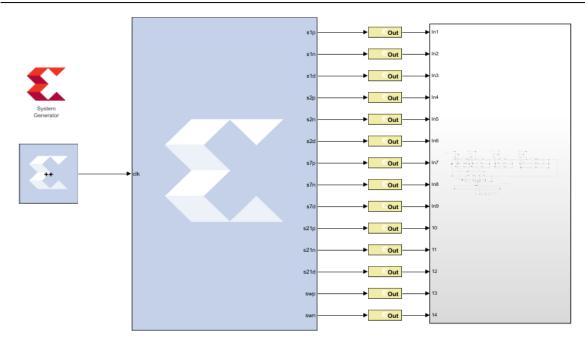

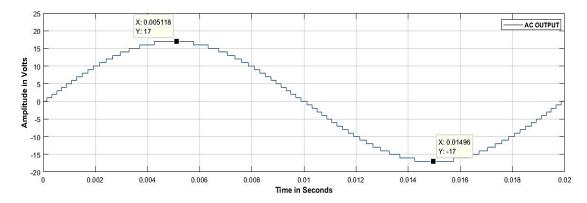

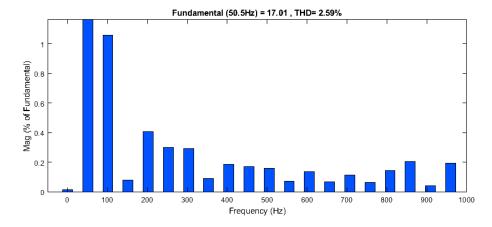

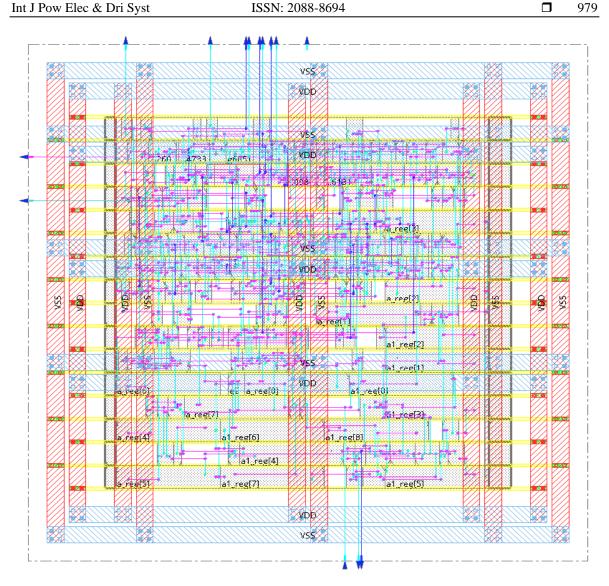

The proposed method for the development of IC layout for the 35-level LUO progression switched ladder multi-level inverter is validated using MATLAB and EDA cadence tool. The MATLAB tool is utilized to verify the functionality of the algorithm to correctly generate the switch patterns of the MLI circuit. The Switch patterns in digital form are developed using the HDL code and translated into Xilinx Simulink Block to be cross-compiled as given in Figure 3. This cross-compiling option provides an opportunity to interlink the developed non-carrier-based switch patterns in HDL with the analog topology of the switched ladder inverter. The execution of the cross-compiled setup produces the AC output for the 35-level LUO progression-based SLI as depicted in Figure 4. The parametric evaluation for the proposed method is carried out for the THD% and is shown in Figure 5. The THD% value for the 35-level LUO progression SLI is 2.59% which is relatively low compared to the [25] that used 8 bits of resolution for the HDL in the switching of H-bridge CMLI topology. Table 2 proves the merit of the THD% for the proposed method is low in comparison with the HCMLI circuit. Also, the number of switches utilized is only 6 for the LPSLI whereas the HCMLI uses 12 switches. The objective of this paper is attained lower THD% for the given 35-level LUO based SLMLI by making use of the improved HHM-SAM. Table 3 validates the enhancement of the proposed method with the value of 2.59% in THD compared to the 2.64% in THD for the conventional SAM algorithm. The other object of developing the SOC is depicted in Figure 6. The IC layout plan for the 35-level LPSLI switching algorithms is developed by making use of cadence EDA tools. Overall, three tools are used for the IC chip layout design namely incisive, genus, and innovus for simulation, synthesis, and IC layout respectively.

Table 2. Comparison of the proposed 35-level LPSLI circuit with the H-bridge CHMLI

| Methods         | Level | No of switches | Resolution    | THD%  |

|-----------------|-------|----------------|---------------|-------|

| [25]            | 35    | 12             | 28 & 212 bits | 3.28% |

| Proposed method | 35    | 6              | 28 bits       | 2.59% |

Table 3. Comparison of the proposed improved HHM-SAM with the conventional HHM-SAM

| Methods         | Level | V <sub>RMS</sub> | $V_{PFAK}$ | THD%  |

|-----------------|-------|------------------|------------|-------|

| Existing<br>HHM | 35    | 12.05            | 17.04      | 2.64% |

| Improved<br>HHM | 35    | 12.03            | 17.01      | 2.59% |

Figure 3. Simulink model for the proposed 35-level LUO progression-based Xilinx block

Figure 4. AC output for the 35-level LUO progression-based MLI using the Xilinx Simulink blocks

Figure 5. THD% calculation for the 35-level LUO progression-based MLI using the Xilinx Simulink blocks

Figure 6. IC chip layout for the 35-level LUO progression-based MLI using cadence tool

# **CONCLUSION**

The proposed 35-level LUO based switched ladder multi-level inverter is driven by the improved switching angle method driven switch patterns to exhibit THD% as low as 2.59% compared to the conventional angle formulation method with the THD% of 2.64%. The application-specific SOC is successfully designed for the proposed improved non-carrier switching patterns of the 35-level LUO progression-based switched ladder inverter. Future work could be invested in the fault analysis of these driving switches using a deep learning algorithm.

# ACKNOWLEDGEMENTS

The authors would like to thank the Presidency University, Bengaluru for providing the VLSI cadence lab in utilizing the EDA tools and for the contribution to this research article.

# FUNDING INFORMATION

Authors state no funding involved.

# **AUTHOR CONTRIBUTIONS STATEMENT**

This journal uses the Contributor Roles Taxonomy (CRediT) to recognize individual author contributions, reduce authorship disputes, and facilitate collaboration.

980 🗖 ISSN: 2088-8694

| Name of Author         | C | M            | So | Va | Fo           | I            | R | D            | O | E            | Vi | Su | P            | Fu |

|------------------------|---|--------------|----|----|--------------|--------------|---|--------------|---|--------------|----|----|--------------|----|

| Joseph Anthony Prathap | ✓ | ✓            | ✓  | ✓  | ✓            | ✓            |   |              | ✓ | ✓            | ✓  | ✓  | ✓            |    |

| J. Kanti Prasad        |   | $\checkmark$ | ✓  |    | $\checkmark$ | $\checkmark$ |   | $\checkmark$ | ✓ | $\checkmark$ |    |    | $\checkmark$ |    |

| Vivekananda Reddy      |   | $\checkmark$ | ✓  |    | $\checkmark$ | $\checkmark$ | ✓ |              |   | $\checkmark$ |    |    |              |    |

| Chinthapalli Suheil    |   | ✓            | ✓  |    | ✓            | ✓            |   |              | ✓ |              |    |    |              |    |

Va: Va idation O: Writing - O riginal Draft Fu: Fu indiag acquisition

Fo: Formal analysis E: Writing - Review & Editing

#### CONFLICT OF INTEREST STATEMENT

Authors state no conflict of interest.

#### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author, [JAP], upon reasonable request.

#### REFERENCES

- [1] M. Karakılıç and M. N. Almalı, "Design of hybrid switched diode multilevel inverter using single DC source," *Journal of Electrical Engineering and Technology*, vol. 19, no. 7, pp. 4169–4180, 2024, doi: 10.1007/s42835-024-01832-9.

- [2] M. A. N. Doss, N. Kalaiarasi, K. Suba, B. Sathishkumar, L. Ramesh, and S. G. Fernandez, "Open circuit switch fault detection in multilevel inverter using artificial neural network," AIP Conference Proceedings, vol. 3037, no. 1, 2024, doi: 10.1063/5.0196365.

- [3] M. Amir, M. S. Alam, A. Haque, F. I. Bakhsh, and N. Shah, "Design and implementation of a reduced switch seventeen-level multilevel inverter for grid integration of battery storage system," *Journal of Energy Storage*, vol. 86, 2024, doi: 10.1016/j.est.2024.111213.

- [4] V. Singh, K. K. KARRI, and S. Pattnaik, "Performance assessment of a new reduced component multilevel inverter with discrete modulation techniques," *International Journal of Power Electronics*, vol. 19, no. 1, 2024, doi: 10.1504/ijpelec.2024.10059146.

- [5] A. Radhakrishnan, E. S. Arasan, B. C. Ramalingam, and K. Chandrasekaran, "A new asymmetric H-6 structured multilevel inverter with reduced power components," *Symmetry*, vol. 16, no. 1, 2024, doi: 10.3390/sym16010072.

- [6] A. T. A. Arulappan, M. Selvaraj, and A. Aladian, "SHE PWM based 21 level inverters with hardware analysis," *International Journal of Power Electronics and Drive Systems*, vol. 15, no. 2, pp. 993–1000, 2024, doi: 10.11591/ijpeds.v15.i2.pp993-1000.

- [7] U. Gajula, K. Manivannan, and N. M. Reddy, "Performance analysis for induction motor fed by reduced switch symmetrical multilevel inverter topology," *International Journal of Power Electronics and Drive Systems*, vol. 15, no. 2, pp. 925–934, 2024, doi: 10.11591/ijpeds.v15.i2.pp925-934.

- [8] R. Memon, M. A. Mahar, A. S. Larik, and S. A. A. Shah, "An asymmetrical multilevel inverter with minimum voltage stress and fewer components for photovoltaic renewable-energy system," *Clean Energy*, vol. 8, no. 1, pp. 1–22, 2024, doi: 10.1093/ce/zkad073.

- [9] V. Kubendran, Y. Mohamed Shuaib, S. Vidyasagar, V. Kalyanasundaram, and K. Saravanan, "The development of a generalized multilevel inverter for symmetrical and asymmetrical DC sources with a minimized-ON state switch," *Ain Shams Engineering Journal*, vol. 15, no. 2, 2024, doi: 10.1016/j.asej.2023.102358.

- [10] B. Mosepele, R. Samikannu, and L. Amuhaya, "A structural review on reduced switch count and hybrid multilevel inverters," Frontiers in Energy Research, vol. 12, 2024, doi: 10.3389/fenrg.2024.1396149.

- [11] O. I. Mohammed, L. A. Mohammed, and A. M. T. Ibraheem Al-Naib, "Design and analysis of seven multilevel cascaded H-bridge inverter controlled by FPGA," NTU Journal of Engineering and Technology, vol. 3, no. 3, Sep. 2024, doi: 10.56286/ntujet.v3i3.863.

- [12] T. A. Hussein, D. Ishak, and M. Tarnini, "A three-phase multilevel inverter synthesized with 31 levels and optimal gating angles based on the GA and GWO to supply a three-phase induction motor," *Energies*, vol. 17, no. 5, 2024, doi: 10.3390/en17051267.

- [13] L. Vijayaraja, S. Ganesh Kumar, M. Rivera, and E. Babaei, "Performance enhancement of reduced component multilevel inverter with optimal placement of level shifter," *IEEE Latin America Transactions*, vol. 22, no. 6, pp. 502–511, 2024, doi: 10.1109/TLA.2024.10534310.

- [14] P. Kar et al., "A novel reduced component high boost multilevel inverter," IEEE Access, vol. 12, pp. 124658–124680, 2024, doi: 10.1109/ACCESS.2024.3450720.

- [15] A. B. Barnawi, A. R. A. Alfifi, Z. M. S. Elbarbary, S. F. Alqahtani, and I. M. Shaik, "Review of multilevel inverter for high-power applications," *Frontiers in Engineering and Built Environment*, vol. 4, no. 2, pp. 77–89, May 2024, doi: 10.1108/FEBE-05-2023-0020.

- [16] S. J. Salehi, M. A. S. Nejad, and H. R. Najafi, "A new multi-input two-output switched-source multilevel inverter based on harvest of maximum energy for photovoltaic applications," *International Journal of Power Electronics*, vol. 19, no. 2, pp. 167–192, 2024, doi: 10.1504/JJPELEC.2024.136561.

- [17] K. Jena et al., "A novel multigain switched-capacitor-based topology with reduced part count," International Transactions on Electrical Energy Systems, vol. 2024, 2024, doi: 10.1155/2024/2944846.

- [18] Q.-T. Tran, "An application of neural network-based sliding mode control for multilevel inverters," Engineering, Technology & Applied Science Research, vol. 14, no. 1, pp. 12530–12535, Feb. 2024, doi: 10.48084/etasr.6516.

- [19] S. S. K. Kumar and P. K. Dhal, "Design and implementation of novel variants of multi-level inverters for traction and heavy vehicle applications," *International Journal of Powertrains*, vol. 12, no. 1, p. 54, 2023, doi: 10.1504/IJPT.2023.129671.

- [20] A. Praveena and K. Sathishkumar, "Power quality improvement using a 31-level multi-level inverter with bio-inspired optimization approach," Frontiers in Energy Research, vol. 12, 2024, doi: 10.3389/fenrg.2024.1264157.

- [21] V. Ramanarayana, K. N. Rao, B. Kumar, and S. V. K. Naresh, "A single-phase five-level multilevel inverter with rated power fault-tolerant feature," AEU International Journal of Electronics and Communications, vol. 190, 2025, doi: 10.1016/j.aeue.2024.155645.

- [22] B. Pragathi, S. Kumar, P. R. Kumari, and A. R. Singh, "Performance evaluation of hybrid multilevel inverter with a high-frequency switching technique," *Journal of Engineering and Applied Science*, vol. 70, no. 1, 2023, doi: 10.1186/s44147-023-00267-9.

- [23] K. Sarker, K. Sarker, J. Sarker, P. Bhowmik, D. Chatterjee, and S. K. Goswami, "Power quality investigation with multilevel inverter by photovoltaic-fed dynamic voltage restorer," *International Journal of Modelling and Simulation*, 2024, doi: 10.1080/02286203.2024.2327647.

- [24] E. Noorsal, A. Rongi, I. R. Ibrahim, R. Darus, D. Kho, and S. Setumin, "Design of FPGA-based SHE and SPWM digital switching controllers for 21-level cascaded H-bridge multilevel inverter model," *Micromachines*, vol. 13, no. 2, 2022, doi: 10.3390/mi13020179.

- [25] J. A. Prathap and T. S. Anandhi, "Field programmable gate array-based new fusion control for photovoltaic inverter," *Computers and Electrical Engineering*, vol. 98, 2022, doi: 10.1016/j.compeleceng.2022.107738.

# **BIOGRAPHIES OF AUTHORS**

J. Kanti Prasad to so is currently pursuing a Bachelor of Technology (B.Tech.) in Electronics and Communication Engineering at Presidency University, located in Bangalore, India. Actively engaged in research projects, he demonstrates a commitment to interdisciplinary approaches in addressing engineering challenges. His contributions within academia and industry underscore his dedication to advancing knowledge and driving technological innovation. His research interests encompass renewable energy systems, machine learning applied to power systems, semiconductor device fabrication, and wireless communication protocols. He can be contacted at email: kantiprasad810@gmail.com.

Vivekananda Reddy is pursuing a Bachelor of Technology in Electronics and Communication Engineering at Presidency University, Bangalore, India. Vivekananda actively demonstrates his commitment to the profession through his membership in the Institute of Electrical and Electronics Engineers (IEEE). He has already made a mark in the field with a published paper on OTFS modulation at an IEEE conference. His passion for electronics is multifaceted, encompassing VLSI design, PCB layout, wireless communications, and the ever-evolving field of machine learning. He can be contacted at email: vivekanandareddy0501@gmail.com.

Chinthapalli Suheil is currently pursuing a Bachelor of Technology (B.Tech.) in Electronics and Communication Engineering at Presidency University, located in Bangalore, India. His proficiency in communication systems is evident through his conference paper on OTFS modulation, which showcases his expertise in signal processing techniques. Actively engaged in research projects, he demonstrated a commitment to interdisciplinary approaches in addressing engineering challenges. His research interests encompass power electronics, artificial intelligence applied to power systems, VLSI technology, and channel modulation. He can be contacted at email: chinthapallisuheil123@gmail.com.