Vol. 16, No. 1, March 2025, pp. 673~682

ISSN: 2088-8694, DOI: 10.11591/ijpeds.v16.i1.pp673-682

# Single-stage transformer less multilevel boost inverter with zero leakage current for PV system

## Dalya Hamzah Al-Mamoori<sup>1</sup>, Shahrin Md Ayob<sup>1</sup>, M. Saad Arif<sup>2</sup>

<sup>1</sup>Department of Electrical Power Engineering, Faculty of Electrical Engineering, Universiti Teknologi Malaysia, Johor Bahru, Malaysia <sup>2</sup>Department of Electrical Engineering, Faculty of Engineering and Technology, Aligarh Muslim University, Aligarh, India

#### **Article Info**

## Article history:

Received Aug 23, 2024 Revised Nov 20, 2024 Accepted Nov 28, 2024

#### Keywords:

Boost Leakage current Multilevel-inverter Single source Transformer less

## **ABSTRACT**

Transformer less inverters (TIs) are highly efficient and have a high power density, making them a popular choice for grid-connected solar PV applications. However, certain topologies can lead to high-frequency common-mode voltage (CMV), which can cause issues such as high leakage current, electromagnetic interference, and an absence of safety. Our newly developed inverter is designed to be more efficient, cost-effective, and compact than traditional types while also addressing the issue of leakage current. This architecture eliminates leakage current by directly connecting the grid's neutral terminal to the PV's negative polarity, resulting in a low leakage current. Moreover, the inverter increases output voltage using only one voltage source and a few power devices, making it a cost-effective solution. Its modular form allows for an increase in output levels, further enhancing its cost-effectiveness. We conducted a comprehensive mathematical examination, and the MATLAB/Simulink results demonstrate its ability to increase the output voltage, eliminate leakage current, and maintain acceptable output voltage THD and current waveforms. These results and the inverter's safety features showcase significant improvements over traditional inverters and provide a secure and reliable solution for gridconnected solar PV applications.

This is an open access article under the <u>CC BY-SA</u> license.

673

## Corresponding Author:

Dalya Hamzah Al-Mamoori Department of Electrical Power Engineering, Faculty of Electrical Engineering Universiti Teknologi Malaysia 81310 UTM Johor Bahru, Johor Darul Takzim, Malaysia

Email: dalyahamzahmussa@graduate.utm.my

# 1. INTRODUCTION

In photovoltaic (PV) applications, transformers are commonly used for galvanic isolation and voltage ratio conversions. However, traditional transformers add weight, bulk, and expense to the inverter while reducing efficiency and power density. To address these issues and prevent safety concerns like ground fault and leakage currents, we aim to design an inverter that does not require transformers and can operate safely without additional precautions [1]–[4].

Various topological topologies, including circuit designs based on AC and DC dissociating, have been suggested in the literature to statement leakage current problems [5], [6]. The most often used and effective topology of this kind is the (HERIC) topology, built on the AC decoupling technique offered in this study. Other DC topologies contain H5 and various forms of H6. But still have the leakage current issue. Furthermore, conduction losses and the inverter's incapacity to the main disadvantages of such inverter topologies are increased [7]–[14].

Journal homepage: http://ijpeds.iaescore.com

Voltage using neutral-point-clamped (NPC) inverters is an additional option that reduces leakage current to a manageable range by keeping the common-mode voltage (CMV) constant. Increasing the output voltage levels also improves the quality of electricity. The most advanced and effective topologies in this category of inverter structures are the flying capacitor (FC)-based t-type and active neutral-point-clamped (ANPC). Recently, a five-level inverter built on an impedance source was described in [15]–[19].

This inverter's poor voltage gain, large component count, and leakage current are its key shortcomings. Consequently, EMI filters are included to reduce high-frequency volatility in CMV, which raises the inverter's cost. Conversely, in these topologies, the maximum AC voltage is just half the DC-link voltage; therefore, a two-stage power managing design with a further boost converter is required for low-voltage solar energy systems [20], [21]. As an alternative, a unique way for satisfying the demands of grid-connected renewable energy sources, particularly PV sources, is to use (CG) TI that may eliminate the issue of high-frequency (CMV), which causes leakage current. Based on the common-ground method, SCMLIs for reducing leakage current have lately acquired acceptance in the literature. They are described as a unique 5-L common-ground CG-type inverter using dual SCs, six switches, and a diode designed for PV systems. Additional sensors are required to balance the SC voltages [22]–[26]. Compact MLIs with boosting capabilities and minimal THD voltage generation are required for PV systems. MLIs based on switched capacitors (SC) have recently become popular as DC/AC voltage converters with boosting capabilities [27]. The SC unit's output voltage range is changeable.

It is dependent on the arrangement and spans a wide range. A traditional active neutral point clamp (ANPC) architecture utilizing capacitors was created [28]. Five output voltage levels beyond the load may be produced with a single DC voltage source, eight IGBTs, and three capacitors. However, there is no way to boost production levels in the load terminal.

Nevertheless, this arrangement does not have a way to raise the output voltage. Two new kinds of ANPC topologies were presented in [29]. These topologies are unable to enhance voltage, and this paper describes a new 5-level boost inverter with continuous gain controller capabilities. The inverter needs an inductor to supply continuous input current in both DC and AC modes, essential for photovoltaic and other renewable energy applications. Because the negative end of the DC source is linked to the neutral terminal of the grid, the design has minimal LC and few components.

The paper's structure follows: section 2 explains the construction of the suggested 5-level multilevel boost inverter. Section 3 explains the switch mechanism and pulse-generating method. Section 4 shows MATLAB Simulink findings for the inverter, which ends in section 5.

## 2. PROPOSED TOPOLOGY

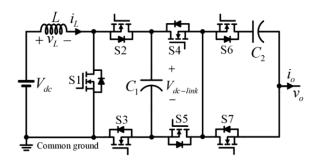

Figure 1 shows the inverter's circuit architecture, which includes a boost inductor to sustain continuous input current and give adjustable gain voltage, seven switches, and two capacitors. The inverter uses a single DC source designed specifically for photovoltaic (PV) systems. Additionally, this provides a large boost gain, with the peak output voltage set at 2M/(1-D) for a 5-level output.

Figure 1. The basic block of the proposed 5-level inverter topology

## 2.1. Operating modes

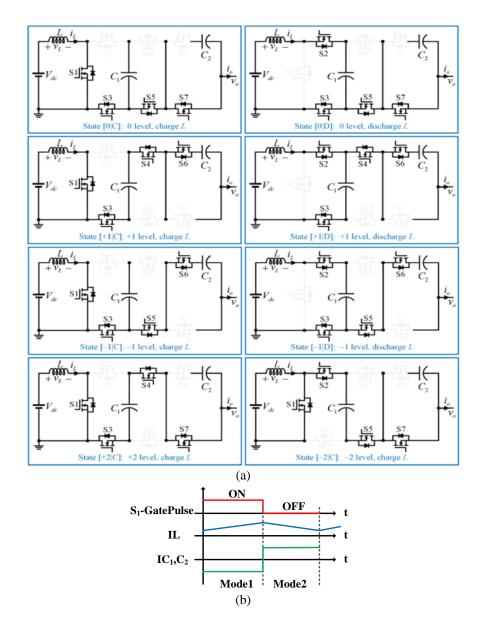

In this section, Figure 2(a) illustrates the primary operational modes of the proposed 5-level converter. These establish distinct operating settings for each voltage stage, guaranteeing a consistent output voltage even during faults. Moreover, the system incorporates multiple charging and discharging modes to suit varying levels of inverter power. This design maintains the equilibrium of the capacitors' voltage and simplifies the

control of the boost duty cycle, resulting in additional benefits, for instance, capacitor voltage balancing. Furthermore, the input inductance within this inverter undergoes charging during the conduction phase of the IGBT S1, while it experiences discharge when the power switch S1 transitions to the off state. Consequently, the key waveforms pertinent to the proposed inverter are illustrated in Figure 2(b). As illustrated in Figure 2(a), the state (+1) consists of two operational conditions: the state of inductor charging and the state of inductor discharging; during the charging phase, the inductor is energized by the direct current (DC) source when switch S1 is activated, in this state the switches S1, S3, S4, S6are activated to reach the +1 level. During the discharging phase, switch S2 is activated, while switches S3, S4, and S6 remain conducting to reach the -1 level, and the same operation principle is used for the rest states.

Figure 2. Operational modes of the (a) charging and discharging stages of the input boost inductor and (b) key waveforms associated with the inverter during both charge and discharge functions

# 2.2. Voltage gain analysis

The gain of the suggested inverter can be determined as follows, considering the DC source voltage and the AC output voltage.

$$Gi = \frac{2M}{1 - D} \tag{1}$$

676 □ ISSN: 2088-8694

Since every capacitor in the proposed inverter has the same amount of charge, the voltage of every capacitor may be determined as follows:

$$V_{C1} = V_{C2} = \frac{V_{DC}}{1 - D} \tag{2}$$

As a result, the highest maximum voltage is equal to the total voltages across the previously stated capacitors. Thus, the following methods can be used to obtain it:

$$V_{O,Max} = \frac{2V_{DC}}{1-D} \tag{3}$$

Table 1 shows equations demonstrating the relationship between the output voltage and the modulation index. Variations in the duty cycle (D) may affect the peak value of the waveform. Table 2 shows the disparities in maximum output voltage. When the modulation index surpasses 0.5, the level shift PWM (LS-PWM) approach creates a 5-level waveform for the inverter output from a sinusoidal reference voltage signal. When the modulation index falls below 0.5, the converter output switches to a three-level waveform.

Table 1. The association between a modulation index and the output waveform

| Output voltage                 | Rang of modulation index | Range of output voltage waveform             |

|--------------------------------|--------------------------|----------------------------------------------|

| $V_O = \frac{2MV_{DC}}{1 - D}$ | 0 to 1                   | $V_O \Rightarrow 0$ to $\frac{2V_{DC}}{1-D}$ |

Table 2. illustrates various modulation index ranges

| Modulation index | Output levels | Gain voltage                                         |

|------------------|---------------|------------------------------------------------------|

| M > 0.5          | 5             | $V_{0,peak} = 2$                                     |

| M < 0.5          | 3             | $\frac{V_{DC}}{V_{O,peak}} - \frac{1-D}{1-D}$        |

| -                |               | $\frac{\overline{V_{DC}}}{V_{DC}} = \frac{1-D}{1-D}$ |

## 2.3. Design factors

This section covers the suggested inverter model concerns for switches, input boost inductors, and capacitors. As demonstrated by the preceding formulations, equations indicating the voltage stress of the switches are constructed.

$$V_{4,6} = \frac{1}{1-D} V_{DC}, V_{1,2,3,5,7} = \frac{2}{1-D} V_{DC}$$

$$\tag{4}$$

Additionally, the input boost inductor may be developed by the subsequent equation:

$$L_{in} \ge \frac{DV_{DC}}{f_s \Delta i_I} \tag{5}$$

Furthermore, the following definition may be applied to the values of the inverter capacitors:

$$C_{1,2,\dots n} \ge \frac{D(1-D)I_0G}{f_S\Delta V_C} \tag{6}$$

## 3. METHODOLOGY

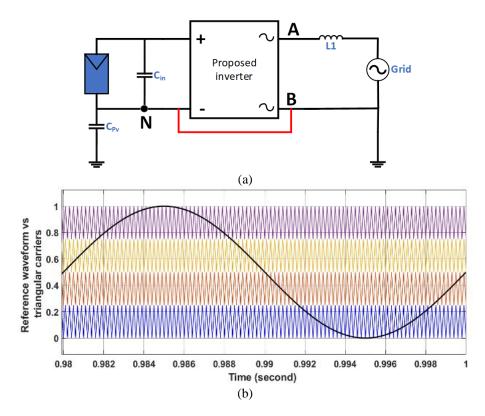

Due to the input and output terminals sharing common ground, the suggested inverter has zero CMV. Figure 3(a) shows that the sinusoidal waveform value from point B to neutral point N is zero (VBN). The PV array's parasitic capacitor ( $C_{PV}$ ) is short-circuit due to the inverter's common ground capabilities. Consequently, the leakage current through  $C_{PV}$  is also zero. As a result, the inverter's CMV value can be calculated as (7).

$$V_{CM.Total} = \frac{V_{AN}}{2} + (V_{AN}) \left(\frac{-L_1}{2(L_1)}\right) = 0$$

(7)

### 3.1. Modulation and switching rules

The proposed topology produces a sinusoidal waveform at the output by controlling the IGBTs with level shift modulation. Figure 3(b) shows the carrier signal waveforms concerning the reference sinusoidal waveform. Four triangular carrier waveforms are included in a 5-level inverter. Every voltage state of the inverter corresponds to one or more switching situations. Table 3 shows the switching table with five levels from -2 V to +2 V3.

Figure 3. The inverter structure common ground and the level shift PWM, (a) the planned inverter association to the AC grid's general schematic and (b) triangle carrier signals compared to the suggested inverter's reference sinusoidal waveform

Table 3. Switching states for 5-level MLI

|                  |                |       | -0    |       |       |       | -     |           |

|------------------|----------------|-------|-------|-------|-------|-------|-------|-----------|

| Level / Switches | Power switches |       |       |       |       |       |       | Inductor  |

|                  | $S_1$          | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ |           |

| 0                | 1              | 0     | 1     | 0     | 1     | 0     | 1     | Charge    |

|                  | 0              | 1     | 1     | 0     | 1     | 0     | 1     | Discharge |

| +1               | 1              | 0     | 1     | 0     | 0     | 1     | 0     | Charge    |

|                  | 0              | 1     | 1     | 1     | 0     | 1     | 0     | Discharge |

| -1               | 1              | 0     | 1     | 0     | 1     | 1     | 0     | Charge    |

|                  | 0              | 1     | 1     | 0     | 1     | 1     | 0     | Discharge |

| -2               | 1              | 1     | 0     | 0     | 1     | 0     | 1     | Charge    |

| +2               | 1              | 0     | 1     | 0     | 0     | 0     | 1     | Charge    |

## 4. RESULTS AND DISCUSSION

As previously explained, the proposed inverter operates in continuous boost mode with a constant input current and 0% leakage current. Furthermore, the loss value findings using the PLECS software illustrate the proportion of losses for each inverter component. The critical parameter values used through the simulation are detailed in Table 4. Table 5 contrasts the proposed inverter to a variety of topologies.

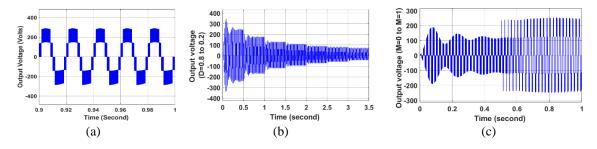

Figure 4(a) illustrates the five-level output voltage characterized by a peak value of 240 V, utilizing the parameter specifications provided in Table 4. Figure 4(b) illustrates the variations in output voltage as the duty cycle is adjusted in increments of 10%, ranging from D = 80% to D = 20%. A notable attribute of the proposed inverter is its ability to regulate the peak output voltage across a broad operational spectrum.

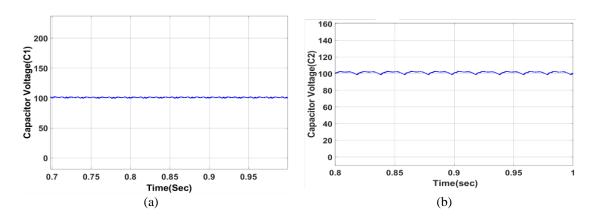

Figure 4(c) illustrates the modulation index value altered from 0 to its maximum (M = 1). The converter produces a three-level voltage when M < 0.5 and a five-level waveform when M > 0.5, as detailed in Table 2. Figures 5(a) and 5(b) present the voltage measurements of the topology capacitors (C1 and C2).

Table 4. Simulation parameter estimates of the proposed inverter

| Tueste in Similaration paramiteter estimates of the proposed inverte |                                  |        |                                                |  |  |  |  |  |  |

|----------------------------------------------------------------------|----------------------------------|--------|------------------------------------------------|--|--|--|--|--|--|

| Value                                                                | Parameter                        | Value  | Parameter                                      |  |  |  |  |  |  |

| 3 mH                                                                 | Input inductor (L <sub>b</sub> ) | 24 V   | Source (V <sub>dc</sub> )                      |  |  |  |  |  |  |

| $100 \ \Omega + 10 \ \text{mH}$                                      | Inductive load                   | 1200µF | Capacitor (C <sub>1</sub> and C <sub>2</sub> ) |  |  |  |  |  |  |

| Level shift PWM                                                      | PWM                              | 10 kHz | $F_{(SW)}$                                     |  |  |  |  |  |  |

| 80%                                                                  | D                                | 1      | M                                              |  |  |  |  |  |  |

Table 5. Comparison of 5-level boost inverters with other inverter topologies

| Structure | S | D | С | L | $N_{Level}$ | Gain               | CC | CG           |

|-----------|---|---|---|---|-------------|--------------------|----|--------------|

| [27]      | 3 | 6 | 2 | 2 | 3           | $DV_{dc}$          | ×  | ✓            |

|           |   |   |   |   |             | $\overline{(1-D)}$ |    |              |

| [28]      | 7 | 0 | 2 | 1 | 5           | $2V_{dc}$          | ×  | ×            |

| [29]      | 6 | 3 | 2 | 1 | 3           | $DV_{dc}$          | ×  | $\checkmark$ |

|           |   |   |   |   |             | $\overline{(1-D)}$ |    |              |

| Proposed  | 7 | 0 | 2 | 1 | 5           | $2MV_{dc}$         | ✓  | ✓            |

| 5-level   |   |   |   |   |             | $\overline{(1-D)}$ |    |              |

|           |   |   |   |   |             | <del></del>        |    |              |

<sup>\*</sup>S: Switching number, D: Diodes number, C: Capacitors number, L: Inductors number, N<sub>Level</sub>: Number of voltage levels, Gain: Boost gain, CC: Continuous input current, CG: Common ground, and M: Modulation index

Figure 4. The output voltage waveforms are as follows: (a) D = 80%, M = 1 output voltage waveform, (b) duty-cycle charging from D = 80% to D = 20, and (c) modulation index changing from M = 0 to M = 1

Figure 5. Voltage waveforms of the virtual DC source capacitors: (a) VC1 and (b) VC2

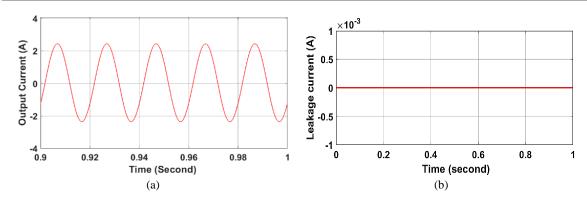

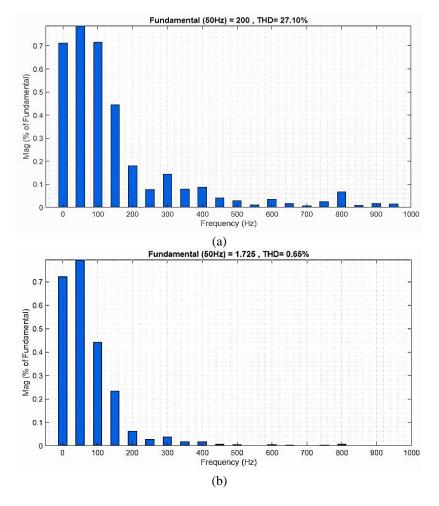

Figure 6(a) illustrates the absence of leakage current across the parasitic capacitance of the input source. Furthermore, Figure 6(b) depicts the waveform of the inverter's output current, characterized by the attributes previously delineated in Table 4. Additionally, Figures 7(a) and 7(b) disclose that the output voltage and current of the inverter exhibit total harmonic distortion (THD) values of 27.10% and 0.65%, respectively.

Figure 6. The output current waveform, (a) zoomed output current waveform and (b) leakage current waveform

Figure 7. Frequency spectrum and THD of the inverter, (a) output sinusoidal waveform and (b) output current

## 4.1. Comparative and losses analysis

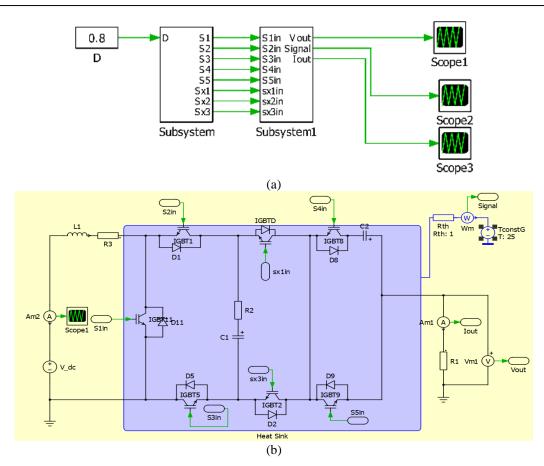

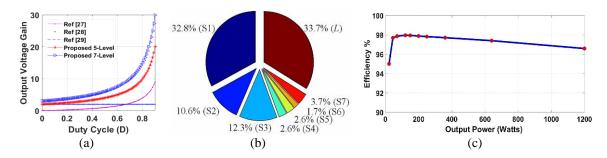

The next sections provide a comparative comparison of the suggested five-level inverter and other innovative topologies. Table 5 indicates the suggested inverter has a high voltage gain and a constant input current, which makes it especially appropriate for photovoltaics. Figures 8(a) and 8(b) also show the simulated converter. Additionally, Figure 9(a) shows the comparative study of voltage gain. Additionally, the efficiency curve of the converter and the percentage distribution of losses among the inverter's components are shown, while variable the output power from 0 to 1500 Watts with real conditions conferring to the values in Table 6 that are shown in Figures 9(b) and 9(c), correspondingly.

680 □ ISSN: 2088-8694

Figure 8. The modeled converter with PLECS software: (a) control system and (b) proposed converter

Figure 9. Comparison of an assessment of the proposed inverter's voltage gain and loss: (a) output voltage gains about the D, (b) loss of each component, and (c) efficiency curve

Table 6. Components and factors applied to calculate losses and efficiency

| Parameter      | Value                               | Parameter  | Value |

|----------------|-------------------------------------|------------|-------|

| Power switches | IGBT-FGH60N60SMD                    | $V_{(dc)}$ | 24 V  |

| $L_{(in)}$     | $3mH (10m\Omega internal resistor)$ | D          | 80%   |

# 5. CONCLUSION

This paper proposes a new five-level step-up common ground inverter with a reduced number of power switches specifically developed for photovoltaic and other renewable energy systems. The proposed inverter demonstrates the capability to attain elevated output voltages utilizing a single-source inverter configuration. Owing to the shared ground connection between the direct current (DC) input and the alternating current (AC) output, this inverter has effectively mitigated the issue of leakage current. The various switching methodologies corresponding to every output voltage level have been elucidated, yielding benefits such as

enhanced voltage balance out among capacitors and straightforward duty-cycle regulation. The architectural design of the inverter achieves a doubling of the boost gain (2D/1–D) within a five-level configuration. A comprehensive analysis of the inverter and a comparative evaluation of its performance relative to other contemporary topologies are provided. Ultimately, simulation outcomes obtained through the MATLAB/Simulink environment are presented to validate the inverter's efficiency.

#### REFERENCES

- [1] M. P. Kazmierkowski, "Grid Converters and Power Electronics (review of "Grid Converters for Photovoltaic and Wind Power Systems: Teodorescu, R., et al.; 2011) [Book News]," *IEEE Industrial Electronics Magazine*, vol. 5, no. 2, pp. 54–54, Jun. 2011, doi: 10.1109/MIE.2011.941116.

- [2] E. Gubía, P. Sanchis, A. Ursúa, J. López, and L. Marroyo, "Ground currents in single-phase transformerless photovoltaic systems," Progress in Photovoltaics: Research and Applications, vol. 15, no. 7, pp. 629–650, 2007, doi: 10.1002/pip.761.

- [3] Y. Yang and F. Blaabjerg, "Overview of Single-phase Grid-connected Photovoltaic Systems," *Electric Power Components and Systems*, vol. 43, no. 12, pp. 1352–1363, Jul. 2015, doi: 10.1080/15325008.2015.1031296.

- [4] M. Y. A. Khan, H. Liu, Z. Yang, and X. Yuan, "A comprehensive review on grid connected photovoltaic inverters, their modulation techniques, and control strategies," *Energies*, vol. 13, no. 6, 2020, doi: 10.3390/en13164185.

- [5] X. Guo and X. Jia, "Hardware-Based Cascaded Topology and Modulation Strategy with Leakage Current Reduction for Transformerless PV Systems," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 12, pp. 7823–7832, 2016, doi: 10.1109/TIE.2016.2607163.

- [6] H. Li, Y. Zeng, B. Zhang, T. Q. Zheng, R. Hao, and Z. Yang, "An Improved H5 Topology with Low Common-Mode Current for Transformerless PV Grid-Connected Inverter," *IEEE Transactions on Power Electronics*, vol. 34, no. 2, pp. 1254–1265, 2019, doi: 10.1109/TPEL.2018.2833144.

- [7] N. Vazquez, M. Rosas, C. Hernandez, E. Vazquez, and F. J. Perez-Pinal, "A new common-mode transformerless photovoltaic inverter," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 10, pp. 6381–6391, 2015, doi: 10.1109/TIE.2015.2426146.

- [8] M. Samizadeh, X. Yang, B. Karami, W. Chen, F. Blaabjerg, and M. Kamranian, "A new topology of switched-capacitor multilevel inverter with eliminating leakage current," *IEEE Access*, vol. 8, pp. 76951–76965, 2020, doi: 10.1109/ACCESS.2020.2983654.

- [9] S. Ravi, M. Premkumar, and L. Abualigah, "Comparative analysis of recent metaheuristic algorithms for maximum power point tracking of solar photovoltaic systems under partial shading conditions," *International Journal of Applied Power Engineering*, vol. 12, no. 2, pp. 196–217, 2023, doi: 10.11591/ijape.v12.i2.pp196-217.

- [10] M. G. Yahya and M. G. Yahya, "Modified PDPWM control with MPPT algorithm for equal power sharing in cascaded multilevel inverter for standalone PV system under partial shading," *International Journal of Power Electronics and Drive Systems*, vol. 14, no. 1, pp. 533–545, 2023, doi: 10.11591/ijpeds.v14.i1.pp533-545.

- [11] Z. M. Abed, T. K. Hassan, and K. R. Hameed, "Analysis and design of photovoltaic three-phase grid-connected inverter using passivity-based control," *International Journal of Power Electronics and Drive Systems*, vol. 13, no. 1, pp. 167–177, 2022, doi: 10.11591/ijpeds.v13.i1.pp167-177.

- [12] T. K. Hassan, "Reduction of single DC bus capacitance in photovoltaic cascaded multilevel converter," *International Journal of Power Electronics and Drive Systems*, vol. 11, no. 3, pp. 1660–1674, 2020, doi: 10.11591/ijpeds.v11.i3.pp1660-1674.

- [13] M. Shahabadini and H. Iman-Eini, "Leakage Current Suppression in Multilevel Cascaded H-Bridge Based Photovoltaic Inverters," IEEE Transactions on Power Electronics, vol. 36, no. 12, pp. 13754–13762, 2021, doi: 10.1109/TPEL.2021.3084699.

- [14] Y. P. Siwakoti, A. Palanisamy, A. Mahajan, S. Liese, T. Long, and F. Blaabjerg, "Analysis and design of a novel six-switch five-level active boost neutral point clamped inverter," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 12, pp. 10485–10496, 2020, doi: 10.1109/TIE.2019.2957712.

- [15] Y. P. Siwakoti, "A new six-switch five-level boost-active neutral point clamped (5L-Boost-ANPC) inverter," Conference Proceedings - IEEE Applied Power Electronics Conference and Exposition - APEC, vol. 2018-March, pp. 2424–2430, 2018, doi: 10.1109/APEC.2018.8341356.

- [16] D. H. Al-Mamoori, N. A. Azli, S. M. Ayob, and A. A. Albakry, "A multilevel boost inverter with removed leakage current and a reduced number of elements for photovoltaic applications," *International Journal of Power Electronics and Drive Systems*, vol. 15, no. 1, pp. 312–322, 2024, doi: 10.11591/ijpeds.v15.i1.pp312-322.

- [17] Y. P. Siwakoti, A. Mahajan, D. J. Rogers, and F. Blaabjerg, "A novel seven-level active neutral-point-clamped converter with reduced active switching devices and DC-link voltage," *IEEE Transactions on Power Electronics*, vol. 34, no. 11, pp. 10492–10508, 2019, doi: 10.1109/TPEL.2019.2897061.

- [18] S. Chinnamuthu, V. Balan, K. Vaidyanathan, V. Chinnaiyan, and P. Santhanamari, "Analysis of single-phase cascaded H-bridge multilevel inverters under variable power conditions," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 30, no. 3, pp. 1381–1388, 2023, doi: 10.11591/ijeecs.v30.i3.pp1381-1388.

- [19] N. S. S. Akshath, A. Naresh, M. N. Kumar, M. Barman, D. Nandan, and T. Abhilash, "Analysis and simulation of even-level quasi-Z-source inverter," *International Journal of Electrical and Computer Engineering*, vol. 12, no. 4, pp. 3477–3484, 2022, doi: 10.11591/ijece.v12i4.pp3477-3484.

- [20] D. Sankar and C. A. Babu, "Design and analysis of a novel quasi Z source based asymmetric multilevel inverter for PV applications," *International Journal of Power Electronics and Drive Systems*, vol. 11, no. 3, pp. 1368–1378, 2020, doi: 10.11591/ijpeds.v11.i3.pp1368-1378.

- [21] A. Chemseddine, N. Benabadji, A. Cheknane, and S. E. Mankour, "A comparison of single phase standalone square waveform solar inverter topologies: Half bridge and full bridge," *International Journal of Electrical and Computer Engineering*, vol. 10, no. 4, pp. 3384–3392, 2020, doi: 10.11591/ijece.v10i4.pp3384-3392.

- [22] B. E. Elnaghi, M. E. Dessouki, M. N. Abd-Alwahab, and E. E. Elkholy, "Development and implementation of two-stage boost converter for single-phase inverter without transformer for PV systems," *International Journal of Electrical and Computer Engineering*, vol. 10, no. 1, pp. 660–669, 2020, doi: 10.11591/ijece.v10i1.pp660-669.

- [23] S. S. Lee, Y. Yang, and Y. P. Siwakoti, "A Novel Single-Stage Five-Level Common-Ground-Boost-Type Active Neutral-Point-Clamped (5L-CGBT-ANPC) Inverter," *IEEE Transactions on Power Electronics*, vol. 36, no. 6, pp. 6192–6196, 2021, doi: 10.1109/TPEL.2020.3037720.

- [24] K. Jena, C. K. Panigrahi, and K. K. Gupta, "A Single-Phase Step-Up 5-level Switched-Capacitor Inverter with Reduced Device Count," ICPEE 2021 - 2021 1st International Conference on Power Electronics and Energy, 2021, doi: 10.1109/ICPEE50452.2021.9358556.

682 □ ISSN: 2088-8694

[25] A. Pourfaraj, M. Monfared, and H. Heydari-Doostabad, "Single-Phase Dual-Mode Interleaved Multilevel Inverter for PV Applications," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 4, pp. 2905–2915, 2020, doi: 10.1109/TIE.2019.2910041.

- [26] S. Kakar et al., "A Common-Ground-Type Five-Level Inverter with Dynamic Voltage Boost," Electronics (Switzerland), vol. 11, no. 24, 2022, doi: 10.3390/electronics11244174.

- [27] H. Heydari-Doostabad, M. Pourmahdi, M. Jafarian, A. Keane, and T. O'donnell, "Three-Switch Common Ground Step-Down and Step-Up Single-Stage Grid-Connected PV Inverter," *IEEE Transactions on Power Electronics*, vol. 37, no. 7, pp. 7577–7589, 2022, doi: 10.1109/TPEL.2022.3145193.

- [28] V. Anand, V. Singh, and J. S. Mohamed Ali, "Dual Boost Five-Level Switched-Capacitor Inverter With Common Ground," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 70, no. 2, pp. 556–560, 2023, doi: 10.1109/TCSII.2022.3169009.

- [29] L. Wang and M. Shan, "A Novel Single-Stage Common-Ground Zeta-Based Inverter With Nonelectrolytic Capacitor," IEEE Transactions on Power Electronics, vol. 37, no. 9, pp. 11319–11331, 2022, doi: 10.1109/TPEL.2022.3167450.

#### **BIOGRAPHIES OF AUTHORS**

Dalya Hamzah Al-Mamoori D S S S is a lecturer at Department of Electrical Power Engineering, Technical College Al-Mussaib, Al-Furat Al- Awsat Technical University. She received a B.Sc. degree in Electrical Power Engineering from Technical College Al-Mussaib, Al-Furat Al-Awsat Technical University, and an M.Sc. degree in Electrical Power Engineering from the University Tenaga Nasional, Malaysia. She is currently a Ph.D. Student at School of Electrical Engineering, Faculty of Engineering, Universiti Teknologi Malaysia, Johor Bahru 81310, Malaysia. Her research interests are power electronics, renewable energy and multilevel inverter. She can be contacted at email: dalyahamzahmussa@graduate.utm.my or daliahamza784@atu.edu.iq.

degree in Power Systems and Drives from AMU, and a PhD in Power Engineering from Universiti Teknologi Malaysia, Malaysia. During his PhD, his research primarily focused on developing novel circuit designs for MLI, and he received recognition for his work from the Ministry of Higher Education, Malaysia. In his early career, Dr Saad got two projects, one from the state government and the other from the central government funding agency. His research is focused on developing novel circuit designs for MLI in power electronic systems and efficiency improvement of solar PV systems to improve the overall performance of power systems and integrated renewable energy systems. He contributed to the field of power electronics and renewable energy systems through his research, publications, and professional services. He has received several awards and honors from national and international bodies. As a faculty member of Aligarh Muslim University, Dr. Saad continues to conduct cutting-edge research in the field of power electronics and renewable energy systems. He also mentors numerous graduate students and actively engages in professional societies such as IEEE. He is dedicated to continuing his research and contributing to the academic community at Aligarh Muslim University. He can be contacted at email: saad.ee@amu.ac.in.