# Design and analysis of seven-level hybrid modified H-bridge multilevel inverter

Arpan Dwivedi<sup>1</sup>, Raman Kumar<sup>2</sup>, Sailesh Sourabh<sup>2</sup>, Vikash Rajak<sup>2</sup>, Vikash Kumar Singh<sup>2</sup>, Maruti Nandan Mishra<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, Mittal Institute of Technology, Bhopal (M.P.), India <sup>2</sup>Department of Science, Technology, and Technical Education, Government of Bihar, Sershah Engineering College, Sasaram, India

#### **Article Info**

## Article history:

Received Sep 5, 2024 Revised May 19, 2025 Accepted Jun 3, 2025

## Keywords:

Boosting multilevel inverter PSIM Switch count Switching topology Voltage stress

#### **ABSTRACT**

This paper introduces a novel boosting multilevel inverter that utilizes switched capacitors. Current multilevel inverters (MLIs) face several issues, such as complex structures, intricate switching controls, and challenges in generating gate pulses, numerous components, and high voltage stress on semiconductors. The increase in the number of levels adds to the complexity and cost of the circuit and can reduce reliability in some cases. The proposed topology creates a 7-level voltage waveform using 9 switches, 1 diode, and 2 capacitors, and it triples the voltage gain. The capacitors maintain selfbalanced operation without the need for additional circuits. A simple logic gate-based pulse-width modulation (PWM) technique is presented to ensure power balancing of the capacitors. The proposed 7-level switched capacitor boosting multilevel inverter features a reduced switch count, lower voltage stress, and built-in fault tolerance. The paper includes a comprehensive comparison of various related topologies. The proposed topology is simulated in PSIM, with simulation results presented for different parameters.

This is an open access article under the CC BY-SA license.

1731

## Corresponding Author:

Arpan Dwivedi

Department of Electrical Engineering, Mittal Institute of Technology

Bhopal (M.P.), India

Email: arpandwvd@gmail.com

#### 1. INTRODUCTION

In industrial applications, DC-AC power converter systems are favored for their nearly sinusoidal output voltage and high-power handling capacity. Traditional three-level inverters, however, necessitate a large output filter and a high DC link voltage [1], [2]. To enhance power quality and efficiency, there is a need for inverters with a greater number of output voltage levels [3], [4]. In smart grids or microgrids, multilevel inverters can be seamlessly integrated with renewable energy sources like photovoltaic (PV) cells. Leading electric vehicle manufacturers have recently adopted higher-voltage batteries to achieve faster charging times, increased power density, and reduced current consumption [5], [6]. As the trend in electric vehicles shifts toward higher DC-link voltages, certain multilevel inverter architectures are being considered as practical and effective alternatives to two-level inverters [7]. Multilevel inverters offer several advantages, including higher efficiency, greater power density, improved waveform quality, and inherent fault-tolerance [8], [9].

Multilevel inverters (MLIs) have emerged as the most advanced power conversion technology for various applications, such as electric motor drives, flexible AC transmission systems (FACTS), and renewable energy resources (RERs) [10], [11]. The popularity of MLIs in medium- to high-power operations is due to their numerous benefits, including low harmonic content, reduced power consumption through power electronic switches, and significantly decreased electromagnetic interference (EMI) at the receiving end.

Journal homepage: http://ijpeds.iaescore.com

Through the above discussion, it is clear that the main limitations of the recently proposed 7-level SCMLIs include a higher component count, increased total standing voltage, higher maximum blocking voltage, and a lower boosting factor. The novel 7-level SCMLI presented in this brief has the following key features:

- The proposed 7-level MLI uses only one DC source;

- The switch and capacitor counts are significantly reduced in this 7-level MLI;

- In the absence of a closed loop, the capacitors self-balance;

- Four switches operate at the fundamental frequency, and about 50% of the switches conduct for each voltage level production, resulting in minimal net power loss;

- Compared to previous MLIs, the output voltage of the proposed MLI is boosted to three times the input voltage; and

- The designed MLI can handle both high and low power factor (PF) loads.

#### 2. PROPOSED METHODOLOGY

#### 2.1. Switching topology seven-level mli topology

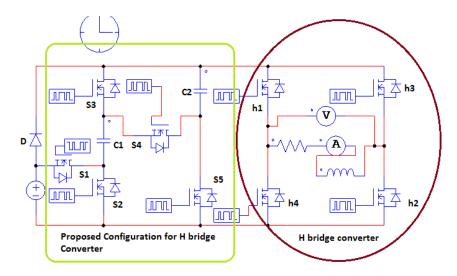

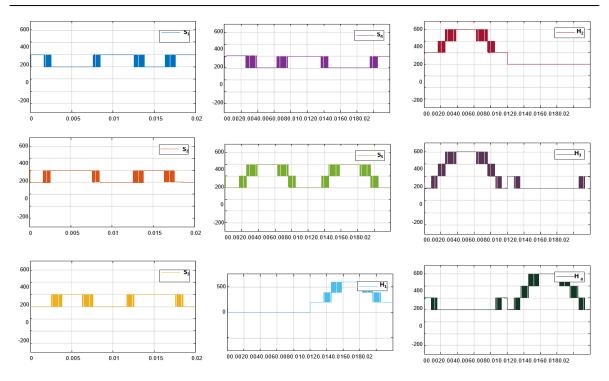

Figure 1 illustrates the simplified structure of the planned seven-level architecture. It consists of nine switches (S1, S2, S3, S4, S5, S6, H1, H2, H3, H4), two capacitors (C1, C2), one diode (D1), and one voltage source (Vdc) to create a 7-level output voltage ( $V_0$ ). The SPWM (switch pulse width modulation) technique is used to generate the switching pulses and the required output voltage.

The final voltage is generated during both the positive and negative half cycles using an H-bridge. Vdc can directly charge each of the capacitors connected to the proposed inverter. Table I describes the different scenarios for each level and their effects on the capacitor's state. It shows that to create an output voltage of 3 Vdc, switches S1, S4, H1, and H4 are turned "on," while switches S2, S3, S5, H2, and H3 are turned "off." In the table, "on" is represented by 1, "off" by 0, "discharging" by "D," "charging" by "C," and "not connected" by "NC." The switch statuses listed in Table 1 determine all the voltage levels.

Figure 1. PSIM simulation of a seven-level hybrid modified H-bridge multilevel inverter

| Table 1. The planned 7-level MLI topology's switching state |                                        |       |       |       |       |       |       |       |       |       |       |                           |  |  |

|-------------------------------------------------------------|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------------|--|--|

|                                                             | Switching states Diodes and capacitors |       |       |       |       |       |       |       |       |       |       |                           |  |  |

| $s_1$                                                       | $S_2$                                  | $S_3$ | $S_4$ | $S_5$ | $H_1$ | $H_2$ | $H_3$ | $H_4$ | $D_1$ | $C_1$ | $C_2$ | $V_O$                     |  |  |

| 1                                                           | 0                                      | 0     | 1     | 0     | 1     | 0     | 0     | 1     | 0     | D     | D     | $3 V_{dc}$                |  |  |

| 1                                                           | 0                                      | 1     | 0     | 0     | 1     | 0     | 0     | 1     | 0     | D     | NC    | $2 V_{dc}$                |  |  |

| 0                                                           | 1                                      | 1     | 0     | 1     | 1     | 0     | 0     | 1     | 1     | C     | C     | $V_{dc}$                  |  |  |

| 0                                                           | 1                                      | 1     | 0     | 1     | 1     | 0     | 1     | 0     | 1     | C     | C     | 0                         |  |  |

| 0                                                           | 1                                      | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 1     | C     | C     | 0                         |  |  |

| 0                                                           | 1                                      | 1     | 0     | 1     | 0     | 1     | 1     | 0     | 1     | C     | C     | $-V_{dc}$                 |  |  |

| 0                                                           | 0                                      | 0     | 1     | 0     | 0     | 1     | 1     | 0     | 1     | NC    | D     | -2 $V_{dc}$               |  |  |

| 1                                                           | 0                                      | 0     | 1     | 0     | 0     | 1     | 1     | 0     | 0     | D     | D     | -3 <i>V</i> <sub>dc</sub> |  |  |

#### 2.2. Operational modes

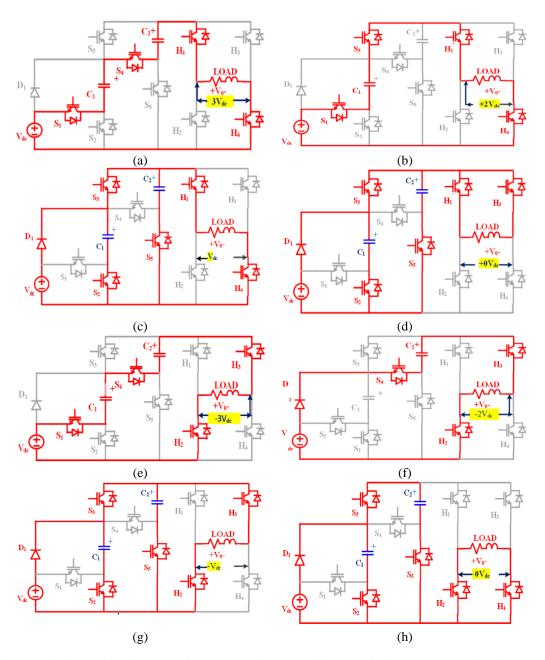

This subsection presents the governing principle of the proposed SCMLI. Figures 2(a)-2(d) (see in appendix) illustrate the circuits for the voltage levels +0Vdc, +1Vdc, +2Vdc, and +3Vdc with positive charging current pathways and a load current i0 > 0. Table 1 shows the switching parameters for achieving various positive and negative voltage levels. Here, "1" and "0" denote the "on" and "off" states of a switch and a diode, respectively, while "D," "C," and "NC" denote the "discharging," "charging," and "not-connected" states of the capacitor. The following is a description of how different voltage levels are generated:

#### i) State 3 Vdc

The load voltage is realized at 3Vdc by combining the voltage of C1 and C2 with Vdc. In this mode, both capacitors C1 and C2 are discharging, and switches S1 and S2 are on. If switches H1 and H3 are on, the voltage across the load is +3 Vdc presented in Figure 2(a). When switches H2 and H4 are on, the voltage across the load is -3 Vdc, as shown in Figure 2(e).

#### ii) State 2 Vdc

Vdc and C1 are connected in series. Switches S1, S3, H1, and H4 are turned on to provide a voltage level of +2Vdc across the load, as shown in Figure 2(b). In this mode, capacitor C1 is discharging, and capacitor C2 is not connected. To create -2Vdc, Vdc, and C2 are connected in series, and the appropriate switches are activated. Switches S4, H2, and H3 are turned on, and diode D1 becomes forward biased to provide a voltage level of -2Vdc across the load, as shown in Figure 2 (f). At this voltage level, capacitor C2 is discharging, and capacitor C1 is not connected.

## iii) State Vdc

This voltage can be achieved by directly placing Vdc across the load or by using the capacitor voltages across C1 or C2. For creating +Vdc across the load, switches S2, S3, S5, H1, and H4 are turned on, and diode D1 becomes forward biased, with capacitors C1 and C2 charging, as shown in Figure 2(C). To create -Vdc, switches S2, S3, S5, H2, and H3 are turned on, and diode D1 becomes forward biased, with capacitors C1 and C2 also charging, as shown in Figure 2(g).

#### iv) State 0 Vdc

When either H1 and H3 or H2 and H4 are switched on, the 0Vdc voltage level is observed across the load terminals, as described in Figures 2(d) and 2(h). To charge capacitors C1 and C2, switches S2, S3, and S5 are turned on, and diode D1 becomes forward-biased.

## 3. METHODS

## 3.1. Mathematical calculations

In this section, the voltage across the switches S1, S2, S3, S4, S5, H1, H2, H3, and H4 is calculated as described below, leading to the calculation of TSV. The voltage stress across various switches is illustrated in Figure 3. The (1) determines the MBV of switches S1, S2, S3, and S4, while (2) provides the MBV of switch S5, and in (3) gives the MBV of switches H1, H2, H3, and H4. Thus, TSV is determined using (3), and the diode's PIV is provided by (4).

MBV for switches S1, S2, S3, and S4 is calculated as Vdc, as shown in (1). For switch S5, the MBV is 2 Vdc, according to (2), while for switches H1, H2, H3, and H4, the MBV is 3 Vdc, as per (3). Consequently, TSV is set at 18 Vdc, as per (4), and the diode's PIV is represented by Vdc in (5).

$$MBV(S_1,S_2,S_3,S_4)=V_{dc}$$

(1)

$$MBV(S_5)=2V_{dc}$$

(2)

$$MBV(H_1,H_2,H_3,H_4)=3V_{dc}$$

(3)

$$TSV=18 V_{dc}$$

(4)

$$PIV_{diode} = V_{dc}$$

(5)

TSV plays a crucial role in high-voltage conditions. The per-unit (pu) values of TSV and MBV for the intended topology are defined as shown in (6) and (7), respectively:

Per unit MBV (pu) = MBV/peak output voltage

$$(7)$$

Figure 3. Voltage stress across the switches ( $S_1$  to  $H_4$ )

#### 3.2. Logic gate-based PWM

Various types of continuous pulse width modulation (CPWM) techniques employed in this context encompass SPWM and SVPWM [12], [13]. In CPWM methods, continuous switching occurs due to the consistent intersection of carrier and reference signals within the carrier band boundaries, where the reference signal is maintained. Conversely, in discontinuous pulse width modulation (DPWM), switching ceases during this period as the reference signal is clamped at the maximum positive or negative value within the carrier band [14]-[16]. In carrier-based space vector pulse width modulation (SVPWM) and DPWM systems, it's essential to obtain a zero-sequence signal and integrate it with the reference signal to generate a modulating signal [17]-[19]. One of the advantages of SPWM technology lies in its uniform switching frequency [20], [21]. Maintaining a constant switching frequency simplifies the thermal design of switching components since component losses can be accurately calculated [22], [23]. This rationale underscores the planned adoption of SPWM technology in the proposed topology [24], [25].

## 4. RESULT AND DISCUSSION

A comprehensive PSIM model is proposed for the suggested architecture to develop a 7-level inverter, aimed at verifying the conceptual viability of the intended inverter. This model employs four IGBTs arranged in an H-bridge configuration to emulate the functionality of the 7-level 9-switch inverter, generating both positive and negative voltages akin to a single-phase inverter. A resistive load is incorporated, with the source voltage set to  $200\ V$ .

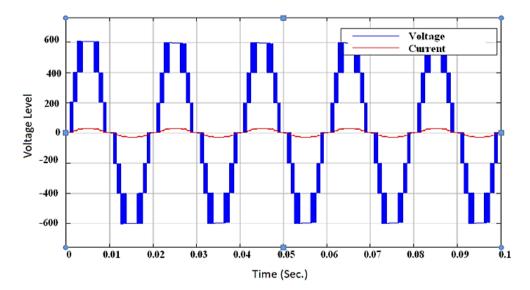

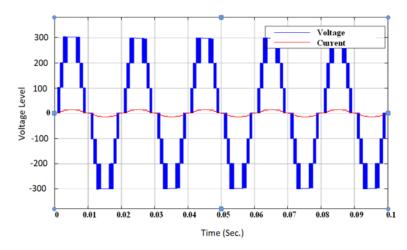

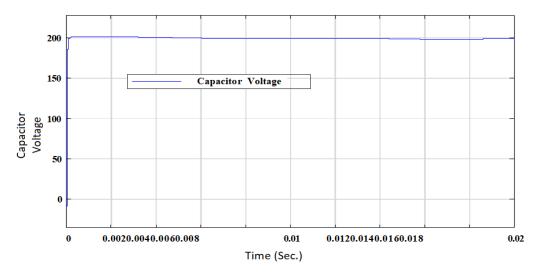

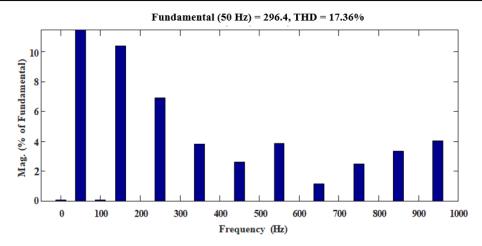

In Figure 4, a simulation waveform is depicted for a supply voltage (Vdc) of 200 V and a resistive load (R) of 300  $\Omega$ . Additionally, an inductor with a value of L = 100 mH is introduced. In Figure 5, a simulation waveform is depicted for a supply voltage (Vdc) of 100 V and a resistive load (R) of 300  $\Omega$ . Additionally, an inductor with a value of L=200mH is introduced. The simulation waveform is presented, illustrating the output boosted to three times the input voltage without any closed-loop control. Furthermore, Figures 4 and 5 showcase a simulation waveform demonstrating the output voltage and load current with a modulation index of 0.51. Figure 6, the charging voltage across capacitors C1 and C2. It's observed that the final steady-state voltages across C1 and C2 are measured at 200 V. The FFT analysis shows that the THD across the load is 17.36 % of the fundamental frequency, and the voltage is observed as 296.4, as shown in Figure 7.

Figure 4. Voltage and current waveform of the proposed converter (Vdc = 200, R = 300, L = 100 mh)

Figure 5. Voltage and current waveform of the proposed converter (Vdc = 100, R = 300, L = 200 mh)

Figure 6. Voltage across the capacitor

Figure 7. THD of the voltage across the load

#### 4 CONCLUSION

This article introduces a proposed topology featuring seven levels in its Simulation model. The suggested converter boasts a boosting factor of 3 and is capable of generating seven distinct levels of output. Detailed discussions are provided on the suggested inverter's circuit configuration, operational concept, and voltage stress analysis, including a thorough examination of the capacitor selection process. An analysis comparing the performance of similar inverters reveals that the suggested inverter achieves the same range of output voltage values using fewer switches and drivers, rendering it a more cost-effective option. Voltage balancing is autonomously managed by capacitors C1 and C2. The feasibility and performance of the Simulation model are extensively evaluated. Switches are controlled via SPWM, with the switching sequence primarily focused on balancing capacitor charging/discharging and the capacitors themselves. Additionally, the total harmonic distortion (THD) of the recommended converter is scrutinized.

#### **FUNDING INFORMATION**

The authors declare that no funds, grants, or other financial support were received during the preparation of this manuscript.

## AUTHOR CONTRIBUTIONS STATEMENT

This journal uses the Contributor Roles Taxonomy (CRediT) to recognize individual author contributions, reduce authorship disputes, and facilitate collaboration.

| Name of Author       | C            | M            | So | Va           | Fo | I            | R | D            | 0            | E            | Vi | Su           | P | Fu |

|----------------------|--------------|--------------|----|--------------|----|--------------|---|--------------|--------------|--------------|----|--------------|---|----|

| Arpan Dwivedi        | ✓            | ✓            | ✓  | ✓            | ✓  | ✓            |   | ✓            | ✓            | ✓            | ✓  |              |   |    |

| Raman Kumar          |              | $\checkmark$ |    |              |    | $\checkmark$ |   | $\checkmark$ | $\checkmark$ |              | ✓  | $\checkmark$ |   |    |

| Sailesh Sourabh      | $\checkmark$ |              | ✓  | $\checkmark$ |    |              | ✓ |              | $\checkmark$ |              | ✓  |              |   |    |

| Vikash Rajak         |              |              |    |              |    | $\checkmark$ |   |              |              | $\checkmark$ |    |              |   |    |

| Vikash Kumar Singh   |              |              |    |              | ✓  |              | ✓ |              |              | $\checkmark$ |    | $\checkmark$ |   |    |

| Maruti Nandan Mishra |              | ✓            |    |              |    |              |   | $\checkmark$ | ✓            | $\checkmark$ |    |              |   |    |

E : Writing - Review & Editing

CONFLICT OF INTEREST STATEMENT

Fo: Formal analysis

Authors state no conflict of interest.

П

#### DATA AVAILABILITY

Data availability is not applicable to this paper as no new data were created or analyzed in this study.

#### REFRENCES

- A. Dwivedi and Y. Pahariya, "Design and Analysis of Hybrid Multilevel Inverter for Asymmetrical Input Voltages," Journal of Electrical Engineering & Technology, vol. 16, no. 6, pp. 3025-3036, Nov. 2021, doi: 10.1007/s42835-021-00814-5.

- H. Luo, Y. Dong, W. Li, and X. He, "Module Multilevel-Clamped Composited Multilevel Converter (M-MC 2) with Dual T-Type Modules and One Diode Module," Journal of Power Electronics, vol. 14, no. 6, pp. 1189-1196, Nov. 2014, doi: 10.6113/JPE.2014.14.6.1189.

- J. Rodriguez, Jih-Sheng Lai, and Fang Zheng Peng, "Multilevel inverters: a survey of topologies, controls, and applications,"

- IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp. 724–738, Aug. 2002, doi: 10.1109/TIE.2002.801052.

L. Franquelo, J. Rodriguez, J. Leon, S. Kouro, R. Portillo, and M. Prats, "The age of multilevel converters arrives," IEEE Industrial Electronics Magazine, vol. 2, no. 2, pp. 28-39, Jun. 2008, doi: 10.1109/MIE.2008.923519.

- J. Rodriguez et al., "Multilevel Converters: An Enabling Technology for High-Power Applications," Proceedings of the IEEE, vol. 97, no. 11, pp. 1786-1817, Nov. 2009, doi: 10.1109/JPROC.2009.2030235.

- S. De, D. Banerjee, K. Siva kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," IET Power Electronics, vol. 4, no. 4, pp. 384-392, Apr. 2011, doi: 10.1049/iet-pel.2010.0027.

- K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel Inverter Topologies With Reduced Device Count: A Review," IEEE Transactions on Power Electronics, vol. 31, no. 1, pp. 135–151, Jan. 2016, doi: 10.1109/TPEL.2015.2405012.

- S. P. Gautam, L. Kumar, and S. Gupta, "Hybrid topology of symmetrical multilevel inverter using less number of devices," IET Power Electronics, vol. 8, no. 11, pp. 2125–2135, Nov. 2015, doi: 10.1049/iet-pel.2015.0037.

- K. K. Gupta and S. Jain, "A Novel Multilevel Inverter Based on Switched DC Sources," IEEE Transactions on Industrial Electronics, vol. 61, no. 7, pp. 3269-3278, Jul. 2014, doi: 10.1109/TIE.2013.2282606.

- [10] E. Babaei, S. Laali, and Z. Bayat, "A Single-Phase Cascaded Multilevel Inverter Based on a New Basic Unit With Reduced Number of Power Switches," IEEE Transactions on Industrial Electronics, vol. 62, no. 2, pp. 922-929, Feb. 2015, doi: 10.1109/TIE.2014.2336601.

- A. K. Sadigh, V. Dargahi, and K. A. Corzine, "New Multilevel Converter Based on Cascade Connection of Double Flying Capacitor Multicell Converters and Its Improved Modulation Technique," IEEE Transactions on Power Electronics, vol. 30, no. 12, pp. 6568-6580, Dec. 2015, doi: 10.1109/TPEL.2014.2387066.

- M. R. J. Oskuee, M. Karimi, S. N. Ravadanegh, and G. B. Gharehpetian, "An Innovative Scheme of Symmetric Multilevel Voltage Source Inverter With Lower Number of Circuit Devices," IEEE Transactions on Industrial Electronics, vol. 62, no. 11, pp. 6965-6973, Nov. 2015, doi: 10.1109/TIE.2015.2438059.

- E. C. dos Santos, J. H. G. Muniz, E. R. C. da Silva, and C. B. Jacobina, "Nested Multilevel Topologies," IEEE Transactions on Power Electronics, vol. 30, no. 8, pp. 4058-4068, Aug. 2015, doi: 10.1109/TPEL.2014.2351392.

- [14] M. R. A and K. Sivakumar, "A Fault-Tolerant Single-Phase Five-Level Inverter for Grid-Independent PV Systems," IEEE

- Transactions on Industrial Electronics, vol. 62, no. 12, pp. 7569–7577, Dec. 2015, doi: 10.1109/TIE.2015.2455523.

Ui-Min Choi, Kyo-Beum Lee, and F. Blaabjerg, "Diagnosis and Tolerant Strategy of an Open-Switch Fault for T-Type Three-Level Inverter Systems," IEEE Transactions on Industry Applications, vol. 50, no. 1, pp. 495-508, Jan. 2014, doi: 10.1109/TIA.2013.2269531.

- S. K. Chattopadhyay and C. Chakraborty, "Performance of Three-Phase Asymmetric Cascaded Bridge (16:4:1) Multilevel Inverter," IEEE Transactions on Industrial Electronics, vol. 62, no. 10, pp. 5983-5992, Oct. 2015, doi:

- S. P. Gautam, L. Kumar, S. Gupta, and N. Agrawal, "A Single-Phase Five-Level Inverter Topology With Switch Fault-Tolerance Capabilities," IEEE Transactions on Industrial Electronics, vol. 64, no. 3, pp. 2004-2014, Mar. 2017, doi: 10.1109/TIE.2016.2626368.

- V. V. S. Pradeep Kumar and B. G. Fernandes, "A Fault-Tolerant Single-Phase Grid-Connected Inverter Topology With Enhanced Reliability for Solar PV Applications," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 3, pp. 1254–1262, Sep. 2017, doi: 10.1109/JESTPE.2017.2687126.

- V. Babenko, A. Danilov, D. Vasenin, and V. Krysanov, "Parametric optimization of the structure of controlled high-voltage capacitor batteries," Archives for Technical Sciences, vol. 1, no. 24, pp. 9-16, Jun. 2021, doi: 10.7251/afts.2021.1324.009B.

- [20] I. Z. Mukti, E. R. Khan, and K. K. Biswas, "1.8-V Low Power, High-Resolution, High-Speed Comparator With Low Offset Voltage Implemented in 45nm CMOS Technology," Journal of VLSI Circuits and Systems, vol. 6, no. 1, pp. 19-24, 2024, doi: 10.31838/jvcs/06.01.03.

- [21] P. A. Pandian, K. S. K. Sheik, A. R. Lakshmi, and G. Bs, "A low power efficient design of full adder using transmission gates," International Journal of communication and computer Technologies, vol. 5, no. 1, pp. 2-6, 2019, doi: 10.31838/ijccts/05.01.01.

- L. Virág, J. Kovács, and A. Edelmayer, "Interacting advanced ITS communications with low-power sensor networks," Journal of Wireless Mobile Networks, Ubiquitous Computing, and Dependable Applications, vol. 4, no. 3, pp. 79–96, 2013.

- G. Nur, B. N. Barış, B. Levent, B. S. Sazaklıoğlu, and E. Ak, "BUSER Transcutaneous Electric Nerve Stimulator Device Design," Natural and Engineering Sciences, vol. 8, no. 1, pp. 18–30, 2023, doi: 10.28978/nesciences.1278068.

- P. H. Thevenon et al., "iMRC: Integrated Monitoring & Recovery Component, a Solution to Guarantee the Security of Embedded Journal of Internet Services and Information Security, vol. 12, no. 2, pp. 70-94, 2022, doi: 10.22667/JISIS.2022.05.31.070.

- [25] J. Priyanka, M. Ramya, and M. Alagappan, "IoT Integrated Accelerometer Design and Simulation for Smart Helmets," Indian Journal of Information Sources and Services, vol. 13, no. 2, pp. 64-67, 2023, doi: 10.51983/ijiss-2023.13.2.3862.

## **APPENDIX**

Figure 2. Eight operational modes of the proposed SCMLI during one full cycle: (a) +3 Vdc, (b) +2 Vdc, (c) +Vdc, (d) 0 Vdc, (e) -3 Vdc, (f) -2 Vdc, (g) -Vdc, and (h) 0 Vdc (negative half-cycle)

# **BIOGRAPHIES OF AUTHORS**

**Dr. Arpan Dwivedi** and a master's degree in Technology in Energy Technology from the University Institute of Technology, RGPV Bhopal. He achieved his Ph.D. in Electrical Engineering from Sarvapalli Radhakrishnan University, Bhopal, in 2018. With over 17 years of teaching and 13 years of research experience, he specializes in power converters, renewable energy systems, hybridization of multiple energy sources, power systems, and energy systems. He holds a lifetime membership with ISTE. He has contributed significantly to research with more than 20 published papers in SCIE/Scopus/UGC indexed Journals and International and National Conferences. His expertise extends to the domain of energy storage systems for PV applications

and power converters, resulting in the successful filing of five patents. Additionally, he serves as an editor for esteemed SCIE/Scopus-indexed journals and conferences. Demonstrating his commitment to advancing knowledge, he has completed a research project funded by TEQIP with a grant of 1.6 lakh, serving as the Co-Principal Investigator. Furthermore, he has authored four books in various areas, showcasing his multidimensional contributions to academia and research. He can be contacted at email: arpandwvd@gmail.com.

Vikash Rajak © © currently works as an Assistant Professor in the Department of Electrical and Electronics Engineering, Sershah Engineering College, Sasaram, under the Department of Science, Technology, and Technical Education, Patna, India. He holds a bachelor's degree in Electrical and Electronics Engineering from BIT, Meshra, Ranchi, master's degree in Power System from VNIT Nagpur. His research interest includes power system and power electronics & drives. He can be contacted at email: vikasr5627@gmail.com.