# Performance analysis of a cascaded dual full bridges 5, 7, and 9 levels inverter: experimental validation

## Nabil Saidani, Rachid El Bachtiri, Abdelaziz Fri, Karima El Hammoumi

REEPER Group, Innovative Technology and Computing Laboratory, Higher School of Technology, Sidi Mohammed Ben Abdellah University (USMBA), Fez, Morocco

## **Article Info**

## Article history:

Received Jan 14, 2025 Revised Jul 31, 2025 Accepted Sep 2, 2025

## Keywords:

Grid connected Multilevel inverter Photovoltaic Selective harmonic elimination Total harmonic distortion

## **ABSTRACT**

Cascaded full-bridge inverter is a suitable topology for grid-connected applications due to its ability to generate an output voltage waveform that closely resembles a sine wave, resulting in lower total harmonic distortion (THD) factors. This article proposes the use of the selective harmonic elimination (SHE) technique to produce a 5-level voltage using a symmetrical inverter and 7 and 9-level voltage using an asymmetrical inverter composed of only two full bridges loaded by an RL circuit of 51.4  $\Omega$  and 200 mH. The study primarily focuses on analysing the impact of the number of levels on the power quality of the inverter. This includes investigating the effects of the fundamental magnitude on the produced power, as well as measuring losses in the inverter, power factor, THD factor, and fundamental magnitude for each level configuration. The study demonstrates that asymmetrical MLIs lower THD (10.9% vs. 16.7%) and increasing voltage levels enhance waveform quality but slightly reduce the fundamental voltage magnitude, impacting AC power output. The simulation analysis has been conducted using the PSIM environment, and the results have been validated through experimental measurements.

This is an open access article under the <u>CC BY-SA</u> license.

2464

## Corresponding Author:

Nabil Saidani

REEPER Group, Innovative Technology and Computing Laboratory, Higher School of Technology Sidi Mohammed Ben Abdellah University (USMBA)

Fez 30000, Morocco

Email: nabil.saidani@usmba.ac.ma

## 1. INTRODUCTION

Multilevel inverters (MLIs) are advanced DC-to-AC converters that generate output voltage waveforms with multiple discrete levels, significantly reducing harmonic distortion and enhancing power quality [1]-[5]. One of the most promising architectures is based on cascaded full-bridge modules, which offer scalability and modularity, enabling high-voltage, high-power applications with improved efficiency and lower THD [6]-[9]. Recent research has extensively explored various MLI topologies, control strategies, and optimization techniques, highlighting their technical advantages and potential for diverse industrial applications [10]-[12].

MLIs are generally classified into two categories: symmetrical and asymmetrical. In a symmetrical MLI, each cascaded full-bridge is supplied by an identical DC voltage source, ensuring uniform voltage steps and a straightforward design [13], [14]. However, this uniformity may limit the achievable number of voltage levels and flexibility in design. In contrast, asymmetrical MLIs utilize different DC voltage levels for each full-bridge module, which allows for the generation of additional voltage steps and can further improve the quality of the output waveform [15], [16]. This approach, while offering enhanced resolution and potentially lower THD, introduces additional complexity in terms of DC source management and control [17].

Journal homepage: http://ijpeds.iaescore.com

The control of a multilevel inverter can be achieved through various techniques, one of which is the selective harmonic elimination (SHE) method [18]-[20]. The SHE technique enables the elimination of lower-order harmonics that have significant amplitudes [21]-[23]. Its principle is based on using "n" switching angles to control the amplitude of the fundamental component and cancel out "n-1" harmonics [24], [25]. In our study, we will take advantage of these "n" switching angles to eliminate as many harmonics as possible and investigate how this influences the fundamental component and the overall power quality delivered by the inverter [26].

The main contribution of this work is the practical validation and performance analysis of both symmetrical and asymmetrical MLIs. We conduct a detailed comparative study by evaluating key performance metrics—including total harmonic distortion (THD), switching and conduction losses, and the relationship between AC power, the fundamental voltage magnitude, and power factor, across configurations with 5, 7, and 9 voltage levels. By combining simulation and experimental results, our study bridges the gap between theoretical research and practical implementation, providing valuable insights into the trade-offs and benefits of each MLI configuration for real-world applications.

#### 2. DESIGN AND DESCRIPTION

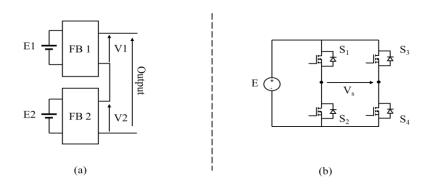

This study focuses on a multilevel inverter that consists of two full-bridge modules (FB1 and FB2) connected in series, as shown in Figure 1. Each full bridge is powered by its own DC voltage source, labelled E1 and E2. In this section, we explain how we determine the DC voltage values for each full bridge, and outline the process for finding the switching angles using the SHE technique to generate five-, seven-, and nine-level voltage waveforms.

Figure 1. Block diagram of the multilevel inverter: (a) cascaded full bridges and (b) circuit diagram of the full bridge

# 2.1. Determination of the DC source value of each configuration

- a. Design constraints

- Step voltage: Identical voltage steps between consecutive levels to ensure harmonic reduction.

- Maximum output voltage: Fixed at E<sub>max</sub>=31.1 V, scaled down by a factor of 10 from the nominal grid peak voltage (311 V for a 220 V<sub>RMS</sub> system).

For each case, we use a pair of equations derived from the level expressions.

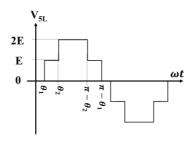

b. Symmetrical configuration (5-level): For the symmetrical case (E1=E2=E), the output voltage levels are -2E, -E, 0, E, 2E as shown in Figure 2. The DC source voltages are derived using (1).

$$\begin{cases}

E1 + E2 = E_{max} = 31.1V \\

E1 = \frac{E_{max}}{2} = 15.55V

\end{cases}

\Rightarrow E1 = E2 = 15,55V$$

(1)

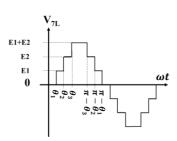

c. Asymmetrical configuration (7-level): For seven-level, an asymmetrical configuration (E2>E1) generates additional voltage levels: -E1-E2, -E2, -E1, 0, E1, E2, E1+E2 (Figure 3). The DC sources are determined by solving (2).

$$\begin{cases}

E1 + E2 = E_{max} = 31.1V \\

E1 = \frac{E_{max}}{3} = 10.3V

\end{cases}

\Rightarrow

\begin{cases}

E1 = 10.3V \\

E2 = 20.7V

\end{cases}$$

(2)

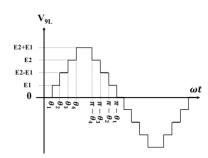

d. Asymmetrical configuration (9-Level): To achieve nine levels as shown in Figure 4(-E1-E2, -E2, E1-E2, -E1, 0, E1, E2-E1, E2, E1+E2). The DC sources are calculated using (3).

$$\begin{cases} E1 + E2 = E_{max} = 31.1V \\ E2 - E1 = \frac{E_{max}}{2} = 15.5V \end{cases} \implies \begin{cases} E1 = 7.7V \\ E2 = 23.3V \end{cases}$$

(3)

Figure 2. Five-level output voltage waveform

Figure 3. Seven-level output voltage waveform

Figure 4. Seven-level output voltage waveform

### 2.2. Determination of the switching angles

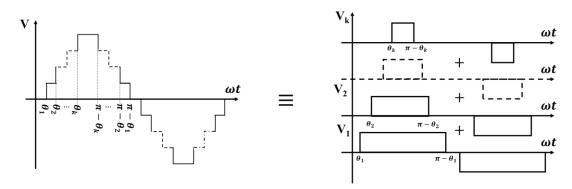

The selective harmonic elimination technique involves decomposing the output voltage waveform into a Fourier series and determining the appropriate switching angles to eliminate specific harmonics. The technique becomes more effective as the number of switching angles increases, enabling the elimination of a greater number of harmonics. The fourier series decomposition (FSD) of the inverter's output voltage can be derived by following the steps below. First, we consider that the output voltage waveform of the inverter is composed of a sum of distinct rectangular pulses, as illustrated in Figure 5.

Figure 5. Output voltage expressed as a sum of partial waveforms Vi

From this observation, the output voltage V (4) can be expressed as the sum of elementary voltage V<sub>i</sub>:

$$V = V_1 + V_2 + \dots + V_k \tag{4}$$

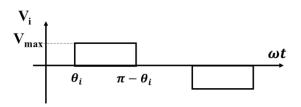

Each component  $V_i$  corresponds to a voltage segment (Figure 6) defined by a specific switching angle  $\theta_i$ , and each of them has odd symmetry. Therefore, their Fourier Series decomposition (5) contains only sine terms and can be written as (5):

$$V_i(t) = \sum_{n=1}^{+\infty} b_n^i \cdot \sin(n\omega_0 t)$$

(5)

where  $b_n^i$  are the Fourier coefficients for the *i*-th segment and are given by (6).

$$b_n^i = \frac{4}{2\pi} \int_{\theta_i}^{\pi - \theta_i} V_{max}. \sin(n\omega_0 t) . dt$$

(6)

The (7) represents the solution of (6).

$$b_n^i = \frac{2V_{max}}{n\pi} \left( \cos(n\theta_i) - \cos(n(\pi - \theta_i)) \right) \tag{7}$$

This means the total output voltage V(t) becomes (8).

$$V(t) = \sum_{i=1}^{k} V_i = \sum_{i=1}^{k} (\sum_{n=1}^{+\infty} b_n^i \cdot \sin(n\omega_0 t))$$

(8)

We can rearrange (8) to (9).

$$V(t) = \sum_{n=1}^{+\infty} \left(\sum_{i=1}^{k} b_n^i\right) \sin(n\omega_0 t) \tag{9}$$

Thus, the n-th harmonic component of the output voltage is given by (10) and (11).

$$V_n(t) = \left(\sum_{i=1}^k b_n^i\right) \sin(n\omega_0 t) \tag{10}$$

$$V_n(t) = \frac{2V_{max}}{n\pi} \cdot \left( \sum_{i=1}^k \left( \cos(n\theta_i) - \cos(n(\pi - \theta_i)) \right) \right) \sin(n\omega_0 t)$$

(11)

The amplitude of the n<sup>th</sup> harmonic, noted Bn, is (12).

$$Bn = \left(\sum_{i=1}^{k} b_n^i\right) = \frac{2V_{max}}{n\pi} \cdot \left(\sum_{i=1}^{k} \left(\cos(n\theta_i) - \cos(n(\pi - \theta_i))\right)\right)$$

(12)

Figure 6. Illustration of the partial waveform Vi

To eliminate a specific harmonic  $V_n$ , it is sufficient to set Bn = 0. Finally, the system of equations used in the SHE technique is solved using MATLAB's fsolve function. The initial guess vector for fsolve is computed based on (13).

$$\theta_0^x = \frac{\pi}{2k} \cdot \left(x - \frac{1}{2}\right)$$

where  $x = 1, 2 \dots k$  and  $k$  the number of switching angles (13)

a. Symmetrical MLI five levels: In the five-level wave form shown in Figure 2, we have two switching angles (14), which means two harmonics to eliminate n=3 and n=5 (3<sup>rd</sup> and 5<sup>th</sup> harmonic).

$$\begin{cases} \sum_{i=1}^{2} \cos(3\theta_i) - \cos(3(\pi - \theta_i)) = 0\\ \sum_{i=1}^{2} \cos(5\theta_i) - \cos(5(\pi - \theta_i)) = 0 \end{cases} \Rightarrow \begin{cases} \theta_1 = 12.00^{\circ}\\ \theta_2 = 48.00^{\circ} \end{cases}$$

(14)

b. Asymmetrical MLI seven levels: The output voltage of the seven-level waveform shown in Figure 3 possessed three switching angles (15), which make it possible to eliminate three harmonics n=3, n=5, and n=7.

$$\begin{cases} \sum_{i=1}^{3} \cos(3\theta_{i}) - \cos(3(\pi - \theta_{i})) = 0\\ \sum_{i=1}^{3} \cos(5\theta_{i}) - \cos(5(\pi - \theta_{i})) = 0\\ \sum_{i=1}^{3} \cos(7\theta_{i}) - \cos(7(\pi - \theta_{i})) = 0 \end{cases} \implies \begin{cases} \theta_{1} = 11.67^{\circ}\\ \theta_{2} = 26.93^{\circ}\\ \theta_{3} = 56.05^{\circ} \end{cases}$$

(15)

Asymmetrical MLI nine levels: The number of switching angles in the nine-level waveform in Figure 4 is four, as indicated by (16), which allows to elimination of four harmonics, n = 3, n = 5, n = 7, and n = 9.

$$\begin{cases} \sum_{i=1}^{4} \cos(3\theta_{i}) - \cos(3(\pi - \theta_{i})) = 0\\ \sum_{i=1}^{4} \cos(5\theta_{i}) - \cos(5(\pi - \theta_{i})) = 0\\ \sum_{i=1}^{4} \cos(7\theta_{i}) - \cos(7(\pi - \theta_{i})) = 0\\ \sum_{i=1}^{4} \cos(9\theta_{i}) - \cos(9(\pi - \theta_{i})) = 0 \end{cases} \Rightarrow \begin{cases} \theta_{1} = 0.85^{\circ}\\ \theta_{2} = 24.85^{\circ}\\ \theta_{3} = 35.14^{\circ}\\ \theta_{4} = 60.85^{\circ} \end{cases}$$

(16)

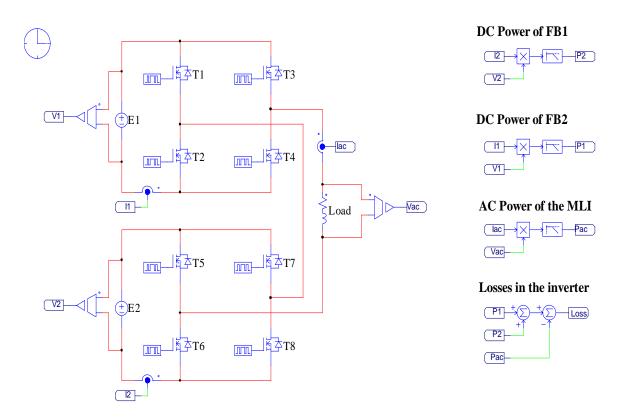

## 3. SIMULATION

The PSIM simulation was conducted using the schematic diagram presented in Figure 7. Figure 7 depicts the configuration of the MLI, which consists of two full bridges connected in series, with four switches each. The output voltage is the sum of the full bridge outputs, and the number of levels can be varied from 5 to 9 according to the switches control and the DC input value, as explained earlier in this article.

Figure 7. Schematic diagram of the PSIM environment

The inverter is connected to an RL circuit (R =  $51.4\,\Omega$  and L =  $200\,\text{mH}$ ) that acts as a low-pass filter to remove high-frequency components from the inverter's output voltage. In order to measure the power absorbed by each full bridge in the inverter, it is necessary to measure the input current and voltage. By multiplying these instantaneous values, the instantaneous power can be obtained. This product is then filtered using a low-pass filter to obtain the average value, which represents the real power consumed by the full bridge. The same procedure is applied to measure the power consumed by the load.

By performing these measurements, it becomes possible to determine the losses in the inverter. This is achieved by subtracting the power at the input of the inverter, which is the sum of the power at the input of each full bridge, from the power at the output of the inverter, which represents the power absorbed by the load. This subtraction allows for the calculation of the losses incurred within the inverter system.

Table 1 shows the output voltage, spectrum analysis of the output voltage, and the current waveform of each case. The spectrum analysis of the output voltage confirms the effectiveness of the Selective Harmonic Elimination (SHE) technique in eliminating specific harmonics. As the number of levels in the inverter increases, more harmonics can be effectively eliminated.

Waveforme Level Voltage spectrum Current spectrum

Output Current Output Voltage **Output Current** 40 0.4 30 0.3 20 0.5 20 0.2 5L 0 10 0.1 -20 -0.5 400 800 600 0 400 20 ms Frequency (Hz) Frequency (Hz) Output Voltage **Output Current** Output Voltage Output Current 40 0.4 30 0.3 0.5 20 20 0.2 7L 10 0.1 -20 0 400 200 400 600 800 Frequency (Hz) **Output Current** Output Voltage Output Current 40 30 0.4 0.3 0.5 20 0.2 9L 10 0.1 -20 0 40 200 400 600 800 400 600 800 1k 0 1k 40 ms Frequency (Hz)

Table 1. Simulation waveforms and spectrum analysis of the inverter output voltage and current were performed on the PSIM environment

## 4. EXPERIMENTAL VALIDATION

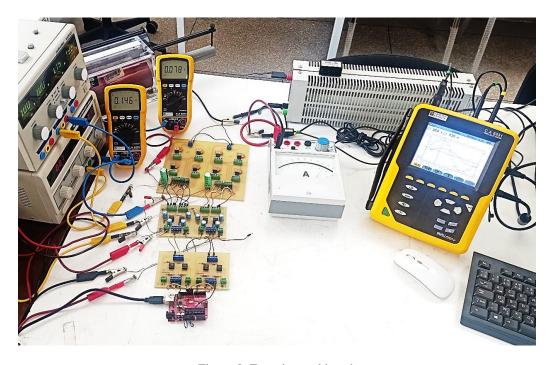

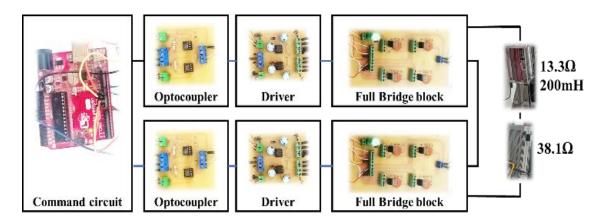

To practically validate the simulation results presented in the previous section, a test bench setup (Figure 8) was used. This experimental setup consists primarily of measurement instruments—including a voltmeter, ammeter, and power quality analyser—as well as the inverter with its drivers and isolation interface feeding an RL load.

Figure 8. Experimental bench

To compare the inverter's performance between simulation and experimental testing, and due to the limited precision of the power quality analyzer, it was necessary to calculate the power on both sides of the inverter using the measured parameters and then deduce the power losses. Additionally, the apparent power was calculated to enable comparison between the power factor and the cosine of the phase angle of the load  $(\cos \varphi)$ , which provides insight into the impact of harmonic distortion.

Figure 9 presents a simplified schematic diagram of the test bench to aid understanding. The system consists of several key components (Figures 8 and 9):

- Command circuit: An Arduino UNO generates command signals that control the operation of the inverter.

- Optocoupler: It serves as a means to separate the command circuit from the power circuit. It ensures electrical isolation and protection between the two circuits.

- Drivers: These components are responsible for applying the required voltage between the gate and the source of the transistors in the inverter.

- Full bridges: These bridge circuits generate the corresponding voltage output based on the commands received from the command circuit. They convert the DC input into the desired AC output voltage

Figure 9. Schematic block of experimental setup

The experimental validation involved measuring various parameters to compare the simulation results with practical results. The following measurements were taken:

- Average voltage (E1, E2) and current (I<sub>DC1</sub>, I<sub>DC2</sub>) at the input of each full bridge.

- I<sub>RMS</sub> the current RMS value measured at the load (RL circuit).

- $V_{RMS}$  voltage RMS value, as well as voltage Total Harmonic Distortion (THD) and current THD, measured at the output of the inverter using a power quality analyzer.

In addition to these measurements, other parameters were calculated using the following formulas:

- DC power at the input of the inverter is calculated in (17).

$$P_{DC} = E1.I_{DC1} + E2.I_{DC2} (17)$$

- AC power at the output of the inverter is determined by using (18).

$$P_{AC} = R.I_{RMS}^2 \tag{18}$$

- Losses in the inverter are deduced by the subtraction of (17) and (18) as indicated in (19).

$$Losses = P_{DC} - P_{AC} \tag{19}$$

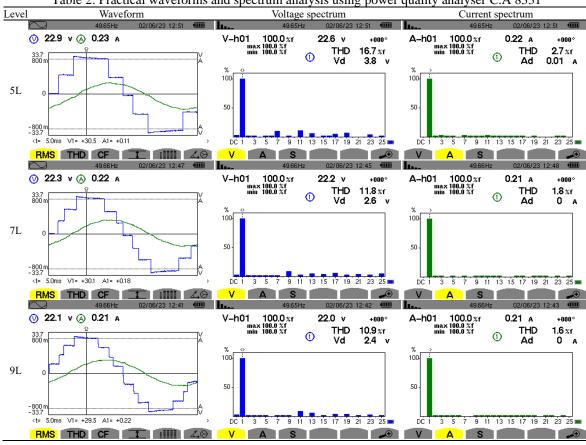

By measuring and calculating these parameters, a comprehensive understanding of the inverter's performance and efficiency can be obtained, allowing for a comparison between simulation and practical results. Table 2 provides a spectrum analysis and waveform representation for both current and voltage at the output of the inverter, corresponding to different numbers of levels.

# Table 2. Practical waveforms and spectrum analysis using power quality analyser C.A 8331

## 5. RESULTS

Simulation and practical results are presented in Table 3. Based on the analysis of Table 3, it is evident that the difference between the results obtained at 7 and 9 levels is relatively small compared to the differences observed between 5 and 7 levels or 5 and 9 levels. This finding reinforces the fact that the elimination of low-order harmonics significantly improves the performance of the inverter. The presence of low-order harmonics, which tend to have significant magnitudes, can adversely impact the quality of the inverter.

Table 3. Simulation and practical results

|          | Measured and calculated parameters | iiiiuiaiioii a | Simulation |         | Practical |         |         |  |  |

|----------|------------------------------------|----------------|------------|---------|-----------|---------|---------|--|--|

| 14       | reasured and carediated parameters | Sym 5L         | Asy. 7L    | Asy. 9L | Sym 5L    | Asy. 7L | Asy. 9L |  |  |

| DMC      | Voltage (V)                        | 22.730         | 22.180     | 21.990  | 22.900    | 22.300  | 22.100  |  |  |

| RMS      | Current (A)                        | 0.276          | 0.272      | 0.270   | 0.279     | 0.273   | 0.271   |  |  |

|          | V Fundamental RMS value (V)        | 22.373         | 22.076     | 21.899  | 22.600    | 22.200  | 22.000  |  |  |

| Spectrum | THD %                              | 17.940         | 12.860     | 11.930  | 16.700    | 11.800  | 10.900  |  |  |

| analysis | I Fundamental RMS value (A)        | 0.276          | 0.272      | 0.269   | 0.270     | 0.270   | 0.260   |  |  |

| •        | THD %                              | 2.130          | 1.210      | 1.070   | 2.700     | 1.800   | 1.600   |  |  |

|          | $P_{DC}(W)$                        | 4.205          | 4.066      | 4.003   | 4.247     | 4.073   | 4.010   |  |  |

|          | $P_{AC}(W)$                        | 3.944          | 3.810      | 3.754   | 4.001     | 3.831   | 3.775   |  |  |

| Power    | Apparent power (VA)                | 6.273          | 6.033      | 5.937   | 6.389     | 6.088   | 5.989   |  |  |

| analysis | Power factor                       | 0.629          | 0.632      | 0.632   | 0.626     | 0.629   | 0.630   |  |  |

| •        | Losses (W)                         | 0.261          | 0.256      | 0.249   | 0.246     | 0.242   | 0.235   |  |  |

|          | Efficiency (%)                     | 93.793         | 93.704     | 93.780  | 94.208    | 94.060  | 94.134  |  |  |

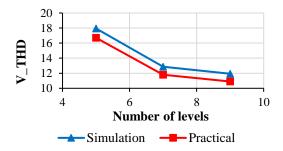

The interpretation of Figure 10 shows a clear correlation between the number of levels and the THD factor. As the number of levels increases, there is a significant reduction in the THD factor. This observation is particularly evident in the transition from 5 levels to 7 levels, where there is a substantial decrease in the THD factor. This reinforces the notion that increasing the number of levels in the inverter leads to a more sinusoidal output waveform with reduced harmonic content, resulting in a lower THD factor.

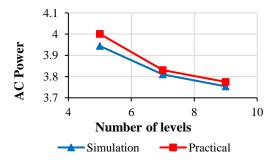

By analysing Figure 11, it is evident that as the number of levels increases in the inverter, the RMS value of the output voltage and its fundamental component progressively converge and become closer to each other. The analysis of Figure 12 shows that the 5-level voltage configuration allows for a higher power transfer compared to the 7-level and 9-level configurations. This observation can be attributed to Figure 13, which demonstrates that an increase in the RMS value of the fundamental component corresponds to an increase in AC power.

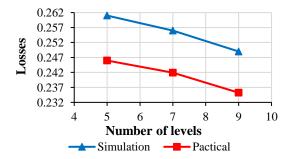

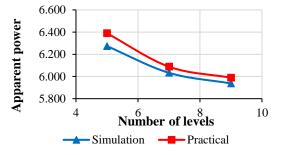

It is evident in Figure 14 that the reduction in losses from 5 levels to 7 levels is smaller compared to the reduction in losses from 7 levels to 9 levels. At the AC side, as the number of levels in the inverter increases, the apparent power decreases (Figure 15). This is primarily due to the harmonics eliminated using the SHE technique, which reduces the distortion power, leading to an improvement in the power factor. From Table 3, it can be observed that the power factor approaches the value of  $\cos(\phi)=0.633$ , where  $\phi$  represents the angle of the load defined as  $\phi=\arctan\left(\frac{2.\pi.f.L}{R}\right)$ .

23 22.8 RMS value 22.6 22.4 22.2 22 21.8 10 18 20 16 **THD** Sim\_V\_RMS Sim\_Fund\_RMS - Pract\_Fund\_RMS Pract\_V\_RMS

Figure 10. Variation of total harmonic distortion of inverter output voltage with number of levels

Figure 11. Comparison of simulated and practical RMS values of the output voltage and its fundamental

4.1 4 5L AC power 3.9 3.8 9I 3.7 22.2 22.4 22.8 21.8 22 22.6 **Fundamental RMS** Simulation Practical

Figure 12. Evolution of the power at the AC side as a function of the number of levels

Figure 13. Evolution of the power at the AC side as a function of the fundamental RMS value

Figure 14. Evolution of the losses in the inverter with the number of levels

Figure 15. Evolution of the apparent power at the AC side as a function of the number of levels

Generally, the practical results validate the simulation results. It is evident that all the practical curves closely align with their corresponding simulation curves and exhibit similar trends. However, slight differences between the two can be attributed to factors such as temperature effects, the accuracy of the simulation model in representing the physical system, and measurement errors.

#### 6. CONCLUSION

In conclusion, the use of MLIs has gained significant popularity in the field of power electronics due to their ability to improve the quality of the output voltage. Asymmetrical MLIs, in particular, offer a higher number of levels compared to symmetrical MLIs, resulting in more sinusoidal voltage waveforms with a low number of switches. Through simulations conducted using the PSIM software and experimental validation, it was demonstrated that increasing the number of levels in the MLI and implementing the SHE technique can effectively reduce the THD factor and losses in the inverter. This leads to improvements in the power factor and overall efficiency of the inverter system. Furthermore, it was observed that as the number of levels in the MLI increases, the magnitude of the fundamental component of the output voltage decreases. This implies that the contribution of the fundamental component to real power production diminishes as more levels are added. Looking ahead, I am eager to explore the application of the asymmetrical configuration for injecting power from photovoltaic (PV) panels. This approach could enhance efficiency and integration of renewable energy sources into the system. Future work will focus on optimizing this setup for real-world PV power delivery.

#### **FUNDING INFORMATION**

Authors state no funding involved.

#### AUTHOR CONTRIBUTIONS STATEMENT

This journal uses the Contributor Roles Taxonomy (CRediT) to recognize individual author contributions, reduce authorship disputes, and facilitate collaboration.

| Name of Author                                      | C            | M            | So           | Va                               | Fo           | Ι            | R | D            | O | E                            | Vi               | Su | P     | Fu |

|-----------------------------------------------------|--------------|--------------|--------------|----------------------------------|--------------|--------------|---|--------------|---|------------------------------|------------------|----|-------|----|

| Nabil Saidani                                       | ✓            | ✓            | ✓            | ✓                                | ✓            |              | ✓ | ✓            | ✓ |                              |                  |    |       |    |

| Rachid El Bachtiri                                  | ✓            | $\checkmark$ |              | $\checkmark$                     | $\checkmark$ | $\checkmark$ |   | $\checkmark$ |   | $\checkmark$                 |                  |    |       |    |

| Abdelaziz Fri                                       | ✓            |              | ✓            | $\checkmark$                     |              | $\checkmark$ | ✓ |              |   | $\checkmark$                 |                  |    |       |    |

| Karima El Hammoumi                                  | $\checkmark$ |              | ✓            | $\checkmark$                     |              |              | ✓ |              |   | $\checkmark$                 |                  |    |       |    |

| C : Conceptualization M : Methodology So : Software |              |              | R : <b>F</b> | nvestiga<br>Resource<br>Data Cui | es           |              |   |              |   | /i : Vi<br>lu : St<br>! : Pr | <b>1</b> pervisi |    | ation |    |

Fu: **Fu**nding acquisition

O: Writing - Original Draft

Fo: **Fo**rmal analysis E: Writing - Review & **E**diting

# CONFLICT OF INTEREST STATEMENT

Authors state no conflict of interest.

## DATA AVAILABILITY

The authors confirm that the data supporting the findings of this study are available within the article.

# REFERENCES

Va: Validation

- [1] C. Buccella, C. Cecati, M. G. Cimoroni, and K. Razi, "Analytical method for pattern generation in five-level cascaded H-bridge inverter using selective harmonic elimination," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 11, pp. 5811–5819, 2014, doi: 10.1109/TIE.2014.2308163.

- [2] R. A. Rana, S. A. Patel, A. Muthusamy, C. woo Lee, and H.-J. Kim, "Review of multilevel voltage source inverter topologies and analysis of harmonics distortions in FC-MLI," *Electronics*, vol. 8, no. 11, p. 1329, Nov. 2019, doi: 10.3390/electronics8111329.

- [3] Y. Babkrani, A. Naddami, and M. Hilal, "A smart cascaded H-bridge multilevel inverter with an optimized modulation techniques increasing the quality and reducing harmonics," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 10, no. 4, p. 1852, Dec. 2019, doi: 10.11591/ijpeds.v10.i4.pp1852-1862.

- [4] O. Alavi, A. H. Viki, and S. Shamlou, "A comparative reliability study of three fundamental multilevel inverters using two different approaches," *Electronics*, vol. 5, no. 2, 2016, doi: 10.3390/electronics5020018.

- [5] S. De, D. Banerjee, K. Siva Kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," IET Power Electronics, vol. 4, no. 4, pp. 384–392, 2011, doi: 10.1049/iet-pel.2010.0027.

[6] N. Saidani, R. El Bachtiri, A. Fri, and K. El Hammoumi, "Control of a full-bridges five levels inverter: Experimental validation," 2023, pp. 590–599. doi: 10.1007/978-3-031-29860-8\_60.

- [7] A. Fri, R. El Bachtiri, A. El Ghzizal, and A. Naamane, "Triphase symmetrical cascaded multilevel inverter (5l) for PV systems controlled by various multicarrier PWM strategies," *Energy Procedia*, vol. 62, pp. 543–554, 2014, doi: 10.1016/j.egypro.2014.12.416.

- [8] C. I. Odeh, E. S. Obe, and O. Ojo, "Topology for cascaded multilevel inverter," IET Power Electronics, vol. 9, no. 5, pp. 921–929, Apr. 2016, doi: 10.1049/iet-pel.2015.0375.

- [9] Y. Neyshabouri, K. K. Monfared, H. Iman-Eini, and M. Farhadi-Kangarlu, "Symmetric cascaded H-bridge multilevel inverter with enhanced multi-phase fault tolerant capability," *IEEE Transactions on Industrial Electronics*, vol. 69, no. 9, pp. 8739–8750, Sep. 2022, doi: 10.1109/TIE.2021.3114745.

- [10] N. Farokhnia, S. H. Fathi, N. Yousefpoor, and M. K. Bakhshizadeh, "Minimisation of total harmonic distortion in a cascaded multilevel inverter by regulating voltages of DC sources," *IET Power Electronics*, vol. 5, no. 1, pp. 106–114, 2012, doi: 10.1049/iet-pel.2011.0092.

- [11] M. J. Shah, K. S. Pandya, and P. Chauhan, "Direct ADC controlled asymmetric cascaded multilevel inverter," Engineering, Technology & Applied Science Research, vol. 12, no. 4, pp. 9071–9077, Aug. 2022, doi: 10.48084/etasr.5164.

- [12] D. Chittathuru, S. Padmanaban, and R. Prasad, "Design and implementation of asymmetric cascaded multilevel inverter with optimal components," *Electric Power Components and Systems*, vol. 49, no. 4–5, pp. 361–374, Mar. 2021, doi: 10.1080/15325008.2021.1970290.

- [13] R. Vasu, S. K. Chattopadhyay, and C. Chakraborty, "Asymmetric cascaded H-Bridge multilevel inverter with single DC source per phase," IEEE Transactions on Industrial Electronics, vol. 67, no. 7, pp. 5398–5409, 2020, doi: 10.1109/TIE.2019.2934080.

- [14] K. Yang, X. Lan, Q. Zhang, and X. Tang, "Unified selective harmonic elimination for cascaded H-bridge asymmetric multilevel inverter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 4, pp. 2138–2146, 2018, doi: 10.1109/JESTPE.2018.2808539.

- [15] N. Prabaharan and K. Palanisamy, "Comparative analysis of symmetric and asymmetric reduced switch MLI topologies using unipolar pulse width modulation strategies," *IET Power Electronics*, vol. 9, no. 15, pp. 2808–2823, 2016, doi: 10.1049/iet-pel.2016.0283.

- [16] M. Tayyab, A. Sarwar, S. Murshid, M. Tariq, S. Urooj, and B. Khan, "Grid-connected operation and control of single-phase asymmetrical multilevel inverter for distributed power generation," *IET Renewable Power Generation*, vol. 16, no. 16, pp. 3629– 3642, 2022, doi: 10.1049/rpg2.12581.

- [17] I. Torres, J. Muñoz, D. Rojas, and E. Espinosa, "Selective harmonic elimination technique for a 27-level asymmetric multilevel converter," *Energies*, vol. 15, no. 10, p. 3694, May 2022, doi: 10.3390/en15103694.

- [18] K. T. Maheswari, R. Bharanikumar, V. Arjun, R. Amrish, and M. Bhuvanesh, "A comprehensive review on cascaded H-bridge multilevel inverter for medium voltage high power applications," *Materials Today: Proceedings*, vol. 45, pp. 2666–2670, 2021, doi: 10.1016/j.matpr.2020.11.519.

- [19] A. M. Noman, A. A. Al-Shamma'a, K. E. Addoweesh, A. A. Alabduljabbar, and A. I. Alolah, "Cascaded multilevel inverter topology based on cascaded H-bridge multilevel inverter," *Energies*, vol. 11, no. 4, 2018, doi: 10.3390/en11040895.

- [20] I. Sajid et al., "Runge-Kutta optimization-based selective harmonic elimination in an H-bridge multilevel inverter," IET Power Electronics, vol. 16, no. 11, pp. 1849–1865, Aug. 2023, doi: 10.1049/pel2.12507.

- [21] R. A. Khan *et al.*, "Archimedes optimization algorithm based selective harmonic elimination in a cascaded h-bridge multilevel inverter," *Sustainability (Switzerland)*, vol. 14, no. 1, 2022, doi: 10.3390/su14010310.

- [22] S. Ürgün, H. Yiğit, and S. Mirjalili, "Investigation of recent metaheuristics based selective harmonic elimination problem for different levels of multilevel inverters," *Electronics*, vol. 12, no. 4, p. 1058, Feb. 2023, doi: 10.3390/electronics12041058.

- [23] O. Zolfagharian, A. Dastfan, and M. H. Marzebali, "Selective harmonic elimination technique improvement for cascaded H-bridge multilevel converters under DC sources uncertainty," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 12, no. 2, pp. 1282–1293, Apr. 2024, doi: 10.1109/JESTPE.2023.3271653.

- [24] M. Khizer, S. Liaquat, M. F. Zia, S. Kanukollu, A. Al-Durra, and S. M. Muyeen, "Selective harmonic elimination in a multilevel inverter using multi-criteria search enhanced firefly algorithm," *IEEE Access*, vol. 11, pp. 3706–3716, 2023, doi: 10.1109/ACCESS.2023.3234918.

- [25] M. M.A. Alakkad, Z. Rasin, M. Rasheed, W. Abd Halim, and R. Omar, "Real-time switching thirteen-level modified CHB-Multilevel inverter using artificial neural network technique based on selective harmonic elimination," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 20, no. 3, p. 1642, Dec. 2020, doi: 10.11591/ijeecs.v20.i3.pp1642-1652.

- [26] M. A. Memon, M. D. Siddique, S. Mekhilef, and M. Mubin, "Asynchronous particle swarm optimization-genetic algorithm (APSO-GA) based selective harmonic elimination in a cascaded H-bridge multilevel inverter," *IEEE Transactions on Industrial Electronics*, vol. 69, no. 2, pp. 1477–1487, Feb. 2022, doi: 10.1109/TIE.2021.3060645.

# **BIOGRAPHIES OF AUTHORS**

Nabil Saidani was born in Kenitra, Morocco in January 1989, obtained his engineering diploma in Electronics, Electrotechnics and Automatics from the Faculty of Science and Technology of Tangier in 2014. Afterwards, he was able to pass his agrégation in electrical engineering in 2019, allowing him to teach specialized physics in electronics and industrial computing at the BTS centre of Fez. His research area is the advanced control of multilevel inverter to inject photovoltaic power into the grid. He can be contacted at email: nabil.saidani@usmba.ac.ma.

Abdelaziz Fri was born in Fez, Morocco. After graduating from the École Normale Supérieure de l'Enseignement Technique (ENSET) in Rabat, Morocco, in 1998, he began his career as a teacher in engineering sciences. He later pursued a Master's degree in Engineering of Industrial Automated Systems from the Faculty of Sciences at Sidi Mohamed Ben Abdellah University in Fez, Morocco. In 2017, Abdelaziz completed his Ph.D. in Renewable Energies and Static Converters. The following year, in 2018, he joined the Higher School of Technology at USMBA University in Fez as an assistant professor. Currently, he is an associate member of the Technologies and Industrial Services Laboratory, and a member of the Research Team in Electrical Engineering, Power Electronics, and Renewable Energies (Équipe de Recherche en Électrotechnique, Électronique de Puissance et Énergies Renouvelables). His research interests include renewable energies and the control of electrical systems. He can be contacted at email: Abdelaziz.fri@usmba.ac.ma.

Karima El Hammoumi received the State Engineer diploma in Automatic Control and Industrial Computing in 1985 and the DESA in 'Industrial Process Control' in 2001 from the Mohammadia School of Engineers, Rabat, Morocco. She obtained the Doctorate degree in Renewable Energies from the University sidi Mohamed Ben Abdellah Fez, Morocco in July 2021. Professor EL HAMMOUMI is currently a Professor at the Higher School of Technology, Université Sidi Mohamed Ben Abdellah, Fez, Morocco. His research interests automatic control systems, renewable energy, smart grid and battery storage. She can be contacted at email: karima.elhammoumi@usmba.ac.ma