ISSN: 2088-8694, DOI: 10.11591/ijpeds.v16.i4.pp2605-2614

# Design and DSP-based validation of a cascaded DSOGI-PLL for mitigating grid disturbances

#### Ilias En-Naoui, Abdelhadi Radouane, Azeddine Mouhsen, Hamid Yantour

Laboratory of Energy-Matter-Instrumentation and Telecoms (EMIT), Faculty of Sciences and Techniques, Hassan First University, Settat, Morocco

#### **Article Info**

#### Article history:

Received Mar 18, 2025 Revised Sep 18, 2025 Accepted Oct 2, 2025

#### Keywords:

Digital signal processor Grid synchronization Phase-locked loop Power electronics Systems control

#### **ABSTRACT**

Ensuring a smooth power injection into an electric grid in the presence of imperfections, such as phase disturbances, voltage imbalance, frequency variations, harmonics, and DC offsets, requires fast and robust phase-locked loop (PLL) techniques. Among these, the double second-order generalized integrator (DSOGI)-based PLL is widely used due to its strong performance in challenging grid conditions. However, conventional DSOGI-PLL has limitations in handling DC offsets and harmonic disturbances. To address these challenges, this paper introduces the design of a cascaded DSOGI-PLL that enhances attenuation of DC components and low-order harmonics while maintaining computational simplicity for DSP-based implementation. Experimental validation on a TMS320F28379D DSP platform demonstrates that the proposed scheme achieves synchronization settling within 48 ms even under severely polluted grid conditions, while reducing output unit-vector THD to 0.5% when the input voltage contains 22% THD. These results confirm the cascaded DSOGI-PLL as a significant improvement over conventional PLLs.

This is an open access article under the <u>CC BY-SA</u> license.

2605

# Corresponding Author:

Ilias En-Naoui

Laboratory of Energy-Matter-Instrumentation and Telecoms (EMIT)

Faculty of Sciences and Technology, Hassan First University

BP: 577, Route de Casablanca. Settat, Morocco

Email: i.ennaoui@uhp.ac.ma

#### 1. INTRODUCTION

Power electronic converters play a critical role in the integration of renewable energy sources [1], and their effective control relies on robust synchronization algorithms with the grid as described in Figure 1. These algorithms must accurately estimate key grid voltage parameters, such as phase, amplitude, and frequency, to ensure grid stability and reliable power transfer. Among these algorithms, phase-locked loops (PLLs) serve as a fundamental component for achieving synchronization and implementing closed-loop control strategies in grid-connected power converters.

A wide range of three-phase PLLs has been reported in the literature. The conventional synchronous reference frame PLL (SRF-PLL) [2], [3] is simple and effective under balanced and clean grid conditions, but its performance degrades severely in the presence of voltage imbalance or harmonics. To mitigate these issues, enhanced schemes such as decoupled double synchronous reference frame PLL (DDSRF-PLL) [3], [4] have been developed, improving accuracy under imbalance. Other advanced PLLs for single-phase and three-phase systems [5]-[8] exist, but their high computational burden often limits their applicability on low-end digital controllers.

Journal homepage: http://ijpeds.iaescore.com

The double second-order generalized integrator PLL (DSOGI-PLL) [9], [10] has emerged as a promising alternative due to its ability to attenuate harmonics and handle voltage unbalance. It relies on two SOGI adaptive filters to generate orthogonal signals, which are then processed by an embedded SRF-PLL. However, despite its robustness, the DSOGI-PLL still faces challenges. First, the SOGI structure is not inherently designed to reject DC offsets, which may arise from grid asymmetries, control imperfections in renewable inverters, or measurement hardware such as transducers and ADCs [11]-[15]. The presence of such offsets leads to DC components in the PLL output unit vectors, violating grid interconnection standards like IEEE 1547-2018 [16], [17]. Second, DSOGI-PLL shows limited rejection capability against low-order harmonics, which are common in grids with nonlinear loads, photovoltaic inverters, or transformer saturation [18]-[20]. These harmonics distort the input voltage and degrade the phase and frequency estimation accuracy [21]. Table 1 summarizes the Strengths and points of weakness of each structure mentioned above against grid's disturbances.

These limitations highlight the need for improved synchronization schemes that remain accurate under DC offsets, low-order harmonics, and grid voltage imbalance. In this paper, we propose a cascaded DSOGI-PLL, a three-phase PLL structure designed to overcome the aforementioned issues while maintaining computational simplicity suitable for digital controllers in renewable energy converters. The proposed scheme cascades two DSOGI stages to enhance attenuation of low-order harmonics and DC components, thus ensuring accurate synchronization even under distorted or unbalanced grid conditions.

The novelty of this work lies in i) introducing a cascaded DSOGI architecture explicitly designed for DC offset and low-order harmonic rejection, ii) providing a complete discretization for real-time deployment, and iii) demonstrating an experimental validation on a DSP-based implementation using the TMS320F28379D platform. This approach is particularly relevant for grid-connected inverters in renewable energy systems, where fast and reliable synchronization under practical disturbances is essential.

This paper is organized as follows: The first section provides an analysis of the DSOGI structure to identify its weaknesses, followed by the design of the cascaded DSOGI-PLL and its discretization process to enable implementation on a digital processor. The second section discusses the experimental results, where the PLL is implemented on the TMS320F28379D DSP board, and its performance is validated under various real-world grid scenarios using a grid emulator developed in our laboratory. Finally, the last section provides a conclusion summarizing the key contributions of the work and potential future research directions.

Figure 1. General architecture of the grid synchronization system for renewable energy converters

Table 1. Strengths and weaknesses of three-phase PLLs against grid's imperfections

| PLL method | Balance | Imbalance | Frequency variation | High order harmonics | Low order harmonics | DC offset |

|------------|---------|-----------|---------------------|----------------------|---------------------|-----------|

| SRF-PLL    | ✓       | ×         | ✓                   | ×                    | ×                   | ×         |

| DDSRF-PLL  | ✓       | ✓         | ✓                   | ×                    | ×                   | ×         |

| DSOGI-PLL  | ✓       | ✓         | ✓                   | ✓                    | ×                   | ×         |

# 2. METHODS

This section initially describes the limitations of the DSOGI-PLL under non-ideal grid conditions. Following this analysis, we present the design of a cascaded DSOGI-PLL to overcome these limitations.

## 2.1. Conventional DSOGI-PLL

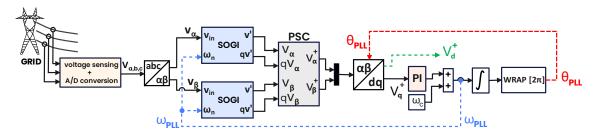

The DSOGI-PLL illustrated in Figure 2, employs two SOGI quadrature signal generators (SOGI) to filter out voltage harmonics, a positive sequence calculator (PSC) to calculate positive's voltage sequence

during imbalance using (1) and (2), and a synchronous reference frame PLL (SRF-PLL) to estimate the grid frequency, phase angle, and the positive voltage sequence. The estimated frequency is then fed back to the DSOGI, ensuring frequency adaptability under varying grid conditions.

$$V_{\alpha}^{+} = \frac{1}{2} \cdot (V_{\alpha} - qV_{\beta}) \tag{1}$$

$$V_{\beta}^{+} = \frac{1}{2} \cdot (qV_{\alpha} + V_{\beta}) \tag{2}$$

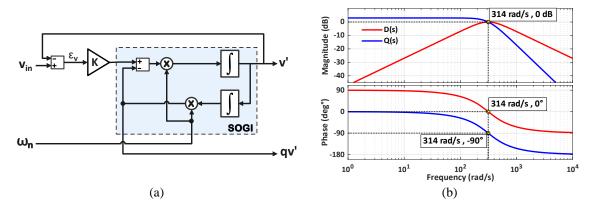

The DSOGI-PLL converts the measured grid voltages through an ADC. Then, it transforms these voltages into the stationary reference frame using the Clarke transformation, resulting in the  $V_{\alpha}$  and  $V_{\beta}$  components. Each of these signals is then processed by an SOGI block, which consists of a second-order generalized integrator, as illustrated in Figure 3(a). The SOGI bloc generates two outputs for each input signal: the direct component v and the quadrature component qv'. These outputs are related to the input through D(s) and Q(s) transfer functions, as defined in (3) and (4), respectively.

$$D(s) = \frac{v'}{v_{in}} = \frac{k.\omega_n s}{s^2 + k.\omega_n s + \omega_n^2}$$

(3)

$$Q(s) = \frac{qv'}{v_{in}} = \frac{k \cdot \omega_n^2}{s^2 + k \cdot \omega_n \cdot s + \omega_n^2}$$

$$\tag{4}$$

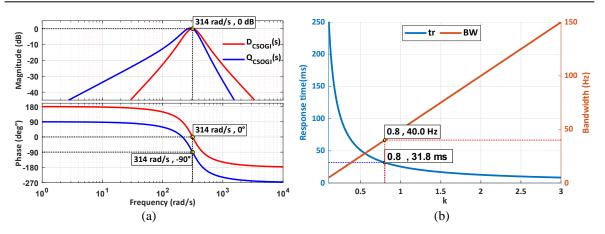

The bode diagrams in Figure 3(b) is plotted using  $\omega_n = 2\pi \times 50$  and  $k = \sqrt{2}$  which provides the minimum response time while ensuring an optimal overshoot of 4%. It is evident that at the frequency  $\omega_n$ , the gain of both transfer functions is unity. From (3) and (4) and their bode plots, it is evident that these represent two second-order filters, where D(s) exhibits a band-pass filtering characteristic, while Q(s) is a low-pass filter. Both D(s) and Q(s) are effective in attenuating high-frequency harmonics; however, their filtering effect is less pronounced when dealing with low-order harmonics. Also, the two transfer functions exhibit a phase shift of 90° between them at the frequency  $\omega_n$ , regardless of the value of k, which means that v' and qv' will be in quadrature, and v' is in phase with the signal  $v_{in}$  at this frequency. Additionally, an issue arises with Q(s) in the presence of a DC offset. From bode plots, Q(s) is incapable of eliminating the DC component, which will have a detrimental impact on the performance of the PLL [22], [23].

Figure 2. Architecture of a double second-order generalized integrator phase-locked loop

Figure 3. SOGI model: (a) structure and (b) transfer functions bode plot

# 2.2. The three-phase cascaded DSOGI PLL

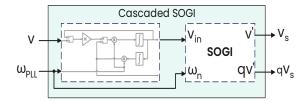

To deal with the problems discussed in the previous section, namely DC offset and low-order harmonics, a design of a cascaded SOGI is proposed. The two SOGI blocks shown in Figure 1 will be replaced with two CSOGI blocks, whose structure is provided in Figure 4. The CSOGI structure is formed by a cascade of two SOGI blocks.

Figure 4. Architecture of a cascaded second-order generalized integrator

In this configuration, the signal v' from the first SOGI block is introduced as the new input for the second SOGI block, since it does not contain any DC component, while the signal qv' will not be considered by the second SOGI block because it allows the DC component to pass through. As a consequence, the second SOGI block processes only the filtered signal v', which is in phase with the original signal v at the frequency  $\omega_{PLL}$ , as discussed in the previous section.

The second SOGI then performs an additional filtering step on v' and generates quadrature signals  $v_s$  and  $qv_s$ , both are unaffected by DC offset. The transfer functions  $D_{CSOGI}(s)$  and  $Q_{CSOGI}(s)$ , which relate  $v_s$  and  $qv_s$  to the input v, are given by (5) and (6), respectively.

$$D_{CSOGI}(s) = \frac{v_s}{v} = \frac{(k.\omega_{PLL}.s)^2}{(s^2 + k.\omega_{PLL}.s + \omega_{PLL}^2)^2}$$

(5)

$$Q_{CSOGI}(s) = \frac{qv_s}{v} = \frac{k^2 \cdot \omega_{PLL}^3 \cdot s}{(s^2 + k \cdot \omega_{PLL} \cdot s + \omega_{PLL}^2)^2}$$

(6)

$$t_{\mathcal{S}} = \frac{4}{\xi \cdot \omega_n} \tag{7}$$

$$Bandwidth = \frac{\omega_n \cdot k}{2\pi} \tag{8}$$

As illustrated by the bode diagrams in Figure 5(a) and (5) and (6), the transfer function  $D_{CSOGI}(s)$  exhibits a band-pass filtering characteristic, achieving unity gain at the frequency  $\omega_{PLL}$  and stronger attenuation at frequencies that exceed its passband. It is also notable that the transfer function  $D_{CSOGI}(s)$  introduces a phase shift of zero at  $\omega_{PLL}$ , thereby ensuring that the output signal  $v_s$  is in phase with the input signal v and they have the same amplitude at this particular frequency. This configuration provides an additional filtering step, which in turn helps to reduce the impact of low/high-order frequency harmonics. For  $Q_{CSOGI}(s)$ , unlike the SOGI, it does not allow the DC component to pass through. It achieves a unity gain at the frequency  $\omega_{PLL}$  and introduces a phase shift of -90° at this frequency. As a result, it generates  $qv_s$ , which is a filtered version of the input signal v, with the same amplitude and in quadrature at the frequency  $\omega_{PLL}$ .

For the design of the cascaded SOGI block, the parameter k is the key factor that determines the dynamics of this block, which will have a significant impact on the response time of the C-SOGI block and its bandwidth, thus affecting its speed and its ability to filter low and high frequencies. To analyze this, we have plotted the evolution of the response time and bandwidth of the C-SOGI as a function of the value of k, using (7) and (8), as illustrated in Figure 5(b). The response time mentioned here refers to the 2% settling. It is observed that to achieve a good filtering effect, the value of k must be small. However, this comes at the cost of slower response time, creating a trade-off between the block's response time and its filtering performance. For this reason, a value of k = 0.8 has been chosen, which provides a bandwidth of 40 Hz and a response time of 32 ms. The choice of this bandwidth range [30 Hz, 70 Hz] is justified because it is sufficiently far from low-order harmonic frequencies [3rd, 5th, 7th ...]. At the closest harmonic frequency, which is the 3rd order one, the attenuation is less than -20 dB, whereas for the SOGI block with the same value of k, the attenuation at this frequency is only -10 dB.

Figure 5. CSOGI model: (a) bode plot and (b) time response vs bandwidth

# 2.3. Discretization and implementation of the three-phase cascaded DSOGI-PLL

With regard to the integrated SRF-PLL, the parameters  $K_P$  and  $T_i$  for the PI controller are selected based on its closed-loop model [24], as outlined in (9). The damping ratio  $\xi$  is set to  $\frac{\sqrt{2}}{2}$ , as this value provides an optimal relationship between response time and overshoot in the dynamic response, while the natural frequency  $\omega_n$  is selected as  $2.\pi.55 \ rad/s$  to match the desired bandwidth. This choice conforms to the IEEE standard, which allows for a frequency variation f up to  $\pm 10\%$  around the nominal 50 Hz frequency in output unit vectors [25]. Using these values, we find  $K_P = 345.5752$  and  $T_i = 83.7$  ms.

$$\frac{\theta_{\text{PLL}}(s)}{\theta(s)} = \frac{K_{\text{P.}}s + \frac{K_{p}}{T_{t}}}{s^{2} + K_{\text{P.}}s + \frac{K_{p}}{T_{t}}} \tag{9}$$

To implement the three-phase cascaded DSOGI PLL on a digital processor, it is necessary to discretize all its blocks. For this purpose, a sampling time of  $Ts = 100 \mu s$  has been chosen. We have selected the Tustin method [26], using (10), which gives a good approximation of an integrator.

$$S \to \frac{T_S}{2} \cdot \frac{1 - z^{-1}}{1 + z^{-1}} \tag{10}$$

The difference equations for the PI controller and the various integrators within this structure are provided by (11) and (12). The settling time of the SRF-PLL with the chosen values of  $K_P$  and  $T_i$  is  $t_{SRF} = 16 \, ms$ . In the worst-case scenario for this structure, the total settling time will be the sum of the SRF bloc and the CSOGI blocks' settling time, resulting in  $t_{CSOGI} = 48 \, ms$  as mentioned in (13), hence, the structure will respond within a maximum of two and a half periods for any transient condition.

PI controller:

$$y(n) = y(n-1) + 345.8 \times u(n) - 345.4 \times u(n-1)$$

(11)

Integrators:

$$y(n) = y(n-1) + 5 \cdot 10^{-5} \times (u(n) - u(n-1))$$

(12)

Settling time:

$$t_s = t_{CSOGI} + t_{SRF} \approx 32 + 16 \approx 48 \, ms$$

(13)

# 3. DISCUSSIONS OF THE OBTAINED RESULTS

This section presents the setup used to validate the PLL's performance and discusses the obtained results, focusing on its accuracy, time response, and robustness against disturbances.

# 3.1. The experimental setup

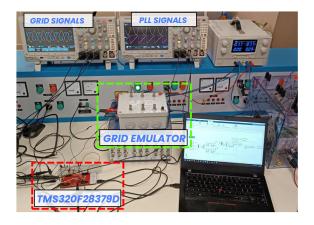

The cascaded DSOGI-PLL structure is validated using the experimental setup shown in Figure 6. In this setup, the cascaded DSOGI-PLL was implemented on the DSP board TMS320F28379D running at 200 MHz, with a sampling time of Ts = 100  $\mu$ s. The DSP's onboard 12-bit ADC modules were used to acquire the three-phase voltage signals. A grid emulator, developed in our laboratory, was employed to generate test scenarios that emulate real grid conditions. The test signals produced include a 1.5 V DC offset and vary between 0 V and 3 V to match the ADC input range of the DSP board.

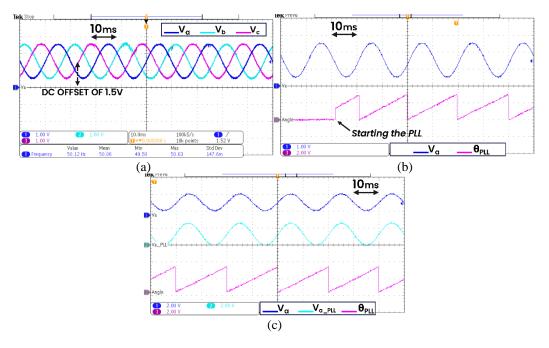

#### 3.2. Scenario N°1: balanced grid

In this first test, a balanced grid voltage ( $V_a$ ,  $V_b$ ,  $V_c$ ) of  $\sqrt{2}$ . 220 V amplitude and 50 Hz frequency was applied to the input of the DSP, as illustrated in Figure 7(a). It can be observed that the PLL locks within 20 ms after startup, and the phase angle  $\theta_{PLL}$  exhibits a linear trend, as shown in Figure 7(b), which represents the evolution of the phase angle generated by the PLL along with the grid voltage  $V_a$ . In the steady-state condition, depicted in Figure 7(c), the signal  $V_{a\_PLL}$ , which represents the unit vector output of the PLL, is in phase with the grid signal  $V_a$ . This demonstrates, first and foremost, the ability of this structure to quickly adapt to a balanced grid.

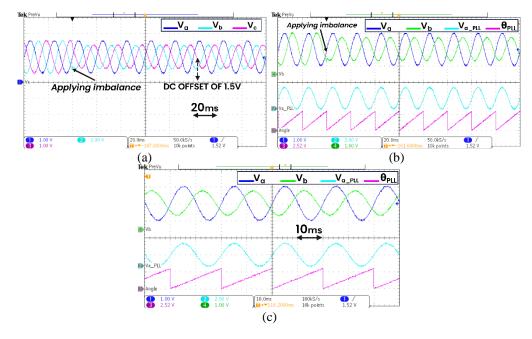

# 3.3. Scenario N°2: unbalanced grid

Figure 8(a) illustrates the signal applied to the input of the PLL in the case of an unbalanced grid, where the positive sequence is  $\sqrt{2}$ . 220 V and the negative sequence is  $\sqrt{2}$ . 50 V which gives an imbalance rate of 22%. From the transient response shown in Figure 8(b) and the steady-state response depicted in Figure 8(c), it is evident that the PLL is completely insensitive to this type of imperfection. Despite the application of such a disturbance, the PLL remains locked to the grid's fundamental component, and the phase angle maintains its linear curve. Furthermore, the unit vector output  $V_{a\_PLL}$  remains in phase with the grid signal  $V_a$ , confirming the robustness of this structure in maintaining synchronization despite grid imperfections.

Figure 6. The practical experimental setup

Figure 7. Balanced grid: (a) grid voltage, (b) transient, and (c) steady-state response

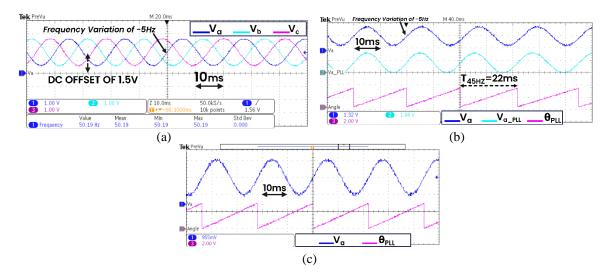

#### 3.4. Scenario N°3: frequency variation

In this test, a frequency jump of -5 Hz was applied to the grid, as illustrated in Figure 9(a), resulting in a grid frequency of 45 Hz. From the transient response shown in Figure 9(b), it is observed that the PLL locks within 20 ms, and the unit vector signal  $V_{a\_PLL}$  aligns perfectly with the grid signal  $V_a$ . In addition, Figure 9(c) presents the steady-state response, where the PLL generates a linear phase angle  $\theta_{PLL}$  that evolves in sync with the grid signal  $V_a$ , demonstrating its ability to accurately track and adapt to frequency variations.

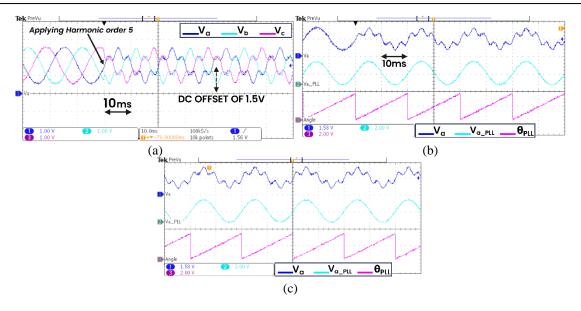

#### 3.5. Scenario N°4: presence of harmonics

In this test, the 5th harmonic with an amplitude of  $\sqrt{2}$ . 50 V was injected into the grid signal, while the fundamental component of the grid remained at  $\sqrt{2}$ . 220 V, resulting in a THD of 22%, as illustrated in Figure 10(a). It is clear that, even under such a disturbance, the PLL output remains locked to the grid's fundamental component, as shown in Figure 10(b). The phase angle  $\theta_{PLL}$  maintains a purely linear trend, and the unit vector signal  $V_{a\_PLL}$  aligns perfectly with the grid's fundamental. A quantitative analysis shows that the unit vector  $V_{a\_PLL}$  has very low distortion, with a THD of around 0.5%. This is much lower than the 22% THD present in the input signal. This is further confirmed by the PLL's steady-state response in Figure 10(c), which demonstrates its ability to effectively handle harmonic distortions originating from the grid.

Figure 8. Unbalanced grid: (a) grid voltage, (b) transient, and (c) steady-state response

Figure 9. Frequency variation test: (a) grid voltage, (b) transient, and (c) steady-state response

Figure 10. Distorted grid: (a) grid voltage, (b) transient, and (c) steady-state response

#### 3.6. Summary of work and results discussion

Through a series of test scenarios emulating real grid disturbances, the proposed cascaded DSOGI-PLL demonstrated its effectiveness in rejecting these disturbances. Notably, all the grid signals tested contained a DC offset of 1.5 V, but the results confirmed that the PLL had succeeded in eliminating this offset entirely. What's more, during the voltage distortion test, particularly with the 5th harmonic, which is a low-order harmonic, the PLL remained highly resistant. Despite imposing a relatively high THD of 22% on the mains voltage, the PLL reduced the distortion of its unit-vector output to approximately 0.5%, while the phase angle response remained linear, indicating great strength in the face of such disturbances. In terms of response time, the PLL was able to synchronize in the worst case over two and a half cycles of fundamental grid voltage, i.e. around 48 ms, making it ideally suited to applications such as power injection and active power filtering, where fast, precise control actions are crucial. In addition, frequency variation tests confirmed that the PLL's output accurately followed frequency changes, guaranteeing reliable synchronization under dynamic grid conditions. In the case of voltage imbalance, no distortion was observed in the PLL's output, demonstrating once again its ability to cope with a wide range of grid conditions. Lastly, the structure could be further improved by developing an adaptive tuning mechanism for the SOGI blocks, allowing the coefficient "k" to dynamically adjust and achieve an optimal trade-off between PLL response time and bandwidth based on real-time grid conditions.

# 4. CONCLUSION

This work presents the design, implementation, and validation of a cascaded DSOGI-PLL to enhance synchronization in grid-connected systems under challenging conditions. By overcoming DSOGI-PLL's limitations in handling DC offsets and low-order harmonics, the proposed approach improves phase estimation accuracy and robustness. Experimental results confirm the PLL's performance, demonstrating fast and accurate synchronization across all tested scenarios, making it a reliable solution for synchronization. To further improve performance, future work will focus on developing an adaptive version of the cascaded DSOGI block, improving the trade-off between response time and bandwidth. This step forward will refine the dynamic behaviour of the PLL, guaranteeing even greater adaptability to grid disturbances.

#### FUNDING INFORMATION

This research received no external funding.

#### **AUTHOR CONTRIBUTIONS STATEMENT**

This journal uses the Contributor Roles Taxonomy (CRediT) to recognize individual author contributions, reduce authorship disputes, and facilitate collaboration.

| Name of Author     | C | M            | So | Va           | Fo           | I            | R | D | 0 | E            | Vi | Su           | P | Fu |

|--------------------|---|--------------|----|--------------|--------------|--------------|---|---|---|--------------|----|--------------|---|----|

| Ilias En-Naoui     | ✓ | ✓            | ✓  | ✓            |              | ✓            | ✓ |   | ✓ |              | ✓  |              |   |    |

| Abdelhadi Radouane |   | $\checkmark$ |    | $\checkmark$ | $\checkmark$ |              |   |   |   | $\checkmark$ | ✓  | $\checkmark$ |   |    |

| Azeddine Mouhsen   |   |              |    |              |              | $\checkmark$ |   |   |   | $\checkmark$ | ✓  | $\checkmark$ |   |    |

| Hamid Yantour      |   |              |    |              | ✓            |              |   |   |   | ✓            | ✓  | ✓            |   |    |

Va: Validation

O: Writing - Original Draft

Fu: Funding acquisition

Fo: Formal analysis E: Writing - Review & Editing

#### CONFLICT OF INTEREST STATEMENT

Authors state no conflict of interest.

#### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### REFERENCES

- [1] B. Popadic, B. Dumnic, V. Katic, D. Sljivac, and D. Pelin, "Overview of grid connected converter synchronization techniques under different grid voltage conditions," in 2017 International Conference on Smart Systems and Technologies (SST), IEEE, Oct. 2017, pp. 99–105. doi: 10.1109/SST.2017.8188677.

- [2] S. Natesan and J. Venkatesan, "A SRF-PLL control scheme for DVR to achieve grid synchronization and PQ issues mitigation in PV fed grid connected system," *Circuits and Systems*, vol. 07, no. 10, pp. 2996–3015, 2016, doi: 10.4236/cs.2016.710256.

- [3] I. En-Naoui, A. Radouane, A. Mouhsen, E. Jarmouni, and E. Ennajih, "DSP implementation and discretization of phase locked loop methods in presence of grid imperfections," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 15, no. 3, p. 1490, Sep. 2024, doi: 10.11591/ijpeds.v15.i3.pp1490-1498.

- [4] F. SEVİLMİŞ and H. KARACA, "Performance analysis of SRF-PLL and DDSRF-PLL algorithms for grid interactive inverters," International Advanced Researches and Engineering Journal, vol. 3, no. 2, pp. 116–122, Aug. 2019, doi: 10.35860/iarej.412250.

- [5] F. Gonzalez-Espin, E. Figueres, and G. Garcera, "An adaptive synchronous-reference-frame phase-locked loop for power quality improvement in a polluted utility grid," *IEEE Transactions on Industrial Electronics*, vol. 59, no. 6, pp. 2718–2731, Jun. 2012, doi: 10.1109/TIE.2011.2166236.

- [6] Y. F. Wang and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," *IEEE Transactions on Power Electronics*, vol. 26, no. 7, pp. 1987–1997, Jul. 2011, doi: 10.1109/TPEL.2010.2099669.

- [7] I. Carugati, P. Donato, S. Maestri, D. Carrica, and M. Benedetti, "Frequency adaptive PLL for polluted single-phase grids," *IEEE Transactions on Power Electronics*, vol. 27, no. 5, pp. 2396–2404, May 2012, doi: 10.1109/TPEL.2011.2172000.

- [8] Q. Zhang, X.-D. Sun, Y.-R. Zhong, M. Matsui, and B.-Y. Ren, "Analysis and Design of a Digital Phase-Locked Loop for Single-Phase Grid-Connected Power Conversion Systems," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 8, pp. 3581–3592, Aug. 2011, doi: 10.1109/TIE.2010.2087295.

- [9] J. Pinto, A. Carvalho, A. Rocha, and A. Araújo, "Comparison of DSOGI-based PLL for phase estimation in three-phase weak grids," *Electricity*, vol. 2, no. 3, pp. 244–270, Jul. 2021, doi: 10.3390/electricity2030015.

- [10] A. A. Nazib, D. G. Holmes, and B. P. McGrath, "Decoupled DSOGI-PLL for improved three phase grid synchronisation," in 2018 International Power Electronics Conference (IPEC-Niigata 2018 -ECCE Asia), IEEE, May 2018, pp. 3670–3677. doi: 10.23919/IPEC.2018.8507364.

- [11] J. Matas, M. Castilla, J. Miret, L. Garcia de Vicuna, and R. Guzman, "An adaptive prefiltering method to improve the speed/accuracy tradeoff of voltage sequence detection methods under adverse grid conditions," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 5, pp. 2139–2151, May 2014, doi: 10.1109/TIE.2013.2274414.

- [12] S. Prakash, J. K. Singh, R. K. Behera, and A. Mondal, "A type-3 modified SOGI-PLL with grid disturbance rejection capability for single-phase grid-tied converters," *IEEE Transactions on Industry Applications*, vol. 57, no. 4, pp. 4242–4252, Jul. 2021, doi: 10.1109/TIA.2021.3079122.

- [13] X. Wang, "Optimization strategy of DSOGI-PLL precision under harmonic interference conditions," in 2020 IEEE Sustainable Power and Energy Conference (iSPEC), IEEE, Nov. 2020, pp. 852–857. doi: 10.1109/iSPEC50848.2020.9351264.

- [14] S. Janardhanan and M. A. Mulla, "Power quality enhancement and DC offset rejection in PV-DVR system using ESOGI-based control," *Electrical Engineering*, vol. 107, no. 7, pp. 8787–8802, Jul. 2025, doi: 10.1007/s00202-024-02455-z.

- [15] J. S. Lee and S.-H. Hwang, "DC offset error compensation algorithm for PR current control of a single-phase grid-tied inverter," *Energies*, vol. 11, no. 9, p. 2308, Sep. 2018, doi: 10.3390/en11092308.

- [16] A. Kulkarni and V. John, "Design of synchronous reference frame phase-locked loop with the presence of dc offsets in the input voltage," *IET Power Electronics*, vol. 8, no. 12, pp. 2435–2443, Dec. 2015, doi: 10.1049/iet-pel.2014.0878.

- [17] "IEEE standard for interconnection and interoperability of distributed energy resources with associated electric power systems interfaces." IEEE, Piscataway, NJ, USA, Feb. 15, 2018. doi: 10.1109/IEEESTD.2018.8332112.

- [18] A. Kulkarni and V. John, "Mitigation of lower order harmonics in a grid-connected single-phase PV inverter," *IEEE Transactions on Power Electronics*, vol. 28, no. 11, pp. 5024–5037, Nov. 2013, doi: 10.1109/TPEL.2013.2238557.

- [19] Q. Shi, H. Hu, W. Xu, and J. Yong, "Low-order harmonic characteristics of photovoltaic inverters," *International Transactions on Electrical Energy Systems*, vol. 26, no. 2, pp. 347–364, Feb. 2016, doi: 10.1002/etep.2085.

[20] I. Daut, S. Hasan, S. Taib, R. Chan, and M. Irwanto, "Harmonic content as the indicator of transformer core saturation," in 2010 4th International Power Engineering and Optimization Conference (PEOCO), IEEE, Jun. 2010, pp. 382–385. doi: 10.1109/PEOCO.2010.5559192.

- [21] D. Wang, L. Yang, and L. Ni, "Performance and harmonic detection algorithm of phase locked Loop for parallel APF," Energy Informatics, vol. 7, no. 1, Dec. 2024, doi: 10.1186/s42162-024-00325-3.

- [22] S.-H. Hwang, L. Liu, H. Li, and J.-M. Kim, "DC offset error compensation for synchronous reference frame PLL in single-phase grid-connected converters," *IEEE Transactions on Power Electronics*, vol. 27, no. 8, pp. 3467–3471, 2012, doi: 10.1109/TPEL.2012.2190425.

- [23] S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Three-phase PLLs: A review of recent advances," *IEEE Transactions on Power Electronics*, vol. 32, no. 3, pp. 1894–1907, Mar. 2017, doi: 10.1109/TPEL.2016.2565642.

- [24] Hyeong-Jin Choi, Seung-Ho Song, Seung-Gi Jeong, Ju-Yeop Choi, and Ick Choy, "Design of SRD-F-PLL system with consideration of low-pass filter for high dynamic performance during voltage disturbance," in 2009 IEEE 6th International Power Electronics and Motion Control Conference, IEEE, May 2009, pp. 720–724. doi: 10.1109/IPEMC.2009.5157479.

- [25] T. Tarasiuk et al., "Review of power quality issues in maritime microgrids," IEEE Access, vol. 9, pp. 81798–81817, 2021, doi: 10.1109/ACCESS.2021.3086000.

- [26] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A new single-phase PLL structure based on second order generalized integrator," in 2006 37th IEEE Power Electronics Specialists Conference, IEEE, Jun. 2006, pp. 1–6. doi: 10.1109/pesc.2006.1711988.

#### **BIOGRAPHIES OF AUTHORS**

Ilias En-Naoui is a Ph.D. student, received his master's degree in electrical engineering from the Faculty of Science and Technology Settat in 2019, and he is currently a professor of electrical engineering in the agrégation cycle at the Ministry of National Education, Morocco. His research areas include power electronics, renewable energy, and power quality. Laboratory of Radiation-Matter and Instrumentation (RMI), Faculty of Sciences and Technology, Hassan 1st University, Morocco. He can be contacted at email: i.ennaoui@uhp.ac.ma.

Abdelhadi Radouane was born in 1969. He received the Agrégation degree in Electrical Engineering from the ENSET of Rabat, Morocco, in 1996. In 2017, he obtained a Ph.D. in automatic control. Since 2018, he joined the FST Settat, Hassan First University of Settat, Morocco, as an assistant professor. He can be contacted at email: abdelhadi.radouane@uhp.ac.ma.

Azeddine Mouhsen be sorn in 10 July 1967. He has been a professor of physics at Hassan First University, Morocco, since 1996. He holds a Ph.D. from Bordeaux I University (France) in 1995 and a thesis from Moulay Ismail University, Morocco, in 2001. He specializes in instrumentation and measurements, sensors, energy transfer, and radiation-matter interactions. He has taught courses in physical sensors, chemical sensors, instrumentation, systems technology, digital electronics, and industrial data processing. Actually, he is the Director of the Laboratory of Radiation-Matter and Instrumentation. He can be contacted at email: az.mouhsen@gmail.com.

Hamid Yantour be soon in 1964, received the master's degree in automatic, signal processing, and Industrial Computing (ATSII) from Hassan 1st University, Morocco in 2011. He obtained a Ph.D. in Automatic and Production in 2016. Currently, he is a professor of Electrical Engineering at the Regional Center for Education and Training Professions (CRMEF) in Settat. He can be contacted at email: yantourhamid@gmail.com.