# Interleaved buck converter using a floating dual seriescapacitor topology

## Chan Viet Nguyen, Dang Tai Nguyen, Thanh Phuong Ho

Faculty of Electrical and Electronics Engineering, Ho Chi Minh City University of Technology (HCMUT), Vietnam National University (VNU), Ho Chi Minh, Vietnam

## **Article Info**

## Article history:

Received Jun 29, 2025 Revised Sep 19, 2025 Accepted Oct 17, 2025

## Keywords:

Buck converter Current balancing Floating structure High conversion ratio Interleaved Non-isolated converter Series capacitor

## **ABSTRACT**

Interleaved buck converters (IBC) are widely utilized in step-down voltage applications due to their excellent performance and straightforward design. However, conventional IBCs require individual current sensors and feedback control circuits to maintain phase current balance, resulting in increased cost and design complexity. In this paper, a novel floating dual series capacitor (FDSC) converter based on an interleaved floating structure is proposed. The most distinctive aspect of this proposed converter is its ability to naturally balance the four inductor currents without the need for any current sensors or feedback control. Furthermore, the proposed converter also exhibits lower voltage stress on switching devices and inductors, contributing to improved efficiency and a reduction in overall magnetic volume. To validate the performance characteristics of the proposed converter, a 1.3 kW prototype of the FDSC topology was developed and tested to indicate the analytical results and demonstrate stable current balance even under different operating conditions. The experimental validation highlights the topology's suitability for high step-down, compact, and efficient applications such as EV auxiliary power supply and voltage regulator modules.

This is an open access article under the <u>CC BY-SA</u> license.

# Corresponding Author:

Chan Viet Nguyen

Faculty of Electrical and Electronics Engineering, Ho Chi Minh City University of Technology (HCMUT) Vietnam National University (VNU)

268 Ly Thuong Kiet Street, Ward 14, District 10, Ho Chi Minh 70000, Vietnam

Email: ncviet@hcmut.edu.vn

## 1. INTRODUCTION

Electric vehicles (EVs) have gained significant popularity in today's market. These vehicles typically operate using high-voltage battery packs, commonly at 400 V or even up to 800 V, to deliver the necessary power for propulsion. Despite this, low-voltage lead-acid batteries are still employed to supply energy to the vehicle's control and infotainment systems, primarily due to their proven reliability [1]. However, lead-acid batteries pose environmental hazards and are increasingly inadequate in meeting the rising energy demands of modern, feature-rich EV systems. As a result, extensive research is being conducted to develop power converters capable of stepping down high-voltage battery output directly to low-voltage levels, aiming to eliminate the need for traditional auxiliary batteries in electric vehicles [2], [3].

Step-down conversion using transformers is widely employed, especially in applications requiring electrical isolation or large voltage conversion ratios. Transformer-based topologies, such as flyback and forward converters, offer flexibility in design and are well-suited for high-voltage or isolated systems. However, in certain scenarios particularly when isolation is not required and the voltage step-down ratio is moderate direct step-down converters like the buck topology provide superior efficiency, reduced component

count, and lower cost [4]–[6]. As a result, direct conversion methods remain a favorable choice in compact, low-to-medium power applications.

The buck converter is a widely used non-isolated topology that efficiently steps down the input voltage to a lower output level. The presence of an output inductor in this topology ensures continuous output current, which is a critical feature in DC/DC converters. To enhance output power, interleaved buck converters (IBC) are widely used. IBC is constructed by combining conventional buck converters in parallel using interleaved switching [7]–[10]. The interleaving effect significantly reduces output current fluctuations. This enables a smaller L-C filter and faster dynamic response [11], [12]. However, even a slight mismatch in gate signals between buck converters can lead to unbalanced inductor currents in the IBC. These studies attempt to address the issue of current imbalance among inductors; however, they require additional current sensors and more complex control methods [13]–[16]. Buck converter achieves high efficiency when the output voltage is not significantly lower than the input voltage. However, as the voltage conversion ratio increases, the efficiency of the converter declines markedly. Moreover, all switches and diodes in the IBC must withstand the high input voltage, resulting in significant switching loss when operating at high frequencies [17]–[20]. Consequently, for applications demanding large voltage step-down ratios, alternative converter topologies with superior conversion capabilities are typically preferred.

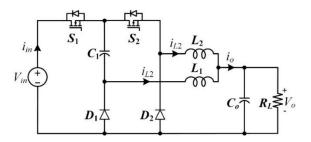

The series capacitor (SC) converter as shown in Figure 1 and presented in [21], [22] offers solutions to the issues faced by the IBC. To begin with, the SC converter has twice the voltage gain while imposing lower voltage stress on the semiconductor devices. Specifically, the voltage stress on switch  $S_2$ , diodes  $D_1$  and  $D_2$  is only  $V_{in}/2$ . This is achieved because the capacitor  $C_1$  is withstanding half of the input voltage, which is  $V_{in}/2$ . Secondly, due to the charge-discharge equilibrium of capacitor  $C_1$ , the current flowing through the two inductor  $L_1$  and  $L_2$  is inherently balanced. However, the aforementioned advantage is only realized when the duty cycle is less than 0.5 [23]. In fact, when the duty cycle exceeds 0.5, the voltage stress on the switching devices increases significantly, and the function of balancing inductor currents is lost [24], [25]. Chen *et al.* [26] attempted to enhance the performance of the conventional SC converter by proposing a multiphase SC configuration. However, the main drawback of this approach is that as the number of phases increases, the operating range becomes more restricted, since the maximum duty cycle is limited to 1/n, where n is the number of phases.

Figure 1. Series capacitor (SC) converter

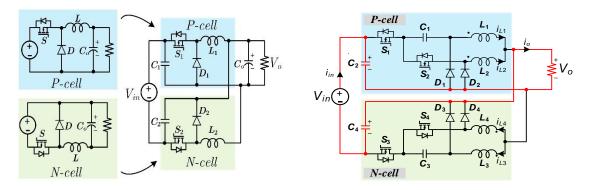

Several studies have instead explored the interleaved floating (IF) structure [26]–[28], which connects two complementary cells of a converter in a floating-input, parallel-output manner. This configuration maintains current balance between phases while achieving a higher conversion ratio, without further narrowing the operating range of the converter. However, for successful interconnection, the configured connection must include both N-cell and P-cell types, as illustrated in Figure 2. Notably, these two converter types exhibit identical electrical characteristics. Forest *et al.* [29] sought to enhance the capacity by extending the IF structure to four phases. However, the phase currents were not inherently balanced, requiring additional current sensors and feedback loops.

In this paper, a floating dual series capacitor (FDSC) converter based on an interleaved floating structure is proposed, as illustrated in Figure 3. The converter is developed by integrating SC cells into an interleaved floating structure to achieve a higher conversion ratio and increase the output power. The proposed converter is engineered to maximize voltage gains and minimize voltage stress on the switching devices, resulting in reduced switching losses and improved efficiency, especially in high conversion ratio applications. Moreover, the proposed converter also has the current balancing feature that naturally equalizes the currents in the four inductors without requiring feedback control or sensing circuits.

Figure 2. Interleaved floating (IF) structure

Figure 3. The proposed FDSC converter

## 2. OPERATION OF THE NOVEL CONVERTER

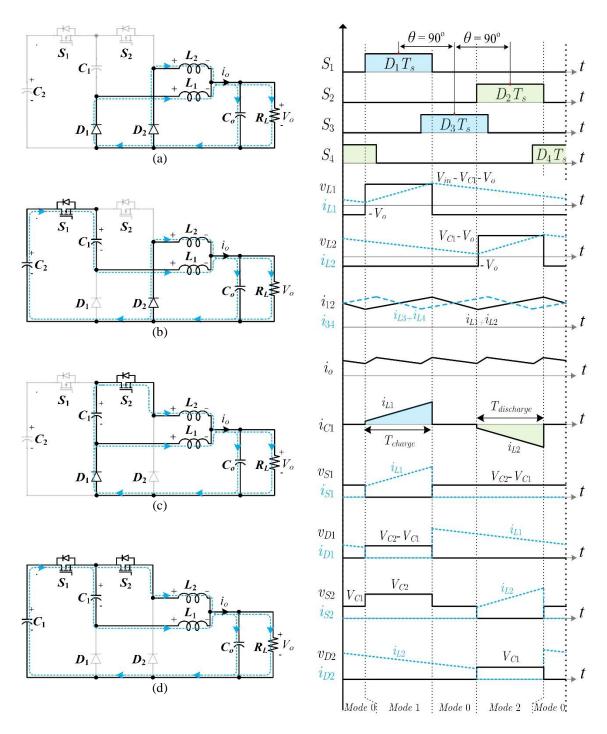

The proposed FDSC converter, shown in Figure 3, is built by connecting two SC converters called the P-cell and N-cell with floating inputs and parallel outputs. The four operating modes of the FDSC converter are illustrated in Figure 4 and their key waveforms are shown in Figure 5. As illustrated in Figure 5, both cells use the same gate driving signals, but with a  $90^{\circ}$  phase shift. As the voltage and current waveforms of the P-cell and N-cell are identical, only the representative waveforms of the P-cell are shown for clarity. Furthermore, due to the inherent limitations of the SC converter, the duty cycle of the FDSC is restricted to D < 0.5 in this study.

[Mode 0, Figure 4(a)]: All the switches are turned off while all the diodes are turned on. The current flows through the load by the loops  $L_1$ - $V_0$ - $D_1$  and  $L_2$ - $V_0$ - $D_2$ . The two capacitors  $C_2$  and  $C_4$  are charged through the loop  $V_{in}$ - $C_2$ - $V_0$ - $C_4$ . The instantaneous voltage across each inductor is equal to - $V_0$ . Therefore, the inductor currents  $i_{L1}$  and  $i_{L2}$  decrease in this mode.

$$\begin{cases}

V_{L1} = -V_0 \\

V_{L2} = -V_0

\end{cases}$$

(1)

[Mode 1, Figure 4(b)]:  $S_1$  and  $D_2$  are turned on while  $S_2$  and  $D_1$  are turned off. In this mode, capacitor  $C_1$  is charged from  $C_2$  with a current equal to  $i_{L1}$  flowing through the loop  $S_1$ - $C_1$ - $L_1$ - $V_o$ - $C_2$ . The inductor  $L_2$  continues discharging through the loop  $L_2$ - $V_o$ - $D_2$ . In this mode, the voltage across  $L_1$  is positive, while that across  $L_2$  is negative. The inductor voltage can be expressed as:

[Mode 2, Figure 4(c)]:  $S_2$  and  $D_1$  are turned on while  $S_1$  and  $D_2$  are turned off. The capacitor  $C_1$  discharges through the loop  $C_1$ - $S_2$ - $L_2$ - $V_o$ - $D_1$ , delivering a current equal to  $i_{L2}$ . The current of inductor  $L_1$  circulates through the loop  $L_1$ - $V_o$ - $D_1$ . In contrast to Mode 1, the voltage across  $L_1$  becomes negative while that across  $L_2$  becomes positive, as shown (3).

$$\begin{cases} V_{L1} = -V_o \\ V_{L2} = V_{C1} - V_o \end{cases} \tag{3}$$

[Mode 3, Figure 4(d)]: All the diodes are turned off while all the switches are turned on. The current flows through the load by the loops  $L_1$ - $V_0$ - $C_2$ - $S_1$ - $C_1$  and  $L_2$ - $V_0$ - $C_2$ - $S_1$ - $S_2$ . The two capacitors  $C_2$  and  $C_4$  are charged through the loop  $V_{in}$ - $C_2$ - $V_0$ - $C_4$ . The inductor currents  $i_{L1}$  and  $i_{L2}$  increase in this mode. In this mode, the voltage across both inductors is positive. The inductor voltages can be expressed as:

$$\begin{cases}

V_{L1} = V_{C2} - V_{C1} - V_{o} \\

V_{L2} = V_{C2} - V_{o}

\end{cases}$$

(4)

In the FDSC converter, capacitor  $C_1$  acts as an intermediate energy storage element: it stores energy by charging in series with inductor  $L_1$  during Mode 1 and releases this energy to  $L_2$  during Mode 2. Thus, the energy delivered to  $L_1$  and  $L_2$  is precisely the energy exchanged in capacitor  $C_1$ .

ISSN: 2088-8694

Figure 4. Operation modes of *the* P-cell SC converter: (a) mode 0, (b) mode 1, (c) mode 2, and (d) mode 3

Figure 5. Key waveforms of the proposed converter

# 3. CHARACTERISTICS OF THE FDSC CONVERTER

## 3.1. Voltage gain

When D < 0.5, the durations of Mode 1 and Mode 2 are equal, each lasting  $DT_s$ . Mode 0 operates for (1-2D)  $T_s$ . The voltages of inductors  $L_1$  and  $L_2$ , denoted as  $v_{L1}$  and  $v_{L2}$ , are illustrated in Figure 5. It can be observed that, within each switching cycle, the inductor voltage alternates between positive and negative intervals. According to the flux (volt–sec) balance condition, the average inductor voltage over one switching period must be zero. In other words, the area of the positive portion (voltage × time) must be equal to that of the negative portion. Therefore, the voltage across the two inductors can be expressed as (5).

$$\begin{cases} V_{L1_{Mode 1}} DT_s = -V_{L1_{Mode 0}} (1 - 2D) T_s - V_{L1_{Mode 2}} DT_s \\ V_{L2_{Mode 2}} DT_s = -V_{L2_{Mode 0}} (1 - 2D) T_s - V_{L2_{Mode 1}} DT_s \end{cases}$$

(5)

By substituting (1)–(4) into (5), the voltages across  $C_1$  and  $C_2$  are obtained.

$$\begin{cases} V_{C1} = \frac{V_o}{D} \\ V_{C2} = \frac{2V_o}{D} \end{cases} \qquad 0 < D \le 0.5$$

(6)

The voltage across  $C_1$  is always half of that across  $C_2$ . Consequently,  $C_1$  blocks half of the switch voltage during operation, thereby reducing voltage stress on the switching devices. Since the properties of the N-cell and P-cell SC are identical, the voltages across  $C_3$  and  $C_4$  correspond to those of  $C_1$  and  $C_2$ , respectively. From the  $V_{in}$ – $C_2$ – $V_o$ – $C_4$  loop shown in Figure 3 (red loop), the output voltage of the proposed FDSC converter is obtained as (7).

$$V_o = V_{C2} + V_{C4} - V_{in} (7)$$

Based on (6) and (7), and considering the symmetry between the P-cell and N-cell, it leads to  $V_{C2} = V_{C4}$ ,  $V_{C1} = V_{C3}$ . The output voltage of the proposed converter can be expressed as (8).

$$V_o = \frac{DV_{in}}{(4-D)} \tag{8}$$

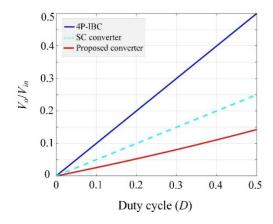

From (8), it is evident that the FDSC converter can step down a large input voltage to a much smaller output voltage with a very high conversion ratio, exceeding 7 times. In contrast, achieving the same ratio with a conventional buck converter would require an extremely small duty cycle. Figure 6 compares the voltage gain of the proposed converter with that of a conventional buck converter, showing that the FDSC consistently achieves a higher conversion ratio at the same duty cycle. It is also well known that the efficiency of step-down converters decreases significantly when the duty cycle becomes extremely low. By attaining a high conversion ratio without resorting to such low duty cycles, the proposed converter offers superior suitability for high step-down applications compared with conventional designs

# 3.2. Inductor current balancing

As shown in Figure 5, the charge and discharge time of the proposed converter are equal to  $DT_s$ . Following the charge balance condition for capacitor  $C_1$ , the charge and discharge areas of capacitor  $C_1$  must be equal. Moreover, the capacitor  $C_1$  is charged and discharged by  $i_{L1}$  and  $i_{L2}$ , respectively. Therefore, the average current of  $L_1$  and  $L_2$  are equal. It is similar for  $I_{L3}$  and  $I_{L4}$ .

As mentioned in Forest *et al.* [29], the two cells of the proposed converter are also naturally balanced by the special input floating output parallel structure. Thus, the four average inductor currents in the proposed converter are given by:

$$I_{L1} = I_{L2} = I_{L3} = I_{L4} = \frac{I_0 + I_{in}}{4} \tag{9}$$

As indicated by (9), the converter inherently maintains balanced inductor current without requiring any supplementary sensors or control algorithms, thereby simplifying the system and ensuring power equilibrium.

## 3.3. Inductor current ripples of the proposed converter

From inductor current waveforms in Figure 5, the inductor current ripple of  $L_1$  to  $L_4$  can be given as (11).

$$\Delta i_{L1-4} = \frac{V_o}{Lf_{SW}} (1 - D) \tag{11}$$

where: L is the inductance of inductors  $L_1$ – $L_4$ . These inductors are normally selected with equal values to ensure optimal interleaving performance.  $f_{sw}$  is the switching frequency of the converter. To achieve the best interleaving effect, the phase currents of the converter must be equal in magnitude and evenly phase-shifted [30], [31]. In the case of the proposed FDSC converter, which operates with four phases, the phase shift between adjacent phases is 90°. The output current ripple of the proposed converter can be expressed as:

П

$$\Delta i_o = \begin{cases} \frac{(1-4D)V_o}{Lf_{SW}} & 0 < D \le 0.25\\ \frac{(1-2D)(4D-1)V_o}{2DLf_{SW}} & 0.25 < D \le 0.5 \end{cases}$$

(12)

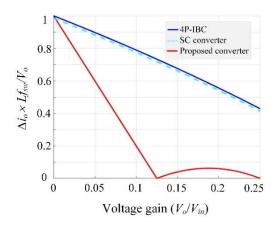

Figure 7 illustrates the output current ripple of the proposed converter in comparison with that of the four-phase interleaved buck converter (4P-IBC). Both converters are evaluated under identical conditions, including the same conversion ratio and inductor value. It is observed that the proposed converter exhibits a significantly lower output current ripple than the 4P-IBC. This improvement is attributed to the fact that the voltage across the inductor in the proposed topology is lower than that in a conventional 4P-IBC. Consequently, the FDSC converter allows for a reduction in both the inductance  $L_{1-4}$  and the output capacitance  $C_0$ , thereby enhancing the dynamic response of the system.

Figure 6. Voltage gain of the 4P-IBC, SC, and proposed converter

Figure 7. Output current ripple of the 4P-IBC, SC, and proposed converter

## 3.4. The converter characteristics

Table 1 provides a comprehensive comparison between the proposed FDSC and other converters, including the four-phase interleaved buck converter (4P-IBC), the series capacitor (SC) converter, and the coupled-inductor buck (CIB) converter. In terms of operating range, the proposed FDSC is restricted to duty cycles below 0.5, which is narrower than that of the other converters. Nevertheless, this limitation is offset by several remarkable advantages. Specifically, the FDSC exhibits the lowest voltage stress on semiconductor devices, ensuring improved efficiency. Moreover, it inherently achieves self-balancing of the output voltages across all four phases without requiring additional control circuits. Beyond that, the proposed topology attains the highest conversion ratio among the compared configurations, while simultaneously producing the smallest output voltage ripple, making it highly attractive for high step-down, high-efficiency applications.

Table 1. Comparison between the FDSC and other converters

| Table 1. Comparison between the FDSC and other converters |                         |           |                    |           |  |  |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------|-----------|--------------------|-----------|--|--|--|--|--|--|--|

| Converters                                                | FDSC                    | 4P-IBC    | SC                 | CIB       |  |  |  |  |  |  |  |

|                                                           | (Proposed converter)    | (**)      | (**)               | (**)      |  |  |  |  |  |  |  |

| Duty cycle (D)                                            | $0 < D \le 0.5$         | 0 < D < 1 | $0 < D \le 0.5$    | 0 < D < 1 |  |  |  |  |  |  |  |

| Voltage stress (*) $S_1, S_3$                             | $\frac{V_{in}}{(4-D)}$  | $V_{in}$  | $\frac{V_{in}}{2}$ | $V_{in}$  |  |  |  |  |  |  |  |

| $S_2, S_4$                                                | $\frac{2V_{in}}{(4-D)}$ | $V_{in}$  | $V_{\it in}$       | $V_{in}$  |  |  |  |  |  |  |  |

| $D_1,D_3$                                                 | $\frac{V_{in}}{(4-D)}$  | $V_{in}$  | $\frac{V_{in}}{2}$ | $V_{in}$  |  |  |  |  |  |  |  |

| $D_2,D_4$                                                 | $\frac{V_{in}}{(4-D)}$  | $V_{in}$  | $\frac{V_{in}}{2}$ | $V_{in}$  |  |  |  |  |  |  |  |

| Voltage gain $\left(\frac{V_o}{V_{in}}\right)$            | $\frac{D}{(4-D)}$       | D         | $\frac{D}{2}$      | D         |  |  |  |  |  |  |  |

| Output current ripple ( $\Delta i_o$ )                    | Lowest                  | Medium    | High               | Low       |  |  |  |  |  |  |  |

| Current balancing                                         | Yes                     | No        | Yes                | No        |  |  |  |  |  |  |  |

\*note: In both SC and CIB, only the devices  $S_1$ ,  $S_2$ ,  $D_1$ , and  $D_2$  are present; \*\*4P-IBC: Four phase interleaved buck converter; SC: Series capacitor converter; CIB: Coupled inductor buck converter

### 4. EXPERIMENTAL VERIFICATION

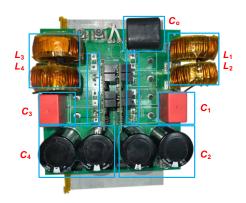

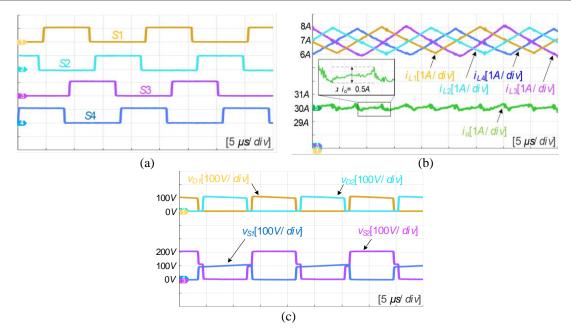

A 1.3 kW FDSC converter, as shown in Figure 8, was built and tested. The experimental results are shown in Figures 9–12 and the converter parameters are presented in Table 2. The converter was designed to work over a wide input voltage range (from 300 to 450 V) while the output voltage was controlled at 45 V. The gate signals of  $S_1$  to  $S_4$  are shifted by 90°.

Figure 8. The prototype of FDSC converter

Table 2. Experimental parameters

| Tuote 2. Emperimental parameters |                  |                               |              |  |  |  |  |  |  |  |

|----------------------------------|------------------|-------------------------------|--------------|--|--|--|--|--|--|--|

| Symbol                           | Value            | Symbol                        | Value        |  |  |  |  |  |  |  |

| $V_{in}/V_o$                     | 300 - 450 V/45 V | $C_1, C_3$                    | $4.4 \mu F$  |  |  |  |  |  |  |  |

| $P_{out}$                        | 1.3~kW           | $C_2$ , $C_4$                 | $100  \mu F$ |  |  |  |  |  |  |  |

| $f_{sw}$                         | 55 kHz           | $L_1$ , $L_2$ , $L_3$ , $L_4$ | $250 \mu H$  |  |  |  |  |  |  |  |

| $S_1 - S_4$                      | SCT3060AR        | $D_1\!\!-\!\!D_4$             | SCS320AM2    |  |  |  |  |  |  |  |

Figure 9 shows the experimental waveforms of inductor currents ( $i_{L1}$ ,  $i_{L2}$ ,  $i_{L3}$ , and  $i_{L4}$ ) and semiconductor device voltages ( $v_{S1}$ ,  $v_{D1}$ ,  $v_{S2}$ , and  $v_{D2}$ ) at (D=0.45,  $V_{in}=360$  V,  $V_o=45$  V, and  $P_o=1.3$  kW). The gate driving signals are shown in Figure 9(a). Owing to the self-balancing capability of the FDSC configuration, the phase currents remain balanced even without the use of sensors or feedback control. As illustrated in Figure 9(b), the four inductor currents are well balanced, with a ripple of approximately 25% (about 2 A). Furthermore, the interleaving effect of the four phases significantly reduces the output current ripple to about 0.5 A. This low ripple allows optimization of the phase inductor values and the output capacitor reactance during the design stage, thereby enhancing the dynamic response of the converter. Figure 9(c) also shows the voltage stresses of switches  $S_1$  and  $S_2$  are 100 V and 200 V, respectively. The voltage stresses of diodes  $D_1$  and  $D_2$ , are 100 V. The same also applies to switches  $S_3$ ,  $S_4$  and diodes  $D_3$ ,  $D_4$ , since the FDSC structure consists of symmetrical P-cell and N-cell configurations. Compared with the conventional 4P-IBC, in which the switching devices experience the full input voltage ( $V_{in} \approx 360$  V), the proposed converter significantly reduces the voltage stress on the switches. This reduction directly contributes to improved conversion efficiency.

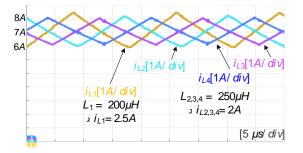

An additional experiment was conducted to examine the effect of inductance mismatch, as shown in Figure 10. In this case, the inductor  $L_1$  was deliberately reduced to  $200 \,\mu H$ , compared to  $250 \,\mu H$  for the remaining inductors. It can be seen that although the ripple of  $i_{L1}$  is larger than that of the other inductors, the average current values across all four inductors remain equal. This demonstrates that the current-balancing capability of the FDSC configuration is independent of the inductor values.

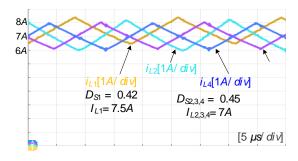

Another similar experiment was conducted, Figure 11, illustrating the waveforms of four currents in the FDSC circuit under conditions where the gate driving signal are intentionally mismatched. The gate signal for  $S_1$  was deliberately altered ( $D_{S1} = 0.42$  and  $D_{S2} = D_{S3} = D_{S4} = 0.45$ ), the four inductor currents are still balanced. To clarifying a point of here that the inductor current balancing function does not mean all the inductor currents must be perfect equal, so it can be observed that the average values of the currents  $i_{L1} - i_{L4}$  show some deviation  $i_{L1}$  reaches 7.5 A while  $i_{L2}$ ,  $i_{L3}$ , and  $i_{L4}$  are at 7 A. As long as the inductor currents are not "losing control" which could lead to degraded performance or potential damage to circuit components, a little mismatch in the inductor currents is still acceptable. It should also be noted that in practical applications, a duty cycle deviation of 0.03 is relatively significant.

Figure 9. Experimental waveforms when D = 0.45,  $V_{in} = 360$  V,  $V_o = 45$  V,  $P_o = 1300$  W: (a) gate signals, (b) inductor current and output current, and (c) diode voltage and switch voltage

Figure 10. Experimental waveforms of the FDSC converter when have a mismatch of the inductance value ( $L_1 = 200 \ \mu H$ ,  $L_2 = L_3 = L_4 = 250 \ \mu H$ )

Figure 11. Experimental waveforms of the FDSC converter with a mismatch of the gate signal  $(D_{S1} = 0.42 \text{ and } D_{S2} = D_{S3} = D_{S4} = 0.45)$

Figure 12. Dynamic response of the FDSC converter under step load

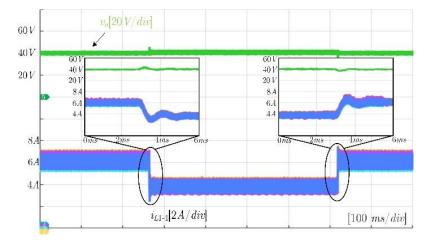

The dynamic response of the FDSC converter under step load conditions is presented in Figure 12. In this test, the load is varied between 70% (900 W) and 40% (500 W). Despite the absence of current feedback, the inductor currents  $i_{L1}-i_{L4}$  remain well balanced, with only a minor overshoot. The output voltage exhibits slight fluctuations, but without significant deviation. Notably, the converter requires only 1 ms to fully settle and restore steady operation.

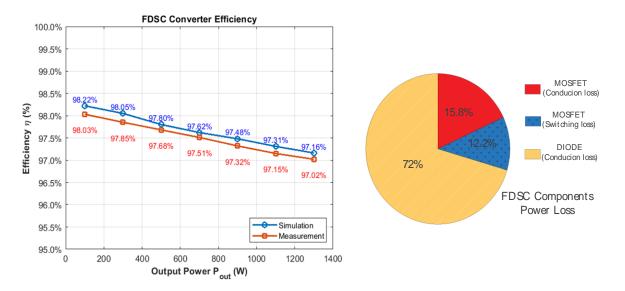

Figure 13 presents the efficiency of the FDSC converter, validated through both simulation and experimental results. The proposed topology demonstrates excellent performance, achieving an efficiency greater than 97% at full load. As the simulation does not account for inductor losses and circuit conduction losses, its reported efficiency is slightly higher than that observed experimentally. Figure 14 further illustrates the loss distribution, indicating that the majority approximately 72% originates from the conduction losses of diodes  $D_1$ – $D_4$ . This observation suggests that the efficiency could be further enhanced by replacing the diodes with active switches, similar to those employed in a synchronous buck converter.

Figure 13. The efficiency of the proposed FDSC converter

Figure 14. Power loss distribution of semiconductor devices in the FDSC converter

## 5. CONCLUSION

This paper proposed an FDSC converter for high conversion ratio DC–DC applications. Compared with the conventional 4P-IBC, the proposed converter achieves natural current balancing without additional sensing or control circuits, provides a higher voltage gain, and reduces voltage stress on semiconductor devices. These advantages make it suitable for applications such as EV auxiliary power supply and voltage regulator modules, where wide voltage ranges and high current capability are required. A detailed analysis was carried out and the experimental prototype at 1.3 kW validated the theoretical findings. Although the duty-cycle limitation still constrains the operating range, future work will focus on PWM scheme and design improvements to address this issue. In conclusion, the proposed FDSC converter demonstrates high efficiency, intrinsic current sharing, and practical feasibility, highlighting its potential for next-generation low-voltage, high-current power converter.

## **ACKNOWLEDGEMENTS**

This research is funded by Vietnam National University Ho Chi Minh City (VNU-HCM) under grant number C2024-20-38.

## **AUTHOR CONTRIBUTIONS**

This journal uses the Contributor Roles Taxonomy (CRediT) to recognize individual author contributions, reduce authorship disputes, and facilitate collaboration

| Name of Author   | C            | M            | So | Va           | Fo | I            | R | D            | 0            | E            | Vi | Su           | P            | Fu           |

|------------------|--------------|--------------|----|--------------|----|--------------|---|--------------|--------------|--------------|----|--------------|--------------|--------------|

| Chan Viet Nguyen | ✓            | ✓            | ✓  | ✓            | ✓  | ✓            |   | ✓            | ✓            |              |    | ✓            | ✓            |              |

| Dang Tai Nguyen  |              | $\checkmark$ | ✓  |              |    | $\checkmark$ | ✓ | $\checkmark$ | $\checkmark$ | $\checkmark$ | ✓  | $\checkmark$ |              |              |

| Thanh Phuong Ho  | $\checkmark$ |              | ✓  | $\checkmark$ |    |              |   |              |              | $\checkmark$ | ✓  |              | $\checkmark$ | $\checkmark$ |

Fo: Formal analysis E: Writing - Review & Editing

## CONFLICT OF INTEREST STATEMENT

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

### **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### REFERENCES

- S. Cha, J. Shin, M. Jung, Y. Kim, J. Kwon, and C. Lee, "Applicability of electric vehicle lv auxiliary battery for emergency use," in 2022 IEEE Transportation Electrification Conference & Expo (ITEC), Anaheim, CA, USA, Jun. 2022, pp. 291–296.

- [2] B. Gao, Z. Wang, J. Zhang, Z. Liu, W. Zhang, and C. Liu, "An integrated electric vehicle charging system of wireless power transfer and auxiliary power module with shared converter and magnetic coupler," *IEEE Transactions on Power Electronics*, vol. 39, no. 2, pp. 1987–2001, Feb. 2024.

- [3] L. He, X. Tang, J. Zhang, and C. C. Mi, "Seamless switching technology for low voltage charging in 800v electric vehicle systems," *Journal of Design and General Automotive Engineering*, vol. 6, no. 1, pp. 17–26, Mar. 2024.

- [4] L. Šebest, V. Benda, A. Vojtěch, and T.-J. Lee, "An experimental review of step-down converter topologies with wide input voltage range for modern vehicle low-power systems," *Electronics*, vol. 14, no. 9, May 2023.

- [5] M. S. Islam, M. A. Rahman, M. S. Alam, M. A. Hossain, and M. A. Razzak, "Step-down dc-dc converters: an overview and outlook," *Electronics*, vol. 11, no. 11, Jun. 2022.

- [6] R. W. Erickson, "DC-dc power converters," in Wiley Encyclopedia of Electrical and Electronics Engineering, John Wiley & Sons, 2007.

- [7] M. Sinha, J. Poon, B. B. Johnson, M. Rodriguez, and S. V. Dhople, "Decentralized interleaving of parallel-connected buck converters," IEEE Transactions on Power Electronics, vol. 34, no. 5, pp. 4993–5006, Jun. 2019, doi: 10.1109/TPEL.2018.2868756.

- [8] O. García, P. Zumel, A. de Castro, and J. A. Cobos, "Automotive de-de bidirectional converter made with many interleaved buck stages," *IEEE Transactions on Power Electronics*, vol. 21, no. 3, pp. 578–586, May 2006, doi: 10.1109/TPEL.2006.872379.

- [9] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "Design considerations for high-voltage high-power full-bridge zero-voltage-switched pwm converter," *Conference Proceedings IEEE Applied Power Electronics Conference and Exhibition APEC*, vol. 7, no. 4, pp. 275–284, Oct. 1990, doi: 10.1109/apec.1990.66420.

- [10] M. Jovanovic and Y. Jang, "Interleaved boost converter with intrinsic voltage gain and improved efficiency," *IEEE Transactions on Power Electronics*, vol. 22, no. 1, pp. 136–143, Jan. 2007.

- [11] T. R. Granados-Luna et al., "Two-phase, dual interleaved buck-boost dc-dc converter for automotive applications," IEEE Transactions on Industry Applications, vol. 56, no. 1, pp. 390–402, 2020, doi: 10.1109/TIA.2019.2942026.

- [12] J. Kudtongngam, K. Sangkarak, P. Lopattanakij, P. Liutanakul, and V. Chunkag, "Implementation of automatic interleaving and load current sharing techniques using single interleaving bus," *IET Power Electronics*, vol. 9, no. 7, pp. 1496–1504, Jun. 2016, doi: 10.1049/iet-pel.2015.0575.

- [13] M. O. Younsi, M. Bendali, T. Azib, C. Larouci, C. Marchand, and G. Coquery, "Current-sharing control technique of interleaved buck converter for automotive application," 7th IET International Conference on Power Electronics, Machines and Drives, PEMD 2014, vol. 5, no. 2, pp. 123–130, 2014.

- [14] A. M. Milasi, R. M. Milasi, and S. N. Lordejani, "Robust control of an interleaved dc-dc buck converter with coupled inductors," International Journal of Dynamics and Control, vol. 12, no. 10, pp. 3769–3777, 2024, doi: 10.1007/s40435-024-01443-2.

- [15] R. Hu, H. Qi, Z. Yan, W. Wu, J. Zeng, and J. Liu, "A coupled-inductor-based bidirectional dc-dc converter with high voltage conversion ratio and sensorless current balance," *IEEE Transactions on Industrial Electronics*, vol. 70, no. 3, pp. 2450–2460, 2023. doi: 10.1109/TIE.2022.3172770.

- [16] X. Zhou, D. Su, Y. Ma, and J. Pan, "Research on auto disturbance rejection control strategy of battery energy storage staggered parallel buck converter," in 2021 IEEE International Conference on Mechatronics and Automation, ICMA 2021, 2021, pp. 414–419. doi: 10.1109/ICMA52036.2021.9512656.

- [17] M. Biswas, S. Majhi, and H. Nemade, "Two-phase high efficiency interleaved buck converter with improved step-down conversion ratio and low voltage stress," *IET Power Electronics*, vol. 12, no. 15, pp. 3942–3952, Jan. 2019, doi: 10.1049/iet-pel.2019.0547.

- [17] I. O. Lee, S. Y. Cho, and G. W. Moon, "Interleaved buck converter having low switching losses and improved step-down conversion ratio," *IEEE Transactions on Power Electronics*, vol. 27, no. 8, pp. 3664–3675, Aug. 2012, doi: 10.1109/TPEL.2012.2185515.

- [18] M. Bendali, C. Larouci, T. Azib, C. Marchand, and G. Coquery, "Design methodology of an interleaved Buck converter for onboard automotive application, multi-objective optimisation under multi-physic constraints," *IET Electrical Systems in Transportation*, vol. 5, no. 2, pp. 53–60, 2015, doi: 10.1049/iet-est.2013.0045.

- [19] I.-O. Lee, S.-Young Cho, and G.-W. Moon, "Interleaved buck converter having low switching losses and improved step-down conversion ratio," *IEEE Transactions on Power Electronics*, vol. 27, no. 8, pp. 3664–3675, Aug. 2012.

[20] J. Chen, D. Maksimović, and R. W. Erickson, "Analysis and design of a low-stress buck-boost converter in universal-input pfc applications," *IEEE Transactions on Power Electronics*, vol. 21, no. 2, pp. 320–329, Mar. 2006, doi: 10.1109/TPEL.2005.869744.

- [21] K. Matsumoto, K. Nishijima, T. Sato, and T. Nabeshima, "A two-phase high step down coupled-inductor converter for next generation low voltage cpu," in 8th International Conference on Power Electronics - ECCE Asia: "Green World with Power Electronics", ICPE 2011-ECCE Asia, Jeju, Korea (South), 2011, pp. 2813–2818. doi: 10.1109/ICPE.2011.5944777.

- [22] P. S. Shenoy, M. Amaro, J. Morroni, and D. Freeman, "Comparison of a buck converter and a series capacitor buck converter for high-frequency, high-conversion-ratio voltage regulators," *IEEE Transactions on Power Electronics*, vol. 31, no. 10, pp. 7006– 7015, Oct. 2016, doi: 10.1109/TPEL.2015.2508018.

- [23] K. Nishijima, K. Harada, T. Nakano, T. Nabeshima, and T. Sato, "Analysis of double step-down two-phase buck converter for VRM," in *INTELEC, International Telecommunications Energy Conference (Proceedings)*, Berlin, Germany, 2005, pp. 497–502. doi: 10.1109/INTLEC.2005.335149.

- [24] L. Zhang and S. Chakraborty, "An interleaved series-capacitor tapped buck converter for high step-down dc/dc application," *IEEE Transactions on Power Electronics*, vol. 34, no. 7, pp. 6565–6574, Jul. 2019, doi: 10.1109/TPEL.2018.2877309.

- [25] D. Van Bui, H. Cha, and V. C. Nguyen, "Asymmetrical pwm series-capacitor high-conversion-ratio dc-dc converter," IEEE Transactions on Power Electronics, vol. 36, no. 8, pp. 8628–8633, Aug. 2021, doi: 10.1109/TPEL.2021.3056659.

- [26] Z. Chen, T. Xiang, Y. Wu, L. Zhao, and X. Tang, "Current sharing strategy of three-phase series capacitor buck converter for wide output voltage range application," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 11, no. 1, pp. 836–849, Feb. 2023, doi: 10.1109/JESTPE.2022.3192540.

- [27] V. G. Agelidis and S. Choi, "Analysis, design and experimental results of a floating-output interleaved-input boost-derived dc-dc high-gain transformer-less converter," *IET Power Electronics*, vol. 4, no. 1, pp. 1–9, Jan. 2011.

- [28] C. A. Villarreal-Hernandez, J. C. Mayo-Maldonado, G. Escobar, J. Loranca-Coutino, J. E. Valdez-Resendiz, and J. C. Rosas-Caro, "Discrete-time modeling and control of double dual boost converters with implicit current ripple cancellation over a wide operating range," *IEEE Transactions on Industrial Electronics*, vol. 68, no. 7, pp. 5966–5977, Aug. 2021, doi: 10.1109/TIE.2020.2996149.

- [29] F. Forest et al., "A nonreversible 10-kw high step-up converter using a multicell boost topology," IEEE Transactions on Power Electronics, vol. 33, no. 1, pp. 151–160, Jan. 2018, doi: 10.1109/TPEL.2017.2662224.

- [30] H. N. Tran, T. T. Le, H. Jeong, S. Kim, H. P. Kieu, and S. Choi, "High power density dc-dc converter for 800v fuel cell electric vehicles," *Proceedings of the Energy Conversion Congress and Exposition Asia, ECCE Asia 2021*, pp. 2224–2228, 2021, doi: 10.1109/ECCE-Asia49820.2021.9479257.

- [31] J. Chen and K. D. T. Ngo, "Interleaving techniques in power converters," *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 408–416, Mar. 2007.

## **BIOGRAPHIES OF AUTHORS**

Dr. Chan Viet Nguyen be solutioned his Bachelor's and Master's degrees in Electrical and Electronics Engineering from Ho Chi Minh City University of Technology (HCMUT), Vietnam National University – Ho Chi Minh City (VNU-HCM), in 2016 and 2018, respectively. He was awarded a Ph.D. in Energy Engineering by Kyungpook National University, Daegu, South Korea, in 2022. From 2016 to 2018, he served as a research associate at the Power Electronics Research Laboratory (PERL) at the University of Technology, Ho Chi Minh City. In 2022, he became a lecturer at the University of Technology, Vietnam National University – Ho Chi Minh City. His current research interests encompass electric vehicle charging systems, DC-DC converters, matrix converters, and renewable energy technologies. He can be contacted at email: ncviet@hcmut.edu.vn.

Thanh Phuong Ho D S graduated with a Bachelor's and Master's degree in Control Engineering and Automation from the Ho Chi Minh City University of Technology (HCMUT), Vietnam National University – Ho Chi Minh City (VNU-HCM) in 2010 and 2013, respectively. Since 2010, she has been working as a lecturer at the University of Technology – Vietnam National University, Ho Chi Minh City. Her current research interests include electric vehicle charging and DC-DC converters. She can be contacted at email: htphuong@hcmut.edu.vn.