# Novel Single Phase Full Bridge Inverter Formed by Floating Capacitors

# B. Prathap Reddy\*, K. Sreekanth Reddy\*\*, B. Samba Siva Reddy\*\*\*

\* Departement of Electrical Engineering, Lovely Professional University, India

\*\* School of Electronics and Electrical Engineering, Lovely Professional University, India

\*\*\* Departement of Electrical Engineering, Lovely Professional University, India

## **Article Info**

# Article history:

Received Oct 22, 2015 Revised Dec 21, 2015 Accepted Jan 14, 2016

## Keyword:

Floating Capacitor Full bridge inverter MATLAB SPWM inverter THD

## ABSTRACT

In this paper, a new single-phase bridge inverter is described which can generate a more steps of voltage levels with reduced number of switches, gate driver circuits and diodes as compare to normal multilevel inverter. Another feature of this inverter is its ability to produce the voltages from a single dc-link power supply which enables back-to-back operation of converter. The proposed method with more number of levels can improve power quality, lower switching losses and produce high quality voltage waveforms. Moreover at all load power factors the proposed method can be operated. The research of the model is done by means of computer simulation with the software MATLAB/SIMULINK. This topology has very low common mode voltage variation and dv/dt stress. Also this inverter is help full for reactive power compensation.

Copyright © 2016 Institute of Advanced Engineering and Science.

All rights reserved.

# Corresponding Author:

B. Prathap Reddy,

Departement of Electrical Engineering,

Lovely Professional University,

G T Road, Phagwara, 144411, Punjab, India.

Email: Prathap.bhimireddy@gmail.com

# 1. INTRODUCTION

Multilevel inverters are power electronic systems which produce a suitable AC output voltage waveform from many dc voltages as inputs [1]. Multilevel inverters have several features in comparison with the traditional two-level voltage inverters such as smaller output voltage level, better electromagnetic compatibility, lower harmonic components and lower switching losses [2], [3]. The conventional full bridge inverter output voltage or currents are of 0 or  $\frac{1}{2}$  V<sub>dc</sub> voltage. They are named as two-level inverter. In order to obtain a qualitative output voltage and current with reduced amount of ripple content, there is a necessity of high carrier frequency along with different pulse-width modulation (PWM) techniques. However In high-power applications these conventional square wave inverters have certain confines like conducting losses and device ratings. In modren years, Multilevel inverters have been utilized in medium and high power applications such as flexible AC transmission system (FACTS) [4], industrial motor drives [5], traction electric vehicle applications, drive systems [6], [7] and so on.

The output voltage waveform is almost a sinewave with minimum harmonic value, improving the performance of the drive presented in [8] and [9] as the number of voltage levels increases. The work described in [10] produces different voltage levels by switching the load current through capacitors. Here, by taking the redundant states for the same pole voltage, the direction of load current through the capacitor can be changed. In this paper, a novel structure for single phase full bridge inverter is presented which can produce more number of levels with minimum requirement of IGBTs, gate firing circuits and diodes.

194 □ ISSN: 2088-8694

# 2. THE STRUCTURE OF CONVENTIONAL SINGLE PHASE INVERTER

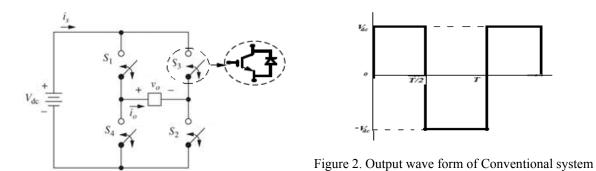

The structure of conventional square wave inverter is as follows like figure 1. In this structure, each switch consists of an IGBT and one diode (or anti-parallel diode). The output wave form of conventional system is shown in Figure 2.

Figure 1. The arrangement of conventional inveter

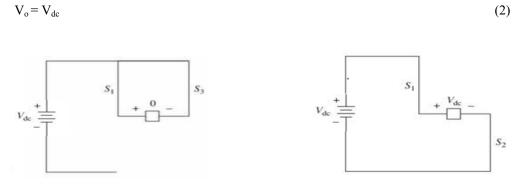

By closing and opening the switches in an appropriate sequence we can get an ac output waveform is synthesized from a dc input. There are four different modes depending on which switches are closed. The equivalent circuits of all four modes are shown in Figure 3. The output current depends on load like R or RL. Mode 1: During this interval the switches  $S_1$  and  $S_3$  are closed. The output load voltage is zero i.e. load is short circuited.

$$V_0 = 0 \tag{1}$$

Mode 2: During this interval the switches  $S_1$  and  $S_2$  are closed. The output load voltage is equals to the input voltage ( $V_{dc}$ ) i.e. load is connected across source directly. And the load current flows through  $V_{dc}$  -  $S_1$ - Load -  $S_2$  and  $V_{dc}$ .

Figure 3(a). Mode 1

Figure 3(b). Mode 2

In a similar manner the output voltage will have a negative of input voltage state and zero voltage state.

$$V_0 = -V_{dc} \tag{3}$$

And this cycle will repeats continuously.

The rms output voltage is,

$$V_{o} = \left(\frac{2}{T} \int_{0}^{T/2} V dc^{2} dt\right)^{1/2}$$

$$= V_{dc}$$

(4)

The Table 1 Shows the different swiching states of conventional full bridge inverter. Switches S1 and S4 or (S2 and S3) should not be turned on simultaneously. Otherwise, a dead zone interval takes place across the dc source.

| 1 doic 1 | . Divitori states of square wave | inverter |

|----------|----------------------------------|----------|

| Mode     | On Position                      | Vo       |

| 1        | S1 & S3                          | 0        |

| 2        | S1 & S2                          | + Vdc    |

| 3        | S2 & S4                          | 0        |

| 4        | S3 & S4                          | - Vdc    |

Table 1. Switch states of Square wave inverter

# 3. PROPOSED INVERTER

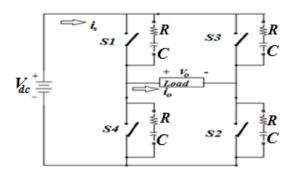

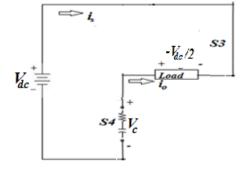

The proposed structure of full bridge inverter is shown in Figure 4. In this structure, each switch contains of an IGBT and one diode (or anti-parallel diode) also one capacitor and one small resistor are connected across each switch. The proposed inverter gives a qualitative output voltage and current with reduced amount of ripple content. Also this inverter is help full in reactive power compensation.

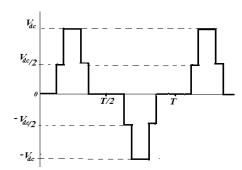

By increasing the no of levels in this inverter, the power rating of inverter can be increased without requirement of high ratings devices. The unique structures of this proposed inverter allow reaching high voltage with minimum harmonic content without the usage of transformers or cascade connected switching devices. As the number of output levels increases, the output voltage harmonic content decreases significantly. The outputvoltage wave form of proposed system is as follows like Figure 5.

Figure 4. The Arrangement of proposed inverter

Figure 5. Output wave form of Conventional system

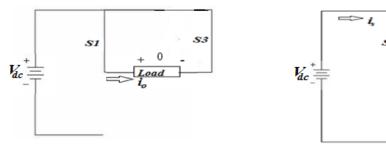

There are also eight different modes depending on which switches are closed. The equivalent circuits of all eight modes are follows like in Figure 6. The output current depends on load like R or RL. Mode 1: During this period the switches  $S_1$  and  $S_3$  are closed. The output load voltage is zero i.e. load is short circuited.

$$V_o = 0 (5)$$

Mode 2: During this period the switch  $S_1$  is closed. The output load voltage is equals to the difference of input voltage  $(V_{dc})$  and capacitor voltage  $(V_c)$ . And the load current flows through  $V_{dc}$  -  $S_1$ - Load – capacitor and  $V_{dc}$ .

$$V_o = V_{dc} - V_c = V_{dc}/2$$

(6)

Here consider the voltage across the resistor is negligible and  $V_c \approx V_{dc}/2$ .

196 □ ISSN: 2088-8694

Figure 6(a). Mode 1

Figure 6(b). Mode 2

Mode 3: During this period the switches  $S_1$  and  $S_2$  are closed. The output load voltage is equals to the input voltage ( $V_{dc}$ ) i.e. load is connected across source directly. And the load current flows through  $V_{dc}$  -  $S_1$ - Load -  $S_2$  and  $V_{dc}$ .

$$V_{o} = V_{dc} \tag{7}$$

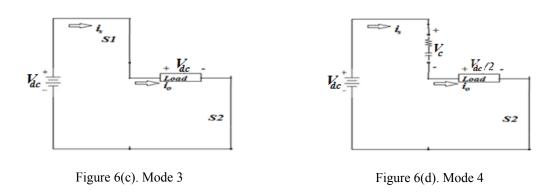

Mode 4: Mode 2 and period4 are same only the switching sequence is different. During this period the switch  $S_2$  is closed. The output load voltage is equals to the difference of input voltage  $(V_{dc})$  and capacitor voltage  $(V_c)$ . And the load current flows through  $V_{dc}$  – capacitor - Load -  $S_2$  and  $V_{dc}$ . The output voltage is follows as equation (6).

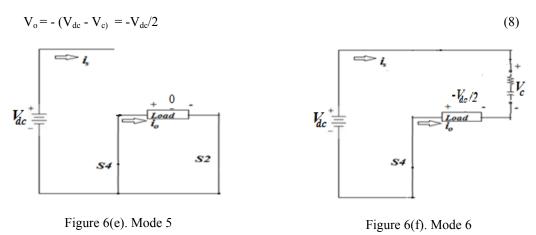

Mode 5: During this period the switches  $S_2$  and  $S_4$  are closed. The output load voltage is zero i.e. load is short circuited. The output voltage is follows as equation (5)

Mode 6: During this period the switch  $S_4$  is closed. The output load voltage is equals to the difference of input voltage  $(V_{dc})$  and capacitor voltage  $(V_c)$ . And the load current flows through  $V_{dc}$  - capacitor - Load -  $S_1$  and  $V_{dc}$ .

IJPEDS ISSN: 2088-8694 □ 197

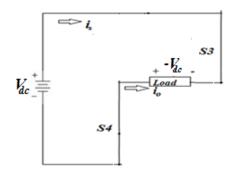

Mode 7: During this period the switches  $S_3$  and  $S_4$  are closed. The output load voltage is equals to the negative of input voltage ( $V_{dc}$ ) i.e. load is connected across source directly. And the load current flows through  $V_{dc}$  –  $S_3$ - Load-  $S_4$ and  $V_{dc}$ .

$$V_{o} = -V_{dc} \tag{9}$$

Mode 8: During this period de the switch  $S_2$  is closed. The output load voltage is equals to the negative difference of input voltage ( $V_{dc}$ ) and capacitor voltage ( $V_c$ ). And the load current flows through  $V_{dc}$  – capacitor - Load -  $S_2$  and  $V_{dc}$ . The output voltage is follows as equation (8) and this cycle will repeats continuously.

Figure 6(e). Mode 7

Figure 6(f). Mode 8

The Table 2. Shows the different swiching states of proposed full bridge inverter.

| TC 11 A   |         |        | •        | 1        | 0 11   | 1 . 1                     | • .       |

|-----------|---------|--------|----------|----------|--------|---------------------------|-----------|

| Table?    | arratah | atataa | $\sim$ t | nronogod | +111   | hridaa                    | intrortor |

| 1 41115 4 | SWILLI  | STATES | ()1      | proposed | 111111 | $\mathbf{m}_{\mathbf{n}}$ | HIVEHEL   |

|           |         |        |          |          |        |                           |           |

| Table 2: Switch states of proposed fair or age inverter |                 |                   |  |  |

|---------------------------------------------------------|-----------------|-------------------|--|--|

| State                                                   | Switches Closed | Vo                |  |  |

| 1                                                       | S1 & S3         | 0                 |  |  |

| 2                                                       | S1              | $+ V_{dc}/2$      |  |  |

| 3                                                       | S1 & S2         | $+$ $V_{dc}$      |  |  |

| 4                                                       | S2              | $+ V_{dc}/2$      |  |  |

| 5                                                       | S2 or S4        | 0                 |  |  |

| 6                                                       | S4              | $-V_{\rm dc}/2$   |  |  |

| 7                                                       | S3 & S4         | - V <sub>dc</sub> |  |  |

| 8                                                       | S3              | - $V_{dc}/2$      |  |  |

# 4. COMPARISON OF PROPOSED STRUCTURE WITH CONVENTIONAL STRUCTURE

The conventional full bridge inverter output voltage or current could be either 0 or  $\pm$  V<sub>dc</sub>. These inverters are also named as two level inverter. To get a qualitative voltage waveform and current with reduced amount of ripple content, these inverters require higher frequency of carrier signal along with different pulse-width modulation (PWM) techniques. However in high-power applications, these two level inverters have certain confines like conduction losses and device ratings. Table 3 gives the compaision between conventional two level inverter and the proposed five level (line voltage) inverter.

Table 3. Comparison between conventional and proposed structures

| rable 3. Comparison between conventional and proposed structures |                                             |  |  |  |

|------------------------------------------------------------------|---------------------------------------------|--|--|--|

| Conventional Full bridge inverter                                | Proposed inverter                           |  |  |  |

| 2(line voltage)                                                  | 5(line voltage)                             |  |  |  |

| 48%                                                              | 19.60%                                      |  |  |  |

| high                                                             | Low                                         |  |  |  |

| low                                                              | High                                        |  |  |  |

| high                                                             | Low                                         |  |  |  |

| high                                                             | Low                                         |  |  |  |

| Square wave                                                      | Approximate sine wave                       |  |  |  |

|                                                                  | 2(line voltage) 48% high low high high high |  |  |  |

198 □ ISSN: 2088-8694

The proposed inverter gives a qualitative voltage and current waveform with reduced ripple content. Also this inverter is help full in reactive power compensation. With this proposed structure it may easier to produce a high power, high voltage inverter due to the voltage stresses across each switch is controlled. The limitations of conventional two level inverter are overcome by proposed inverter. Table 4 gives the compaision between three level multilevel inverter and the proposed five level (line voltage) inverter.

| Table 4 Com  | narison betweer | three level | multilevel | inverter and  | proposed inverter |

|--------------|-----------------|-------------|------------|---------------|-------------------|

| Table 4. Com | parison between |             | muntilever | miver ter and | proposed inverter |

| Parameter                        | Three level multi level inverter | Proposed inverter |

|----------------------------------|----------------------------------|-------------------|

| No of output voltage levels      | 5(line voltage)                  | 5(line voltage)   |

| Voltage stresses across switches | medium                           | Low               |

| No of switches                   | high                             | low               |

| Electromagnetic interference     | Medium                           | Low               |

## 5. SIMULATION RESULTS

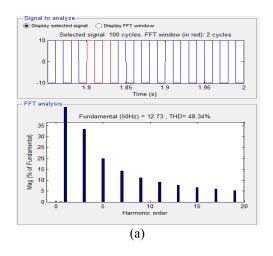

In this section, the MATLAB software is utilized for simulation. Figure 7 shows results of the normal single phase inverter i.e. output voltage output current and their harmonic spectrums. The inverter is having one supply source as DC with a magnitude of 10V. A load which have been taken as the R-L load (R =  $1\Omega$  and L = 100mH) for simulation purpose. The switches are IGBT's with internal diodes and having internal resistance of 1m  $\Omega$ .

The total harmonic distortion (THD) is a popular performance index which estimates the amount of harmonic content is presented in the output waveform for the power converters. Different modulation methods have been introduced for inverters namely trapezoidal modulation, stepped modulation, SPWM, space vector PWM and modified reference with multi carrier waveforms.

Figure 7. Simulation results for conventional system (a) harmonic spectrum of output voltage (THD=48.34%); (b) Harmonic spectrum of output current (THD= 12.12%)

In this paper, the Sinusoidal PWM has been used. The Sinusoidal PWM technique can eliminate the lower order harmonics along with the control of inverter outur voltage. The requirement of filter will be minimized as the higher order harmonics can be eliminated easily with SPWM.

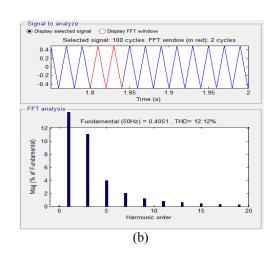

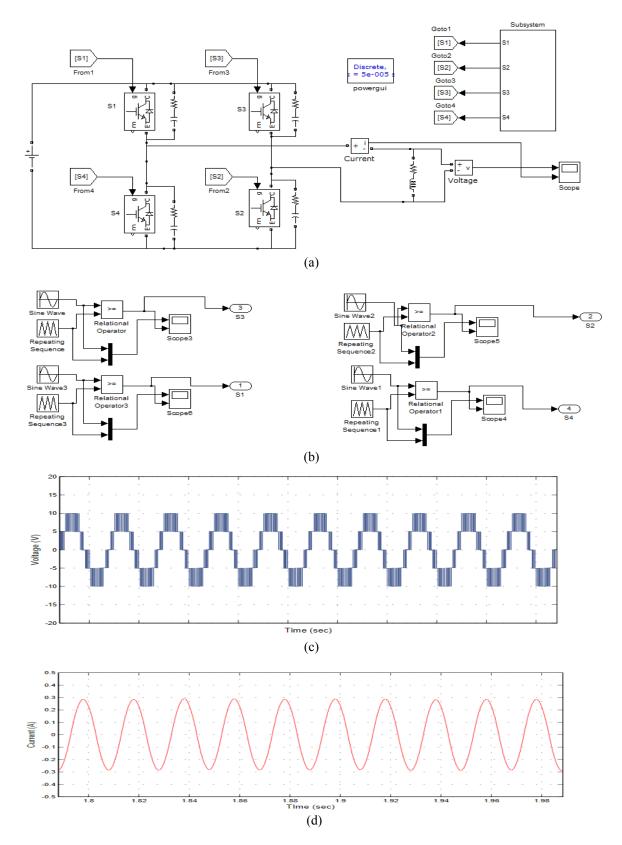

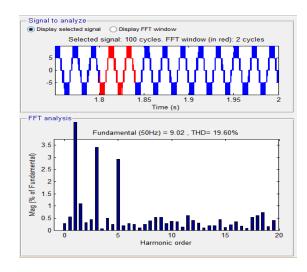

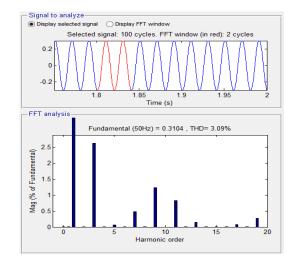

Figure 8 shows the proposed single phase inverter simulation circuit along with its voltage and current waveforms. The inverter is having one supply source as DC with a magnitude of 10V. A load which have been taken as the R-L load (R =  $1\Omega$  and L = 100mH) for simulation purpose. The switches are IGBT's with internal diodes and having internal resistance of 1m  $\Omega$  also having parallel capacitors. Figure 9 shows the harmonic spectrum of output voltage (THD=19.60%), harmonic spectrum of output current (THD=3.09%) of proposed inverter.

Figure 8. Simulation results of proposed inverter (a) Circuit diagram; (b) SPWM sequence for switches (subcircuit); (c) Output voltage; (d) Output current

200 ☐ ISSN: 2088-8694

Figure 9. Simulation results for conventional system (a) Simulation output voltage and harmonic spectrum (THD=19.60%); (d) Simulation output current and harmonic spectrum (THD= 3.09%)

## 6. CONCLUSION

In this paper, a new multilevel voltage source inverter has been proposed. For the proposed structure, each switch consists of an IGBT and one anti-parallel diode also one capacitor and one resistor are connected across the switch. The proposed inverter gives a qualitative output voltage and current waveform with reduced amount of ripple content. Also this inverter is help full in reactive power compensation. The simulation results have been presented for the proposed inverter using the SPWM technique. From the results of the proposed system THD value is reduced when compare to conventional system. The proposed inverter used in FACTS, UPS, ASDs, and Var compensators.

# **ACKNOWLEDGEMENTS**

I manifest my heartier thankfulness pertaining to our contentment over. Mr K Sreekanth Reddy, Assistant professor, School of Electronics & Electrical Engineering, Lovely Professional University, Punjab for his precious suggestions apart from general guidance, constant encouragement throughout my work, without which it would probably not possible for me to bring out the work in this form.

# REFERENCES

- [1] JN Chiasson, LM Tolbert, KJ McKenzie, Z Du. Control of Multilevel converter Using Resultant Theory. *IEEE Trans. On Cont. Sys. Tech.*, 2003; 11(3): 345-354.

- [2] JH Kim, SK Sul, PN Enjeti. A carrier-based PWM method with optimal switching sequence for a multilevel four-leg voltage-source inverter. *IEEE Trans. Ind. Appl.*, 2008; 44(4): 1239-1248.

- [3] LM Tolbert, FZ Peng, T Cunnyngham, JN Chiasson. Charge Balance Control Schemes for Cascade Multilevel Converter in Hybrid Electric Vehicles. *IEEE Trans. Industrial Electronics*, Vol. 49, No. 5, pp. 1058-1064, Oct. 2002

- [4] NH Kim. Rotor fault detection system for inverter driven induction motor using current signals and an Encoder. *Journal of Power Electronics*. 2007; 7(4): 271-277.

- [5] MF Aiello, PW Hammond, M Rastogi. Modular Multi-Level Adjustable Supply with Parallel Connected Active Inputs. U.S. Patent. 2001.

- [6] LM Tolbert, FZ Peng, TG Habetler. *Multilevel Inverters for Electric Vehicle Applications*. IEEE Workshop on Power Electronics in Transportation. 1998; 1424-1431.

- [7] MN Abdul Kadir, S Mekhilef, HW Ping. Dual vector control strategy for a three –stage hybrid cascaded multilevel inverter. *Journal of power Electronic.* 2010; 10(2): 155-164.

- [8] A.M. Massoud, S. Ahmed, P.N. Enjeti, and B.W.Williams, "Evaluation of a multilevel cascaded-type dynamic voltage restorer employing discontinuous space vector modulation", *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2398–2410, Jul. 2010.

- [9] S. Rivera, S. Kouro, B. Wu, S. Alepuz, M. Malinowski, P. Cortes, and J.R. Rodriguez, "Multilevel direct power control a generalized approach for grid-tied multilevel converter applications", *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5592–5604, Oct. 2014.

[10] T.A. Meynard and H. Foch, "Multi-level conversion: High voltage choppers and voltage-source inverters", in *Proc. IEEE 23rd Annu. Power Electron. Spec. Conf.*, Jun. 29–Jul. 3, 1992, vol. 1, pp. 397–403.

## **BIOGRAPHIES OF AUTHORS**

B. Prathap Reddy was born in Anantapur, Andhra Pradesh, in 1993. He received the B.E. degree in electrical and electronics engineering from JNTU, Anantapur, India, in 2014. He is currently working toward the M.Tech degree in Power electronics and drives, Lovely Professional University Punjab. His current research interests include renewable Energy systems, pwm converters, motor drives, and electromechanic systems.

K. Sreekanth Reddy was born in Kadapa, Andhra Pradesh, in 1987. He received the B.E. degree in electrical and electronics engineering from JNTU, Hyderabad, India, in 2008. He received M.Tech degree in Power electronics and drives, from VIT University in 2010. From 2010 onwards he is working as an Assistant professor in Lovely Professional University and his research area of interests are Multilevel inverters, power quality and drives.

B. Samba Siva Reddy was born in Anantapur, Andhra Pradesh, in 1992. He received the B.E. degree in electrical and electronics engineering from JNTU, Anantapur, India, in 2014. He is currently working toward the M.Tech degree in Power electronics and drives, Lovely Professional University, Punjab. His current research interests include power electronics, and power quality, renewable energy systems.