# A Novel Topology of Multilevel Inverter with Reduced Number of Switches and DC Sources

Nakul Thombre, Ratika singh Rawat, Priyanka Rana, Umashankar S School of Electrical Engineering, VIT University, Vellore Tamilnadu, India

## Article Info

#### Article history:

Received Feb 17, 2014 Revised May 17, 2014 Accepted May 29, 2014

#### Keyword:

21 levels Asymmetric multilevel inverter Multilevel inverters PWM Techniques Total harmonic distortion

### **Corresponding Author:**

Nakul Thombre, School of Electrical Engineering, VIT University, Vellore, Tamilnadu, India. Email: nak128900@gmail.com

# ABSTRACT

This paper introduces new topology of cascaded multilevel inverter, with considerable reduction in the number of switches and DC voltage sources. The proposed topology is based on asymmetrical multilevel inverter which produces 21 levels of output with the use of 11 unidirectional switches, 3 diodes and 4 DC voltage sources. The advantages of this topology are reduction in the number of switches (2 nos.) and gate driver circuits (2 nos.), reduction in the number of DC sources (2 nos.) also cost, complexity, and space required for hardware is reduced without sacrificing the quality output of the inverter. To reduce the THD further Level shifting SPWM techniques such as PD, POD & APOD are used and comparison is shown on the basis of THDs obtained from the above SPWM techniques. Frequency of carrier waves is 1KHz, and modulation index is 1.0. To validate the proposed topology the circuit is simulated and verified by using MATLAB/Simulink.

Copyright © 2014 Institute of Advanced Engineering and Science. All rights reserved.

#### 1. INTRODUCTION

Now-a-days, in industries, power conversion systems become very popular and are used extensively. The power conversion system includes AC-DC, DC-AC, DC-DC, AC-AC conversions. Many high and medium voltage applications require such power conversion systems. Those applications are HVDC transmission, FACTS, AC/DC drives, renewable energy sources such as PV solar cells, wind, fuel cells etc. [2]-[4]. This paper concentrates on DC-AC conversion (Inverter action). A conventional single phase inverter is able to produce voltage levels of +Vdc, 0, -Vdc, so the output waveform of the inverter is quasi-square wave, which is not advisable to use as an input to any AC system. Hence, to get nearly sinusoidal waveform, multilevel inverter is introduced in 1975 [10]. The output of multilevel inverter is a staircase wave, which is nearly sinusoidal. By increasing the number of output voltage levels in multilevel inverter the THD can be minimized. Also ripple content in the output of multilevel inverter is voltage stress across the individual switch is lesser in case of MLI [5]. Many topologies of MLI are developed and studied. They are generally classified into:

- a) Flying-capacitor inverter

- b) Diode-clamped inverter

- c) Cascaded H-bridge inverter

From these inverter topologies cascaded H-Bridge multilevel inverter is widely used [6]-[7]. Cascaded inverter has 'n' number of series connected cells, with an individual DC voltage source connected to each cell. There are two groups of cascade multilevel converters, the symmetric and the asymmetric

multilevel converters. In symmetric MLI all the DC voltage sources used are of equal magnitude, whereas in asymmetric MLI magnitudes of DC voltage sources are unequal.

In the asymmetric topologies, the values of DC voltage sources magnitudes are unequal. By giving proper switching sequence to the gate driver circuits, desired number of output voltage levels can be obtained. So the number of power electronic components required, will be reduced as compared to that of MLI with symmetrical DC voltage sources [8]. One of the advantages of asymmetrical MLI is that with the same number of switches and DC voltage sources, the number of output voltage level obtained is more, when compared to the symmetrical topology.

This paper proposes new asymmetric topology for 21- level voltage output with reduced number of switches. The proposed topology has been also analyzed without using any PWM technique. But after using SPWM techniques THD of the output can be reduced further. Three techniques of SPWM are used here and compared among themselves, to figure out the technique which gives least THD.

# 2. PROPOSED TOPOLOGY

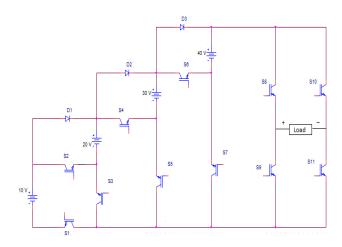

Figure 1. Proposed topology

The proposed topology has been successful in significantly reducing the switch count and no. of DC voltage sources. It consists of four asymmetrical DC voltage sources for 21 levels. Increments in the DC voltage sources are in the fashion n, 2n, 3n, 4n.... Where n = lowest DC voltage source magnitude. Proposed topology follows one relation between number of output voltage levels and number of DC sources. The relation is,

### Nlevel = NDC (NDC+1) + 1

Where, Nlevel= Number of levels, NDC= Number of DC sources.

The following table shows the switching sequence given to the proposed topology to generate 21 level voltage output.

| Table 1. Switching states of proposed topology |                      |            |     |            |     |     |            |            |          |

|------------------------------------------------|----------------------|------------|-----|------------|-----|-----|------------|------------|----------|

| Sr. No                                         | Output Voltage Level | <b>S</b> 1 | S2  | <b>S</b> 3 | S4  | S5  | <b>S</b> 6 | <b>S</b> 7 |          |

| 1                                              | 0                    | OFF        | OFF | OFF        | OFF | OFF | OFF        | OFF        | щ        |

| 2                                              | <u>+</u> Vdc         | ON         | OFF | OFF        | OFF | OFF | OFF        | OFF        | U        |

| 3                                              | <u>+</u> 2Vdc        | OFF        | OFF | ON         | OFF | OFF | OFF        | OFF        | Ā        |

| 4                                              | <u>+</u> 3Vdc        | OFF        | OFF | OFF        | OFF | ON  | OFF        | OFF        |          |

| 5                                              | <u>+</u> 4Vdc        | OFF        | OFF | OFF        | OFF | OFF | OFF        | ON         | ~        |

| 6                                              | <u>+</u> 5Vdc        | ON         | OFF | OFF        | OFF | OFF | ON         | OFF        | <u> </u> |

| 7                                              | <u>+</u> 6Vdc        | OFF        | OFF | ON         | OFF | OFF | ON         | OFF        | <u> </u> |

| 8                                              | <u>+</u> 7Vdc        | OFF        | OFF | OFF        | OFF | ON  | ON         | OFF        | · ·      |

| 9                                              | <u>+</u> 8Vdc        | ON         | OFF | OFF        | ON  | OFF | ON         | OFF        |          |

| 10                                             | <u>+</u> 9Vdc        | OFF        | OFF | ON         | ON  | OFF | ON         | OFF        | <b>—</b> |

| 11                                             | <u>+</u> 10Vdc       | ON         | ON  | OFF        | ON  | OFF | ON         | OFF        | _        |

Table 1. Switching states of proposed topology

A Novel Topology Of Multilevel Inverter With Reduced Number Of Switches And DC... (Nakul Thombre)

## 3. PULSE WIDTH MODULATION METHODOLOGY

For an n – level inverter the multicarrier PWM method uses n-1 triangular carrier signals and only one modulating sinusoidal signal is applied as reference. The zero reference is placed in the middle of the carrier set. At every instant each carrier signal is compared with the modulating sinusoidal signal. Each comparison gives one if the modulating signal is greater than the triangular carrier signal, otherwise zero. The Multicarrier PWM method is categorized into 2 groups:

1) Phase shifted PWM method, where the multiple carriers are phase shifted accordingly.

2) Carrier disposition methods (CD) where the reference signal is sampled through a number of carrier signals displaced by continuous increments of the reference signal amplitude. Further carrier disposition PWM method is grouped into three:

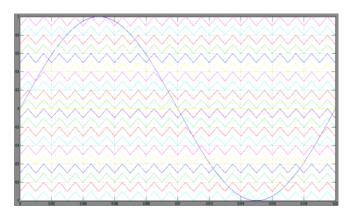

a) Phase Disposition (PD) Method - The phase disposition method has an equal number of carrier signals above and below the zero reference and are in phase with the same amplitude and frequency.

Figure 2. PD PWM

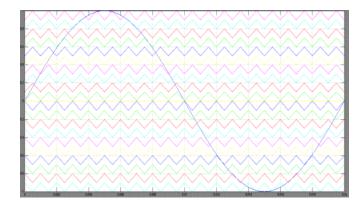

b) Alternative Phase Opposition Disposition (APOD) Method - All carrier waveforms in this APOD method are phase-displaced by 180° alternatively.

Figure 3. APOD PWM

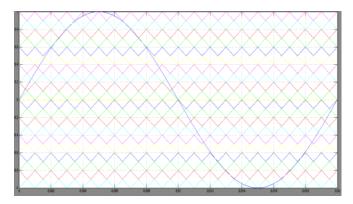

c) Phase Opposition Disposition (POD) Method - All carrier signals above the zero reference are in the same phase but the carrier signals below the zero reference are phase shifted by 180 degrees.

Figure 4. POD PWM

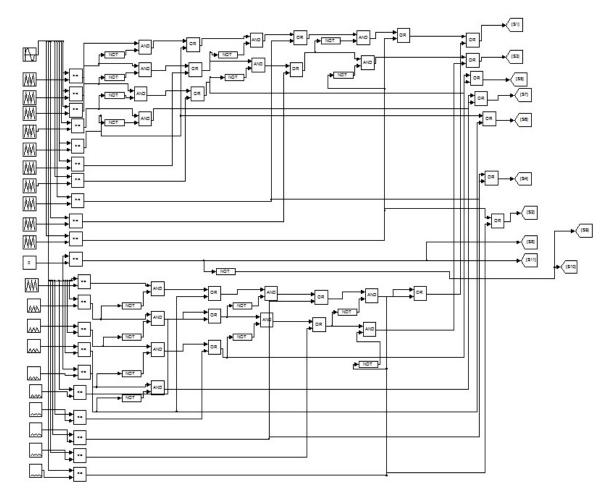

## 4. PULSE GENERATION CIRCUIT

For the pulse generation in the new topology 20 carriers signals are employed with the amplitude of each triangular carrier as 0.1 and frequency 1KHz. One sinusoidal wave of amplitude 1 and frequency 50 Hertz is employed as a reference signal. In order to turn on the switches in the particular desired instants, pulse generation circuit is used. In this circuit, the reference signal is compared with the carrier signal and the output of the comparison is fed to the logic gates and the required pulse pattern is generated at the output of the logic gates to trigger the switches. The pulse generation circuit implementing PD PWM technique is shown in Figure 5.

Figure 5. Pulse Generation Circuit

A Novel Topology Of Multilevel Inverter With Reduced Number Of Switches And DC... (Nakul Thombre)

## 5. SIMULATION RESULTS

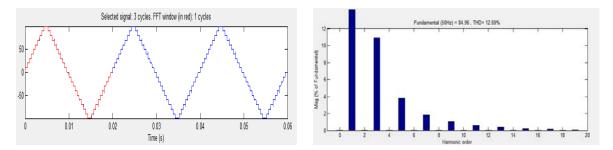

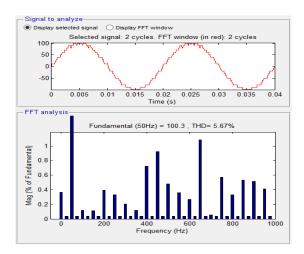

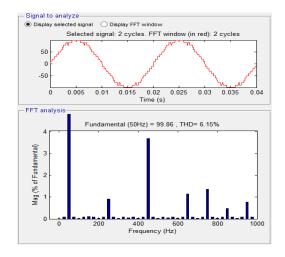

Proposed circuit is validated on MATLAB/Simulink platform. IGBT in parallel with the series RC snubber circuit is used as a switch. The magnitudes of DC voltage sources taken are 10V, 20V, 30V, 40V. Load resistance is taken as 10Ohm. Repeating sequence block is used to generate the switching sequence. Pulse generators are used to give pulses to the H - bridge. Figure 3 shows the circuit diagram of proposed topology. Figure 4 shows the 21 level output of the inverter. Figure 5 shows THD content in the output. It is **12.69%**. Figure shows THD of the output waveforms after using PD, POD, APOD PWM techniques.

Figure 6. THD of the output waveform without any PWM technique

gnal to analyze

Display selected signal O Display FFT window Sele cted signal: 2 cycles. FFT (in red): 2 cycle 100 0 -100 0.035 0.005 0.01 0.015 0.025 0.03 0.04 0.02 me (s) Tir FFT analysis Fundamental (50Hz) = 100.7 , THD= 5.93% 1.5 Mag (% of Fundamental) 0.5 0 Frequency (Hz)

Figure 7. THD of the output waveform using PDPWM technique

Figure 8. THD of the output waveform using PODPWM

Figure 9. THD of the output waveform using APODPWM

Table 2. Comparison of SPWM techniques

|   |         | <b>I</b>      |         |

|---|---------|---------------|---------|

|   | Sr. No. | PWM Technique | THD (%) |

|   | 1.      | PD            | 5.67    |

|   | 2.      | POD           | 5.93    |

| _ | 3.      | APOD          | 6.15    |

#### 6. CONCLUSION

In this paper, a new topology for 21 levels is proposed with reduced number of switches and DC sources. Thus, this new circuit will require lesser hardware space, lesser cost; also the complexity of the circuit will reduce. The FFT analysis done with the fundamental switching frequency resulted in the THD of 12.69%. From the FFT analysis, it is found that PDPWM technique gives least THD. The new circuit is examined in MATLAB/Simulink. It is observed that even after the reduction in switches and sources, the desired output is obtained.

#### REFERENCES

- [1] Bayat, Z.; Babaei, E., "A new cascaded multilevel inverter with reduced number of switches," *Power Electronics and Drive Systems Technology (PEDSTC), 2012 3rd*, vol., no., pp.416-421, 15-16 Feb. 2012.

- S. Lai and F.Z. Peng, "Multilevel converters -a new breed of power converters," IEEE Trans. Ind Appl., vol. 32, no. 3, pp. 509-17, M ay/June 1996.

- [3] Ebrahimi, E. Babaei, and G.B. Gharehpetian "A new multilevel converter topology with reduced number of power electronic components," Accepted and will be published on IEEE Trans. Ind. Electron.

- [4] S. De, D. Banerjee I, K. Siva kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," IET Power Electron., vol. 4, no. 4, pp. 384-392, 2011.

- [5] E. Babaei and S.H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," Elsevier Journal of Energy Conversion and Management, vol. 50, no. II, pp. 2761-2767, Nov. 2009.

- [6] S. Mekhilef and M.N. Abdul Kadir, "Novel vector control method for three-stage hybrid cascaded multilevel inverter," IEEE Trans. Ind. Electron., vol. 58, no. 4, pp. 1339-1349, April 2011.

- [7] S.D.G. Jayasinghal, D.M. Vilathgamuwal, and U.K. Madawala, "Cascade multilevel static synchronous compensator configuration for wind farms," IET Power Electron., vol. 4, no. 5, pp. 548-556,2011.

- [8] Ranjan, S.; Mishra, S.K., "Analysis of asymmetrical cascaded multilevel inverter for traction systems," *Energy Efficient Technologies for Sustainability (ICEETS), 2013 International Conference on*, vol., no., pp.708,713, 10-12 April 2013

- [9] Lakshmi, T.V.V.S.; George, N.; Umashankar, S.; Kothari, D.P., "Cascaded seven level inverter with reduced number of switches using level shifting PWM technique," *Power, Energy and Control (ICPEC), 2013 International Conference on*, vol., no., pp.676,680, 6-8 Feb. 2013

- [10] Ned mohan, Tore.M, undeland, and William.P. Robbins "power electronics, converters, Applications and Design", Third edition, New Delhi, Wiley India (P.)Ltd. Reprint.

- [11] M.H.Rashid "Power electronics : Circuits, Devices and applications. Third edition, Prentice hall, 2004

## **BIOGRAPHIES OF AUTHORS**

Nakul Thombre was born in Thane, Maharashtra . Currently, he is pursuing a Master's Degree in Power Electronics and Drives at VIT University, Vellore. He received his Bachelor Degree in Electrical Engineering in the year 2012 at College Of Engineering A'nagar affiliated to University of Pune, Maharashtra. His research interests are cascaded multilevel Inverter, SMPS, Battery operated vehicles and electrical drives.

Ratika Singh Rawat was born in Hapur, Uttar Pradesh. Currently, she is pursuing a Master's Degree in Power Electronics and Drives at VIT University, Vellore. She received her Bachelor Degree in Electronics and Instrumentation Engineering in the year 2013 at the Institute Of Technology and Management college affiliated to Rajiv Gandhi Technical University, Madhya Pradesh. Her research interests are cascaded multilevel Inverter and control of power electronic converters.

A Novel Topology Of Multilevel Inverter With Reduced Number Of Switches And DC... (Nakul Thombre)

Priyanka Rana was born in Gwalior, Madhya Pradesh. Currently, she is pursuing a Master's Degree in Power Electronics and Drives at VIT University, Vellore. She received her Bachelor Degree in Electronics and Instrumentation Engineering in the year 2013 at the Institute Of Technology and Management College affiliated to Rajiv Gandhi Technical University, Madhya Pradesh. Her research interests are cascaded multilevel Inverter and DC to DC converter.

Umashankar S received B.E. Degree in Electrical and Electronics Engineering from Govt. College of Technology, Coimbatore in the year 2001 and M. Tech., and PhD in Power Electronics from VIT University, Vellore in the year 2004 and 2013 respectively. Currently he is working as *Associate Professor* in the School of Electrical Engineering at VIT University, Vellore. He worked as Asst. Professor-Senior, Senior R&D Engineer and Senior Application Engineer in the power electronics, renewable Energy and electrical drives field for more than 10 years. He has been one of the Editorial Board members in International journal of electronics, communication and electrical engineering and reviewer in reputed journals like Elsevier, IEEE and IET. He has published/presented 98 papers in national and international journals/conferences. He has also co-authored/co-edited 10 books/chapters and 10 technical articles on power electronics applications in renewable energy and allied areas. His current areas of research activities include power electronics applications in wind and solar energy, modern electrical drives and control, smart grid and power quality.