# Structure of 15-Level Sub-Module Cascaded H-Bridge Inverter for Speed Control of AC Drive Applications

## R. Uthirasamy\*, U. S. Ragupathy\*\*, R. Naveen\*\*\*

\* Department of Electrical and Electronic Engineering, Jansons Institute of Technology, Coimbatore, Tamilnadu, India \*\* Department of Electronics and Instrumentation Engineering, Kongu Engineering College, Erode, Tamilnadu, India \*\*\* Power Electronics and Drives, Jansons Institute of Technology, Coimbatore, Tamilnadu, India

## **Article Info**

## Article history:

Received Oct 3, 2014 Revised Dec 12, 2014 Accepted Jan 7, 2015

#### Keyword:

H-Bridge Inverter Motor drives Multilevel Speed Control Variable Frequency Zero Voltage Switching

## **ABSTRACT**

This paper deals with the implementation of a single phase 15-level Sub-Multilevel Cascaded H-Bridge Inverter (SMCHBI) for variable speed industrial drive applications. It consists of sub-multilevel modules and H-bridge inverter configuration. Sub-multilevel switches synthesize stepped DC link voltage and current from the DC sources. H-bridge inverter switches renovate stepped DC link voltage and current into sinusoidal waveform. Compared with conventional Cascaded Multilevel Inverter (CMLI), the proposed system employs the reduced number of power switches, DC sources and gate driver requirements. The proposed system not only reduces the overall system cost but also reduces the voltage stress across the inverter switches. The proposed system does not required additional resonant soft switching circuits for Zero Voltage Switching (ZVS) of inverter. In the proposed method, variable frequency method is adopted for the speed control of industrial induction motor drives. A prototype model of 15-level SMCHB is developed and the performance of the systems is validated experimentally.

Copyright © 2015 Institute of Advanced Engineering and Science.

All rights reserved.

### Corresponding Author:

R. Naveen, Power Electronics and Drives, Jansons Institute of Technology, Coimbatore, Tamilnadu, India. Email: naveenramaa92@gmail.com

## 1. INTRODUCTION

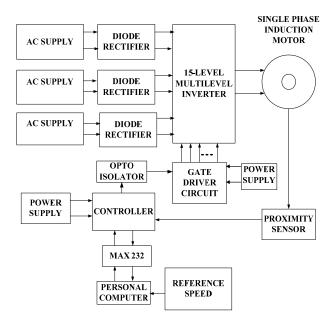

Advancement in power electronics lay down a wide spread scope for efficient operation of power converters. Variable speed drives plays a vital role in present day industries. Power electronic converters have the responsibility to carry out these tasks with high efficiency. Traditional power electronic inverters are Voltage Source Inverter (VSI) and Current Source Inverter (CSI). Two-level VSI topology is the simplest topology used to achieve the variable speed of industrial drives. Multilevel Inverters (MLI) are emerging as the new breed of power converter options for high power applications [1]. Three topologies of Multilevel Inverter (MLI) are; Diode Clamped Multilevel Inverters (DCMLI), Flying Capacitor Multilevel Inverters (FCMLI) and Cascaded Multilevel Inverter (CMLI) [2]-[4]. Among these inverter topologies, the FCMLI is difficult to be realized because each capacitor must be charged with different voltages as the voltage level increases. Moreover, the FCMLI, also known as a neutral clamped converter is difficult to be expanded to multilevel because of the natural problem of the DC link voltage unbalancing. Two-level inverters and multilevel inverters of FCMLI and DCMLI having high voltage stress. To reduce the voltage stress across the inverter switches, resonant soft switching circuits are required. Most solar cell installation involves the use of multiple solar panels or modules, which are connected in series or parallel with CMLI. The most popular advantages of CMLI compared with the traditional two level voltage source inverters are lower semiconductor voltage stress, better harmonic performance, lower Electro Magnetic Interference (EMI) and lower switching losses [5]-[11]. The efficiency of the CMLI system is degraded, because of more number of DC sources and controlled power switches for higher voltage levels. In the proposed work, 15-level SMCHBI is designed and implemented for the speed control of single phase induction motor drive applications [12]-[20]. Compared with conventional CMLI, the proposed system employs the reduction in power switches, DC sources and driver circuit requirements. The speed control of the induction motor is achieved using Peripheral Interface Controller (PIC). Figure 1 shows the block diagram of the proposed SMCHBI. This paper is organized as seven sections as follows; Introduction of the CMLI is reviewed in Section 1. Structure of SMCHBI system is addressed in section 2. Modes of operation of SMCHBI are reviewed in Section 3. Implementation of 15-level SMCHBI fed single phase induction motor is addressed in Section 4. Results and discussion of the proposed system is presented in Section 5. Section 6 concludes the paper.

Figure 1. Block Diagram of SMCHBI Systems

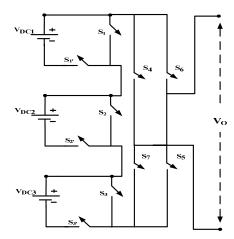

## 2. STRUCTURE OF SUB-MULTILEVEL CASCADED H-BRIDGE INVERTER

The general structure consists of sub-multilevel modules connected in series. DC voltage source in each sub-multilevel inverter is asymmetrical in manner. The output voltage of each sub-multilevel module is always positive or zero. To operate as an inverter, it is necessary to change the voltage polarity in every half cycle. To obtain positive and negative output voltage, an H-bridge inverter is added to the output of series connected sub-multilevel modules. The equivalent structure of 15-level SMCHBI is shown in Fig. 2. Each sub-multilevel module consists of (s+1) switches and a DC source.

Number of levels of CMLI configuration can be expressed as;

$$N_{level} = 2(s) + 1 \tag{1}$$

Number of switches of CMLI can be expressed as;

$$N_{switch} = 4s \tag{2}$$

Number of levels of SMCHBI configuration can be expressed as;

$$N_{level} = 2(m+1)^{S} - 1 (3)$$

Number of switches of SMCHBI can be expressed as;

$$N_{switch} = 2s + 4m \tag{4}$$

406 □ ISSN: 2088-8694

Where,

m is the number of H-bridge inverter s is the number of DC source

Figure. 2. Equivalent Structure of 15-Level SMCHBI

#### 3. MODES OF OPERATION

To obtain 15-level AC output from the asymmetrical DC sources, the proposed system can be operated under 15 modes of operation.

### 3.1. In Operating Mode 0

In mode 0 operation, all the switches are getting turned OFF. The output voltage of sub-multilevel module and H-bridge inverter are zero.

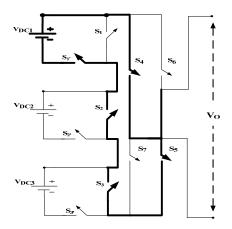

## 3.2. In Operating Modes 1 and 8

To obtain the 1<sup>st</sup> level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$  and  $S_3$  and H-Bridge switches  $S_4$  and  $S_5$  are getting turned ON as shown in Figure 3. Hence, the DC voltage source  $V_{DC1}$  is linked with the drive load. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = V_{01} = V_{DC1}$$

(For Positive Cycle) (5)

To obtain the  $8^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$  and  $S_3$  and H-Bridge switches  $S_6$  and  $S_7$  are getting turned ON. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = -V_{01} = -V_{DC1}$$

(For Negative Cycle) (6)

# 3.3. In Operating Modes 2 and 9

To obtain the  $2^{nd}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ,  $S_2$ ' and  $S_3$  and H-Bridge switches  $S_4$  and  $S_5$  are getting turned ON. Hence, the DC voltage source  $V_{DC2}$  is linked with the drive load. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = V_{02} = V_{DC2}$$

(For Positive Cycle) (7)

To obtain the  $9^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ,  $S_2$ ' and  $S_3$  and H-Bridge switches  $S_6$  and  $S_7$  are getting turned ON. The output voltage of H-bridge inverter can be expressed as:

$$V_0 = -V_{02} = -V_{DC2}$$

(For Negative Cycle) (8)

## 3.4. In Operating Modes 3 and 10

To obtain the  $3^{rd}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$ ' and  $S_3$  and H-Bridge switches  $S_4$  and  $S_5$  are getting turned ON. Hence, the DC voltage source  $V_{DC1}$  and  $V_{DC2}$  are linked with the drive load. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = V_{03} = (V_{DC1} + V_{DC2})$$

(For Positive Cycle) (9)

To obtain the  $10^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$ ' and  $S_3$  and H-Bridge switches  $S_6$  and  $S_7$  are getting turned ON. The output voltage of H-bridge inverter can be expressed as:

$$V_0 = -V_{03} = -(V_{DC1} + V_{DC2})$$

(For Negative Cycle) (10)

# 3.5. In Operating Modes 4and 11

To obtain the  $4^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ,  $S_2$  and  $S_3$ ' and H-Bridge switches  $S_4$  and  $S_5$  are getting turned ON. Hence, the DC voltage source  $V_{DC3}$  is linked with the drive load. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = V_{04} = V_{DC3}$$

(For Positive Cycle) (11)

To obtain the  $11^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ,  $S_2$  and  $S_3$ ' and H-Bridge switches  $S_6$  and  $S_7$  are getting turned ON. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = -V_{04} = -V_{DC3}$$

(For Negative Cycle) (12)

## 3.6. In Operating Modes 5and 12

To obtain the  $5^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$  and  $S_3$ ' and H-Bridge switches  $S_4$  and  $S_5$  are getting turned ON. Hence, the DC voltage source  $V_{DC1}$  and  $V_{DC3}$  is linked with the drive load. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = V_{05} = V_{DC1} + V_{DC3}$$

(For Positive Cycle) (13)

To obtain the  $12^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$  and  $S_3$ ' and H-Bridge switches  $S_6$  and  $S_7$  are getting turned ON. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = -V_{05} = -(V_{DC1} + V_{DC3})$$

(For Negative Cycle) (14)

### 3.7. In Operating Modes 6 and 13

To obtain the  $6^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ,  $S_2$ ' and  $S_3$ ' and H-Bridge switches  $S_4$  and  $S_5$  are getting turned ON. Hence, the DC voltage source  $V_{DC2}$  and  $V_{DC3}$  is linked with the drive load. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = V_{06} = V_{DC2} + V_{DC3}$$

(For Positive Cycle) (15)

To obtain the  $13^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ,  $S_2$ ' and  $S_3$ ' and H-Bridge switches  $S_6$  and  $S_7$  are getting turned ON. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = -V_{06} = -(V_{DC2} + V_{DC3}) \qquad \text{(For Negative Cycle)}$$

408 □ ISSN: 2088-8694

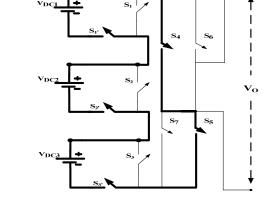

## 3.8. In Operating Modes 7 and 14

To obtain the  $7^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$ ' and  $S_3$ ' and H-Bridge switches  $S_4$  and  $S_5$  are getting turned ONas shown in Figure 4. Hence, the DC voltage source  $V_{DC1}$ ,  $V_{DC2}$  and  $V_{DC3}$  is linked with the drive load. The output voltage of H-bridge inverter can be expressed as;

$$V_0 = V_{07} = V_{DC1} + V_{DC2} + V_{DC3}$$

(For Positive Cycle) (17)

To obtain the  $14^{th}$  level of inverter output voltage, sub-multilevel switches  $S_1$ ',  $S_2$ ' and  $S_3$ ' and H-Bridge switches  $S_6$  and  $S_7$  are getting turned ON. The negative output voltage of H-bridge inverter can be expressed as;

$$V_0 = -V_{07} = -(V_{DC1} + V_{DC2} + V_{DC3})$$

(18)

Sub-multilevel and H-Bridge switches are getting triggered based on the switching strategy as shown in Table 1.

Figure 3. Mode 1 operation

Figure 4. Mode 7 operation

Table 1. Switching Strategy of Sub-Multilevel Switches and H-Bridge Switches

|       | Sub              | - Multil | evel Sw          | itches         |                  | Н              | I-bridge | Switch | es             | Levels |

|-------|------------------|----------|------------------|----------------|------------------|----------------|----------|--------|----------------|--------|

| $S_1$ | S <sub>1</sub> ' | $S_2$    | S <sub>2</sub> ' | S <sub>3</sub> | S <sub>3</sub> ' | S <sub>4</sub> | $S_5$    | $S_6$  | S <sub>7</sub> | Vo     |

| 0     | 0                | 0        | 0                | 0              | 0                | 0              | 0        | 0      | 0              | 0      |

| 0     | 1                | 1        | 0                | 1              | 0                | 1              | 1        | 0      | 0              | 1      |

| 1     | 0                | 0        | 1                | 1              | 0                | 1              | 1        | 0      | 0              | 2      |

| 0     | 1                | 0        | 1                | 1              | 0                | 1              | 1        | 0      | 0              | 3      |

| 1     | 0                | 1        | 0                | 0              | 1                | 1              | 1        | 0      | 0              | 4      |

| 0     | 1                | 1        | 0                | 0              | 1                | 1              | 1        | 0      | 0              | 5      |

| 1     | 0                | 0        | 1                | 0              | 1                | 1              | 1        | 0      | 0              | 6      |

| 0     | 1                | 0        | 1                | 0              | 1                | 1              | 1        | 0      | 0              | 7      |

| 0     | 1                | 1        | 0                | 1              | 0                | 0              | 0        | 1      | 1              | 8      |

| 1     | 0                | 0        | 1                | 1              | 0                | 0              | 0        | 1      | 1              | 9      |

| 0     | 1                | 0        | 1                | 1              | 0                | 0              | 0        | 1      | 1              | 10     |

| 1     | 0                | 1        | 0                | 0              | 1                | 0              | 0        | 1      | 1              | 11     |

| 0     | 1                | 1        | 0                | 0              | 1                | 0              | 0        | 1      | 1              | 12     |

| 1     | 0                | 0        | 1                | 0              | 1                | 0              | 0        | 1      | 1              | 13     |

| 0     | 1                | 0        | 1                | 0              | 1                | 0              | 0        | 1      | 1              | 14     |

IJPEDS ISSN: 2088-8694 □ 409

#### 4. IMPLEMENTATION OF 15-LEVEL SUB-MULTILEVEL CASCADED H-BRIDGE INVERTER

Variable speed drives have made its profound place in present industrial applications. Since the number of poles is fixed by design, the best way to vary the speed of the induction motor is by varying the supply frequency. The torque developed by the induction motor is directly proportional to the ratio of the applied voltage and the frequency of supply. In the proposed system, variable frequency method is implemented for the speed control of single phase induction motor. Pulse Width Modulation (PWM) technique based switching strategy is developed for sub-multilevel switches. The prototype model of the proposed system consists of controller unit, driver unit and power converter unit.

## 4.1. Controller Unit

PIC16F877 microcontroller forms the major part of the control unit. It compares the actual speed with the desired speed of induction motor drive and the PWM pulses are developed according to the variation in the speed. Actual speed of the induction motor is sensed by using the proximity sensor. Microcontroller provides the control signals to the MOSFET driver circuit via opto - coupler. RS-232 communications is the most popular method of Personal Computer (PC) to external device communications. Reference speed or desired speed of the induction motor is entered in PC using LABVIEW tools and which is transmitted to the controller unit via RS-232 cable.

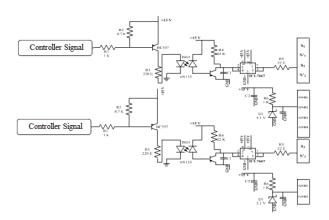

#### 4.2. Driver Unit

Three driver IC boards are assembled to trigger the sub-multilevel and H-bridge MOSFET switches. Control signals are transferred from PIC controller to the driver boards via opto-coupler. The driver circuit for the sub-multilevel inverter switches  $(S_1, S_1, S_2, S_3, S_3, S_3, S_3)$  is shown in the Figure 5.

Figure 5. Driver circuit unit of sub-multilevel inverter switches

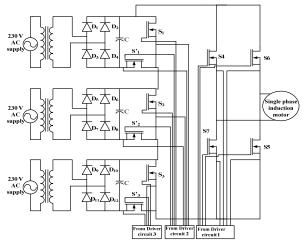

## 4.3. Power Circuit unit of SMCHBI

Figure 6. Hardware equivalent circuit of 15-level SMCHBI

410 SISSN: 2088-8694

The equivalent circuit of 15-level SMCHBI fed single phase induction motor drive is shown in Figure 20. Each sub-multilevel module consists of two power MOSFET switches.H-bridge unit of the proposed system consists of four power MOSFE switches. The asymmetrical voltage sources of sub-multilevel modules are 53.8 V, 107.4 V and 161.2 V. Three asymmetrical DC sources are developed from three diode bridge rectifier units as shown in Figure 6.

### 5. HARDWARE RESULTS AND DISCUSSIONS

In this section, the experimental results of the proposed 15-level single phase SMCHBI system for variable speed AC drive applications is presented. An experimental set up of the proposed system is developed to obtain the speed control of 0.25 HP induction motor drive and the results are put forth.

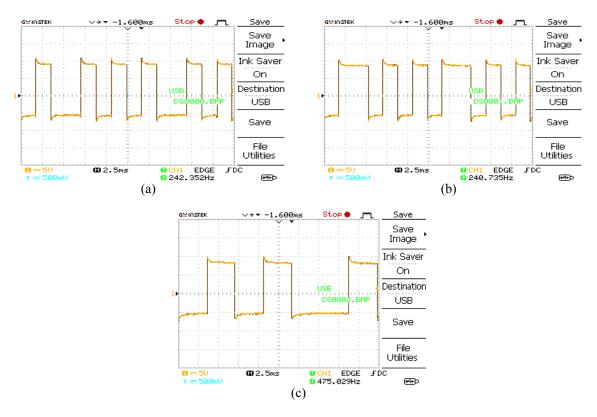

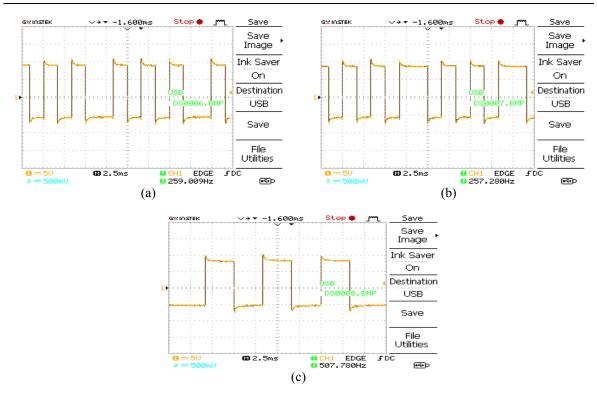

### 5.1. Gate Pulses to Sub-Multilevel Switches

Two patterns of gate pulses are developed for inverter switching.  $S_4$  and  $S_5$  switches receive the same pattern of firing pulses.  $S_6$  and  $S_7$  switches receive the same pattern of firing pulses which are  $180^\circ$  phase shift with  $S_4$  and  $S_5$  firing pulses. PWM based gate pulses are developed for sub-multilevel switches. Gate pulses are developed for achieving 4 sets of reference speed of induction motor. The generated gate pulses of sub-multilevel switches for obtaining 1100 RPM and 1200 RPM of rotor speed is shown in Figure 7 and Figure 8 respectively.

Figure 7. Gate Pulses to Sub-multilevel Switches for 1100 RPM: (a) To S<sub>1</sub>,(b) To S<sub>1</sub>',(c) To S<sub>2</sub>

From the Figure 7 and Figure 8, it is observed that the switching frequency of sub-multilevel pulses get increased to obtain the two reference speed of 1100 RPM and 1200 RPM, are tabulated in the Table 2.

Figure 8. Gate Pulses to Sub-multilevel Switches for 1200 RPM: (a) To S<sub>1</sub>,(b) To S<sub>1</sub>',(c) To S<sub>2</sub>

Table 2. Switching Frequency of sub-multilevel switches

| Rotor Spec | ed (RPM) | Switching Frequency (Hz) |        |        |  |

|------------|----------|--------------------------|--------|--------|--|

| Reference  | Actual   | $S_1$                    | $S_1$  | $S_2$  |  |

| 1100       | 1099     | 242.35                   | 240.73 | 475.02 |  |

| 1200       | 1195     | 259.00                   | 257.29 | 509.70 |  |

## 5.2. Output Voltage of H-Bridge Inverter

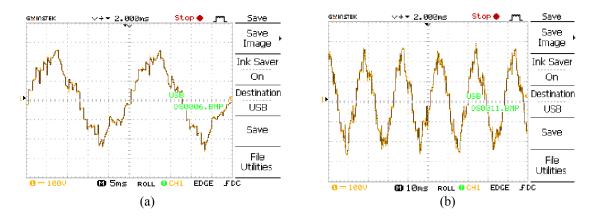

The output voltage waveforms of H-bridge inverter are shown in Figure 9(a) and (b). From the obtained waveform shown in Figure 9(a), it is observed that the output voltage and frequency of H-bridge inverter is 280V and 41.35Hz respectively. From the obtained waveform shown in Figure 9 (b), it is observed that the output voltage and frequency of H -bridge inverter is 280V and 52.415Hz respectively.

Figure 9. Output Voltage of H-Bridge Inverter for a) 41.35 Hz b) For 52.415 Hz

412 ISSN: 2088-8694

## 5.3. Actual Speeds of 15-level SMCHBI fed Induction Motor Drive

Speed control of induction motor is achieved in accordance with the reference speed, which is imported to the controller through personal computer using LABVIEW tools. For the reference speeds of 1100RPM, 1200RPM the obtained the actual speeds of the induction motor is 1099RPM, 1195RPM respectively. Table 3 clearly implies the speed control of 15-level SMCHBI fed induction motor which is achieved using variable frequency method. The actual rotor speed of the induction motor for the reference speed of 1100RPM is shown in Figure 10.

Table 3. Frequency Vs Actual Speed of the Induction Motor

| Rotor Spee | ed (RPM) | Frequency (Hz) | Time Period (ms) |

|------------|----------|----------------|------------------|

| Reference  | Actual   |                |                  |

| 1100       | 1099     | 41.35          | 24.18            |

| 1200       | 1195     | 48.85          | 20.47            |

| 1500       | 1494     | 52.415         | 19.07            |

The required DC sources and switches for single phase15-level CMLI, BCMLI and SMCHBI systems are analyzed and tabulated in Table 4 and 5 respectively. From the analysis, it is inferred that the proposed SMCHBI system required less number of DC sources, and number of switches than conventional systems. The technical specification of ICL7667 is listed in Table 6.

Table 4. Required Number Switches for Single Phase CMLI and SMCHBI

| Number of | Number of Switches |           |  |

|-----------|--------------------|-----------|--|

| levels    | In CMLI            | In SMCHBI |  |

| 5         | 4                  | 6         |  |

| 7         | 12                 | 8         |  |

| 15        | 28                 | 10        |  |

| 31        | 60                 | 12        |  |

Figure 10. Actual drive speed (1099 RPM) for the reference speed (1100 RPM)

Table 5.Required Number DC Sources for Single Phase CMLI and SMCHBI

| Number of | Number of DC Sources |           |  |  |

|-----------|----------------------|-----------|--|--|

| levels    | In CMLI              | In SMCHBI |  |  |

| 3         | 2                    | 1         |  |  |

| 7         | 3                    | 2         |  |  |

| 15        | 7                    | 3         |  |  |

| 31        | 15                   | 4         |  |  |

Table 6. Technical Specifications of ICL7667

| S.No. | Specification         |                   | Range         |

|-------|-----------------------|-------------------|---------------|

| 1     | Logic 1 Input Voltage | $V_{\mathrm{IH}}$ | 4.5 V to 17 V |

| 2     | Output High Voltage   | $V_{\mathrm{OH}}$ | 14.95 V       |

| 3     | Power Supply Current  | $I_{DD}$          | 7 mA          |

| 4     | Supply Voltage        | $ m V_{DD}$       | 15 V          |

Figure 11. Experimental Setup of PC interfaced 15level SMCHBI fed Induction Motor Drive System

Table 7. Hardware Specification

| Components          | Specifications |  |  |

|---------------------|----------------|--|--|

| Diode               | 1N4007         |  |  |

| Capacitor           | 1000 μF        |  |  |

| Disc Capacitor      | 22 pF          |  |  |

| MOSFET              | IRF840         |  |  |

| PIC Microcontroller | 16F877A        |  |  |

| Driver IC           | IC17667        |  |  |

| Opto Isolator       | 6N135          |  |  |

| 1Ø Induction Motor  | 0.25 HP        |  |  |

| Speed Sensor        | Proximity      |  |  |

The experimental setup of the proposed system is shown in Figure 11. The power supply unit consists of step down transformer and regulator ICs IC7805 and IC7815. Sub-multilevel module consists of six MOSFET switches. H-bridge inverter consists of four MOSFET switches. Controller unit consists of PIC16F877 and its biasing components including crystal oscillator. Driver unit consists of ICL7667 and its biasing components. Three diode bridge rectifiers are implemented for obtaining equivalent DC sources. The detailed system hardware specification is tabulated in Table 7.

### 6. CONCLUSION

In this paper, a new structure of single phase 15-level Su-Multilevel Cascaded H-Bridge Inverter fed variable speed induction motor drive has been proposed. It has been shown that the structure consisting of sub-multilevel modules and H-bridge inverter. It is shown that this structure can be an appropriate aspirant for power converters used in speed control of AC drive applications. Compared with conventional inverter fed speed control of induction motor drive systems, the proposed system employs less voltage stress, reduced switch count and DC source count. The proposed topology extends the design flexibility and possible to optimize the power converter for achieving the main objectives. The experimental results of the 15-level Sub-Multilevel Cascaded H-Bridge Inverter are validated in this paper. In the proposed system, desired speed of the induction motor drive is achieved through the A prototype model of 15-level SMCHBI is developed for solar powered industrial drive system and their performance is validated. The proposed system enhances the utilization of CMLI system for industrial applications.

## REFERENCES

- [1] AmuliuBogdanProca, and Ali Keyhani, "Identification of variable frequency induction motor models from operating data," *IEEE Trans. on Energy Conv.*, vol. 17, pp. 24-31, March 2002.

- [2] Alfredo Munoz-Garcia, Thomas A. Lipo, and Donald W. Novotny, "A New Induction Motor V/fControl Method Capable of High-Performance Regulation at Low Speeds," *IEEE Trans. Ind. Applicat.*, vol.34, pp. 813-821, July/Aug. 1998.

- [3] J. S. Lai and F. Z. Peng, "Multilevel converters-A new breed of power converters," *IEEE Trans. Ind. Applicat.*, vol. 32, pp. 509-517, May/June 1996.

- [4] G. Su, "Multilevel DC-link inverter," IEEE Trans. Ind. Appl., vol. 41, pp. 848-854, May/Jun. 2005.

- [5] Thomas M. Jahns, and Edward L. Owen, "AC Adjustable-Speed Drives at the Millennium: How Did We Get Here?," *IEEE Trans. Power Electron.*, vol. 16, pp. 17-25, Jan. 2001.

- [6] Akshay K. Rathore, Joachim Holtz, and Till Boller, "Generalized Optimal Pulse Width Modulation of Multilevel Inverters for Low-Switching-Frequency Control of Medium-Voltage High-Power Industrial AC Drives," *IEEE Trans. Ind. Electron.*, vol. 60, Oct. 2013.

- [7] Dong Jiang, Fei Wang, and Jing Xue, "PWM Impact on CM Noise and AC CM Choke for Variable-Speed Motor Drives PWM Impact on CM Noise and AC CM Choke for Variable-Speed Motor Drives," *IEEE Trans. Ind. Applicat.*, vol. 49, Mar./April 2013.

- [8] J. Rodriguez, B.Wu, S. Bernet, J. Pontt, and S. Kouro, "Multilevel voltage source converter topologies for industrial medium voltage drives," *IEEE Trans. Ind. Electron.*, vol. 54, Dec. 2007.

- [9] Jeffrey Ewanchuk, John Salmon, and Andrew M. Knight "Performance of a High-Speed Motor Drive System Using a Novel Multilevel Inverter Topology," *IEEE Trans. Ind. Applicat.*, vol. 45, Sept./Oct. 2009.

- [10] E. Babaei "A Cascade Multilevel Converter Topology with Reduced Number of Switches," IEEE Trans. Power Electron., vol. 23, Nov. 2008.

414 🗖 ISSN: 2088-8694

[11] Li Li, DariuszCzarkowski, Yaguang Liu, and PragasenPillay, "Multilevel Selective Harmonic Elimination PWM Technique in Series-Connected Voltage Inverters," *IEEE Trans. Ind. Applicat.*, vol. 45, Jan./Feb. 2000, pp. 160-170.

- [12] M.V. Subramanyam, P.V.N. Prasad, G. Poornachandra Rao1, "Fuzzy Logic Closed Loop Control of 5-level MLI Driven Three phase Induction motor," *International Journal of Power Electronics and Drive System*, vol. 3, June 2013.

- [13] FaridKhoucha, MounaSoumiaLagoun, AbdelazizKheloui, and Mohamed El HachemiBenbouzid, "A Comparison of Symmetrical and Asymmetrical Three-Phase H-Bridge Multilevel Inverter for DTC Induction Motor Drives," *IEEE Trans. on Energy Conv.*, vol. 26, pp. 64-72, March 2011.

- [14] FaridKhoucha, SoumiaMounaLagoun, KhoudirMarouani, AbdelazizKheloui, and Mohamed El HachemiBenbouzid, "Hybrid Cascaded H-Bridge Multilevel-Inverter Induction-Motor-Drive Direct Torque Control for Automotive Applications," *IEEE Trans. Ind. Electron.*, vol. 57, pp. 892-899, March 2010.

- [15] Samir Kouro, Mariusz Malinowski, K. Gopakumar, JosepPou, Leopoldo G. Franquelo, BinWu, Jose Rodriguez, Marcelo A. Perez, and Jose I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, pp. 2553-2580, Aug. 2010.

- [16] Bhim Singh, Brij N. Singh, Ambrish Chandra, Kamal Al-Haddad, AshishPandey, and Dwarka P. Kothari, "A Review of Single-Phase Improved Power Quality AC-DC Converters," *IEEE Trans. Ind. Electron.*, vol. 50, pp. 962-981, Oct. 2003.

- [17] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium voltage multilevel converters—State of the art, challenges and requirements in industrial applications," *IEEE Trans. Ind. Electron.*, vol. 57, Aug. 2010.

- [18] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo, M. A. M. Prats, and M. A. Perez, "Multilevel converters: An enabling technology for high-power applications," Proc. IEEE, vol. 97, Nov. 2009.

- [19] S. Rohner, S. Bernet, M. Hiller, and R. Sommer, "Modulation, losses, and semiconductor requirements of modular multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, pp. 2633–2642. Aug. 2010.

- [20] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol. 2, June. 2008.

#### **BIOGRAPHIES OF AUTHORS**

**R.** Uthirasamy received the B.E. degree in Electrical and Electronics Engineering from Sengunthar Engineering College, in 2005, the M.E. degree in Power Electronics and Drives from Government College of Engineering Salem in 2007. Currently he is working as Assistant Professor in EEE department, Jansons Institute of Technology, Coimbatore. He has published 10 papers in International Journals, National and International Conferences. His research is in the field of Power Converters, Soft Switching Techniques.

**U.S. Ragupathy** received the B.E. degree in Electrical and Electronics Engineering in 1999 from University of Madras, the M.E. degree in Applied Electronics from Anna University Chennai in 2004 and Ph.D. in the area of medical image processing from Anna University Chennai in 2011. At present he is working as Professor/Head in EIE Department at Kongu Engineering College, Perundurai. His areas of academic interest include Digital Image Processing, VLSI Signal Processing, Wavelets and Soft Computing Techniques. He has published 35 papers in International Journals, National and International Conferences.

**R.** Naveen received the B.E. degree in Electrical and Electronics Engineering from St.Joseph's College of Engineering, in 2013. Currently he is pursuing his M.E. degree in Power Electronics and Drives, Jansons Institute of Technology, Coimbatore.